Understanding the Cell Microprocessor

by Anand Lal Shimpi on March 17, 2005 12:05 AM EST- Posted in

- CPUs

Cell’s Dynamic Logic

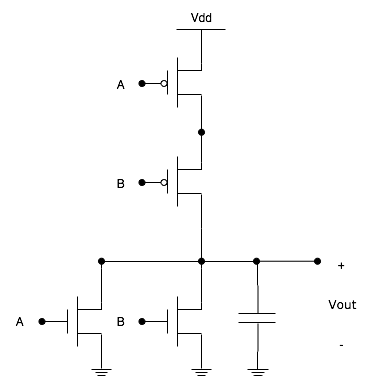

Although it’s beyond the scope of this article, one of the major problems with static CMOS circuits are the p-type transistors, and the fact that for every n-type transistor, you also must use a p-type transistor.There is an alternative known as dynamic or pseudo-NMOS logic, which gets around the problems of static CMOS while achieving the same functionality. Let’s take a look at that static CMOS NOR gate again:

Thus, the NOR gate outputs a 1 only if all inputs are 0, which is exactly how a NOR gate should function.

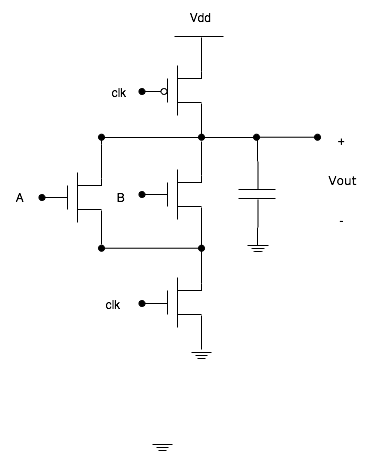

Now, let’s take a look at a pseudo-NMOS implementation of the same NOR gate:

Cell’s implementation goes one step further. The p-type transistor at the top of the circuit and the n-type transistor at the bottom are clocked on non-overlapping phases, meaning that the two clocks aren’t high/low at the same time.

The way in which the gate here works is as follows: inputs are first applied to the logic in between the clock fed transistors. The top transistor’s gate is closed allowing the logic transistors to charge up. The gate is then opened and the lower transistor’s gate is closed to drain the logic transistors to ground. The charge that remains is the output of the circuit.

What’s important about this is that since power is only consumed during two non-overlapping phases, overall power consumption is lower than static CMOS. The downside is that clock signal routing becomes much more difficult.

The other benefit is lower transistor count. In the example of the 2-input NOR gate, our static CMOS design used 4 transistors, while our pseudo-NMOS implementation used 4 transistors as well. But for a 3-input NOR gate, the static CMOS implementation requires 6 transistors, while the pseudo-NMOS implementation requires 5. The reasoning is that for a CMOS circuit, you have 1 p-type transistor for every n-type, while in a pseudo-NMOS circuit you only have two additional transistors beyond the bare minimum required to implement the logic function. For a 100-input NOR gate (unrealistic, but a good example), a static CMOS implementation would require 200 transistors, while a pseudo-NMOS implementation would only require 102.

By making more efficient use of transistors and lowering power consumption, Cell’s pseudo-NMOS logic design enables higher clock frequencies. The added cost is in the manufacturing and design stages:

- As we mentioned before, clock routing becomes increasingly difficult with pseudo-NMOS designs similar to that used in Cell. The clock trees required for Cell are probably fairly complex, but given IBM’s expertise in the field, it’s not an insurmountable problem.

- Designing pseudo-NMOS logic isn’t easy, and there are no widely available libraries from which to pull circuit designs. Once again, given IBM’s size and expertise, this isn’t much of an issue, but it does act as a barrier for entry of smaller chip manufacturers.

- Manufacturing such high speed dynamic logic circuits often requires techniques like SOI, but once again, not a problem for IBM given that they have been working on SOI for quite some time now. There’s no surprise that Cell is manufactured on a 90nm SOI process.

70 Comments

View All Comments

ceefka - Thursday, March 17, 2005 - link

Rambus'RevengeLocut0s - Thursday, March 17, 2005 - link

Great article Anand!! Yeah I actually get to bring my Comp150 knowledge to bear in reading this article! If this had come out 6 months ago I would have been totally lost. It will indeed be interesting to see what headway Cell can make, however unfortunately as Anand alludes to the x86 architecture is just too heavily entrenched for anything to budge it except the Big 2 (AMD and Intel). I can't wait to see what type of power the Playstation 3 will have though, and especially how that power will be utilized in games. I bet there will be some jaw dropping graphics awaiting us there. That is if Cells limitations don't hold back lazy game developers and lead to a string of mediocre games punctuated by a few amazing titles made by independent developers who really care to utilize the architecture. Didn't the Playstantion 1 suffer something similar?knitecrow - Thursday, March 17, 2005 - link

The real world technology article on the cell, states that it gives up single thread performance in favour of runing many parallel threads. That sounds like a terrible difficult processor to development games for.I for one think it will be easier to put the burden on the hardware rather than on the software side.

Can we see another repeat of PS2? Technically impressive, but hard to code for.

JarredWalton - Thursday, March 17, 2005 - link

11 - I think the point is that games tend to use certain functions of a CPU much more frequently, while general business/office applications make use of a wider range of generic operations. I understand your complaint, as office applications generally don't need a lot more power than about 1.5 GHz at most. However, the key of the statement was the "general purpose microprocessor" and not the "very powerful" part.AnandThenMan - Thursday, March 17, 2005 - link

WAIT. What the flock does this mean?"Performance in business/office applications requires a very powerful, very fast general purpose microprocessor, but performance in a game console, for example, does not."

WHAT??????? Hello?? So an office app like Word needs a very powerful processor, but a game console does not? I beg to differ. I suppose it depends on how you define "business/office application" but I think that statement is WAY off. I know several current office applications that will limp along on a pentium 133, but no current game has any hope on the same CPU.

tipoo - Wednesday, July 30, 2014 - link

It was clear to me that meant console CPUs didn't have to be as general purpose and brute force powerful in every regard - they can get away with being more specialized, and suck at general work, but still fast for game specific code.Googer - Thursday, March 17, 2005 - link

When are they coming out? Anyone know of a release date?jeffbui - Thursday, March 17, 2005 - link

#4, I do. Heh.I've been waiting for this article forever.. thanks!

JarredWalton - Thursday, March 17, 2005 - link

Interesting stuff. The Playstation has always been something of a pain in the rear to program. PS1 went it's own way, and PS2 did the same. PS3 and Cell seem ready to pave new roads into the "OMG this is really complex" land of programming. I'm glad I've given up serious programming.... :)Googer - Thursday, March 17, 2005 - link

In soviet russia cell processor controls your mind.