Arm Announces Neoverse N1 & E1 Platforms & CPUs: Enabling A Huge Jump In Infrastructure Performance

by Andrei Frumusanu on February 20, 2019 9:00 AM ESTE1 Implementation & Performance Targets

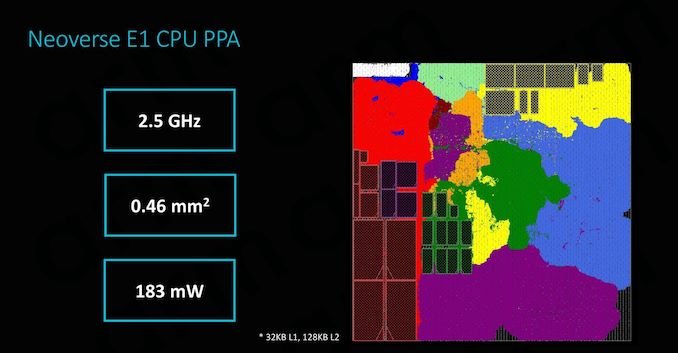

The Neoverse E1 CPU being a small CPU core aimed at cost-effective and dense implementation naturally needs to be quite small, as well as power efficient.

Implemented on a 7nm process, Arm physical design team is able to get an E1 CPU core with 32KB L1 and 128KB L2 cache down to 0.46mm² - all while reaching a high clock of 2.5GHz and a power consumption of 183mW. The higher clock was a surprise as it is quite notably higher than what we’ve seen vendors achieve on the A55 – although we are talking about different implementation targets.

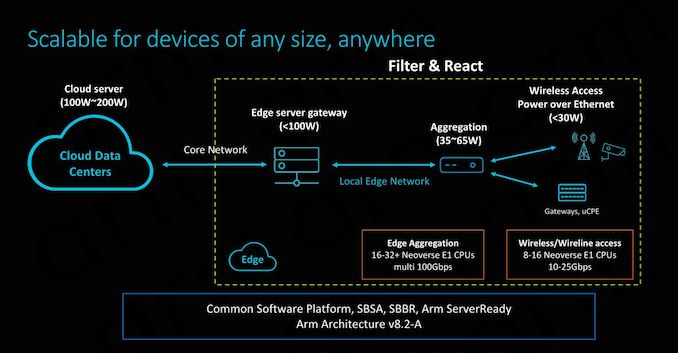

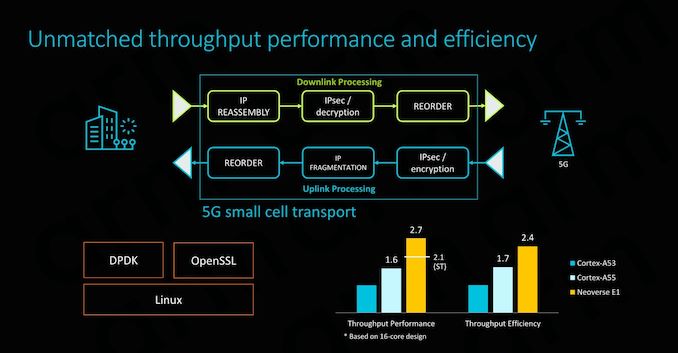

Arm envisions the most popular implementations of the E1 to be found in lower power edge applications. At the lower end, ranging from 8-16 cores would be a good for wireless access points and gateways, delivering data throughputs in the 10-25Gbps rang. A tier up we would see 16-32 core designs in use-cases such as edge data aggregation deployments, achieving data rates in the 100’s of Gbps.

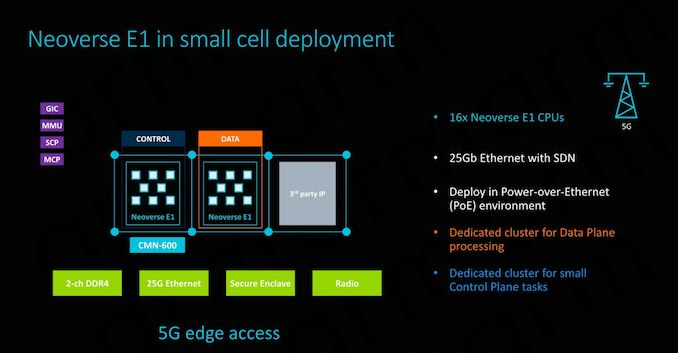

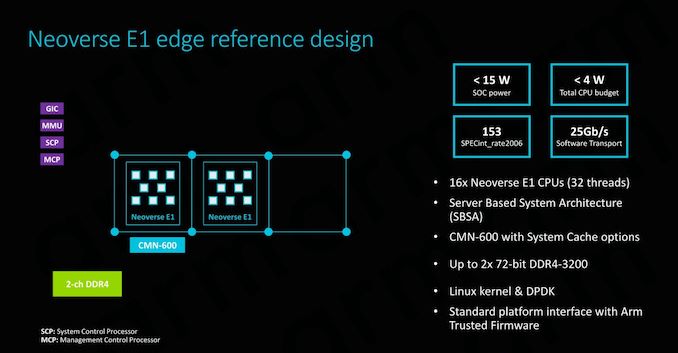

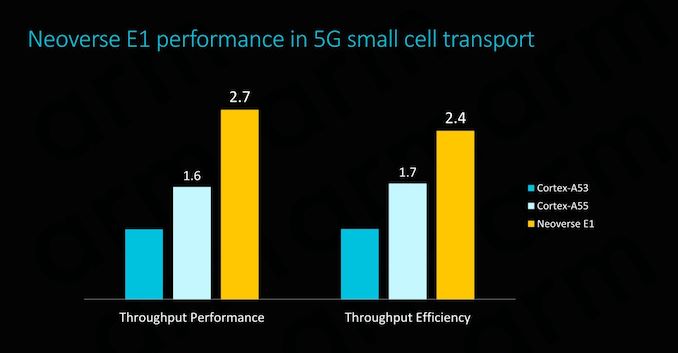

The Neoverse E1 reference design that Arm offers and sees as being the most popular “sweet-spot” is based on a 16 core design. Here we have to clusters of 8 cores in a small CMN-600 2x4 mesh network, allowing for system cache options as well as integration of possible additional third-part IP. The envisioned memory system would be a 2-ch DDR4 configuration.

Such as SoC would have a power consumption of less than 15W, of which less than 4W would actually be used by the CPU cores. SPECint2006 rate scores would come in at 153 – which given the actual size and power consumption of the platform is quite impressive. The system would also be capable of 25Gb/s network throughput, enabled solely by a software transport layer (Meaning no hardware acceleration).

On a per-core comparison to the Cortex A53 and A55, the new E1 CPU would again offer significant throughput performance benefits, but also very importantly it would represent an efficiency boost compared to its predecessors (ISO process comparison).

101 Comments

View All Comments

platinumjsi - Thursday, February 21, 2019 - link

Wouldnt mind seeing an Anadtech article detailing the differences between X86 and Arm and explaining the benefits and downsides of each architecture.Looking at this if ARM can do 64 cores for 105w I have to wonder why it takes AMD 250w on the same process?

Intel / AMD should be seriously worried about this.

Could we see ARM-based Laptops / Desktops? Wouldnt be any good for gaming as I cant see devs recompiling there back cataloge for ARM but for Office use these seem ideal.

SarahKerrigan - Thursday, February 21, 2019 - link

ARM laptops already exist, running Windows. Look at the Asus NovaGo or the Lenovo Yoga C630.edzieba - Thursday, February 21, 2019 - link

ARM still has to overcome the same issue that killed off every other HPC architecture (barring POWER just about hanging in there): not being x86 ( http://3s81si1s5ygj3mzby34dq6qf-wpengine.netdna-ss... ).Antony Newman - Thursday, February 21, 2019 - link

Perhaps this will all change when Apple move over to an ARM ISA? Apple would have to offer a system that is at least as capable as x86 with a significantly lower lower TCO. I think the limitation up until know was the wimpiness of the ARM offerings; the offerings were cheap but not performant.javadesigner - Friday, February 22, 2019 - link

What does the "A" in ARM stand for ? I always thought it was Apple. Does Apple make any licensing money when Samsung makes an (A)pple(R)(M) chip ?TobiWahn_Kenobi - Saturday, February 23, 2019 - link

Acorn RISC MachinesTobiWahn_Kenobi - Saturday, February 23, 2019 - link

Nowadays Advances RISC Machines.darkich - Sunday, February 24, 2019 - link

.. Isn't this basically (as expected) an expansion of the Cortex A76 architecture?techbug - Sunday, June 9, 2019 - link

intel w-3175x's rate score doesn't look right. Its single-thread score is 48.18 and 56T is 729.82. So each thread only contributes only 729.82/56=13.03, which seems to be too low.obi210 - Sunday, February 2, 2020 - link

A Neoverse E1 derivative, without SMT, could be the next gen Arm little core. Such a core with Armv9 support could provide near A73 performance. In-order A53 derivatives should not be carried over to next gen.