Intel to Discontinue Itanium 9700 ‘Kittson’ Processor, the Last of the Itaniums

by Anton Shilov on January 31, 2019 6:30 PM EST

Intel on Thursday notified its partners and customers that it would be discontinuing its Itanium 9700-series (codenamed Kittson) processors, the last Itanium chips on the market. Under their product discontinuance plan, Intel will cease shipments of Itanium CPUs in mid-2021, or a bit over two years from now. The impact to hardware vendors should be minimal – at this point HP Enterprise is the only company still buying the chips – but it nonetheless marks the end of an era for Intel and their interesting experiment into a non-x86 VLIW-style architecture.

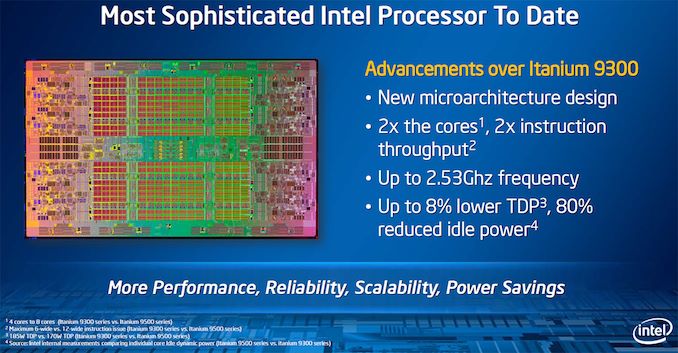

The current-generation octa and quad-core Itanium 9700-series processors were introduced by Intel in 2017, in the process becoming the final processors based on the IA-64 ISA. Kittson for its part was a clockspeed-enhanced version of the Itanium 9500-series ‘Poulson’ microarchitecture launched in 2012, and featured a 12 instructions per cycle issue width, 4-way Hyper-Threading, and multiple RAS capabilities not found on Xeon processors back then. It goes without saying that the writing has been on the wall for Itanium for a while now, and Intel has been preparing for an orderly wind-down for quite some time.

At this point, the only systems that actually use Itanium 9700-series CPUs are the HPE Integrity Superdome machines, which are running the HP-UX 11i v3 operating system and launched in mid-2017. So Intel's sole Itanium customer will have to submit their final Itanium orders – as well as orders for Intel’s C112/C114 scalable memory buffers – by January 30, 2020. Intel will then ship its last Itanium CPUs by July 29, 2021. HPE for its part will support their systems through at least December 31, 2025, but depending on how much stock HPE wants to keep on hand, they'll presumably stop selling them a few years sooner than that.

With the EOL plan for the Itanium 9700-series CPUs in place, it certainly means that this is the end of the road for the whole Itanium project, both for HPE and Intel. The former has been offering Xeon-based NonStop and Integrity servers for years now, whereas the latter effectively ceased development of new CPUs featuring the IA-64 ISA earlier this decade. The machines running these CPUs will of course continue their operations through at least late 2025 (or until HPE drops HP-UX 11i v3) simply because mission-critical systems are bought for the long-haul, but Intel will cease shipments of Itaniums in 2.5 years from now.

Related Reading:

- Intel to Discontinue Itanium 9500 ‘Poulson’ CPUs

- Intel’s Itanium Takes One Last Breath: Itanium 9700 Series CPUs Released

- Intel to Release New Itanium CPUs in 2012: New Architecture and Up to Eight Cores

Source: Intel

63 Comments

View All Comments

mode_13h - Sunday, February 3, 2019 - link

PowerPC ran Linux for a long time - odd that you'd assume UNIX people would all go to Apple. Also, you forgot about SPARC and MIPS.HStewart - Friday, February 1, 2019 - link

One thing this does not mean Itanium is gone, Intel still has 9700 series but with Microsoft dropping support in Windows it is pretty much end of life. I don't see why someone needs one when they can get Xeons.SarahKerrigan - Friday, February 1, 2019 - link

It does mean Itanium is gone. That's what this article is about. In a year, no more 9700 orders.And until Xeon can run the full set of Itanium operating systems, this affects customers. NSK has been ported; VMS and GCOS 8 have announced ports, but neither are shipping on Xeon today AFAICT; HP-UX, likely the largest installed base of all of them, has no announced port, just a vague "we'll provide some kind of migration path to Linux."

UtilityMax - Friday, May 24, 2019 - link

Microsoft support is irrelevant. The main customers for HP IA64 hardware are HPUX users. HP has no plan to port HPUX to x86-64 btw.rocky12345 - Friday, February 1, 2019 - link

It has been a very long time since I heard anything about the IA64 platform. Like other have said Intel probably hoped that at some point IA64 would be adopted into the desktop platform in some shape or form so they could become the main supplier of CPU's down the road. AMD released x64 before Intel was able to switch in some sort of IA64 onto the desktop market.My theory is if AMD was not able to get x64 out first and because Intel had locked down the IA64 to the point nobody could clone it like x86 that right now AMD would not be making CPU's or at least would be a much smaller player in the market. Just just look at what Intel did to Nvidia back in the day when they pulled Nvidia's chipset license which disallowed Nvidia from making any Intel based chipset and that was just from Nvidia's license running out and they could not get it renewed by Intel.

frenchy_2001 - Friday, February 1, 2019 - link

No intel did not pull nvidia's license, they changed their chipset interface, from the Front Side Bus (FSB), which had been licensed to many companies (SIS, VIA, ATI, Nvidia...) to QPI in the Core iX processors.Intel has not licensed QPI to anybody, which explains why there is no 3rd party chipset anymore.

NuclearArmament - Friday, February 1, 2019 - link

I hate AMD for killing this processor. It truly was the future of computing.HStewart - Friday, February 1, 2019 - link

It was not AMD that did - more likely advancements in Xeon's I am sure Intel is using some of advancements in Itanium to advance x86 processors especially Xeons. By way only 9300 is discontinued.SarahKerrigan - Friday, February 1, 2019 - link

Typical HStewart lies. The PCN Anandtech links to specifically lists the 9700 series as being discontinued.UtilityMax - Friday, May 24, 2019 - link

Nope. It was AMD that killed this by producing a 64-bit extension to x86 architecture. Originally, Intel had no intention for making Xeon or other x86 processor 64-bit. They were forced to do it only to respond to AMD. And at that point IA64 became a toast. Not only with pretty much ordinary performance, but also not binary compatible with x86.