CoWoS-L

TSMC is no stranger to building big chips. Besides the ~800mm2 reticle limit of their normal logic processes, the company already produces even larger chips by fitting multiple dies on to a single silicon interposer, using their chip-on-wafer-on-substrate (CoWoS) technology. But even with current-gen CoWoS allowing for interposers up to 3.3x TSMC's reticle limit, TSMC plans to build bigger still in response to projected demand from the HPC and AI industries. To that end, as part of the company's North American Technology Symposium last week, TSMC announced that they are developing the means of building super-sized interposers that can reach over 8x the reticle limit. TSMC's current-generation CoWoS technology allows for building interposers up to 2831 mm2 and the company is already seeing customers come...

TSMC Preps 6x Reticle Size Super Carrier Interposer for Extreme SiP Processors

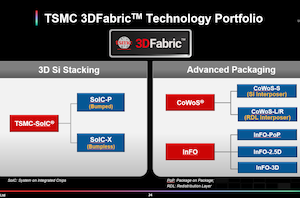

As part of their efforts to push the boundaries on the largest manufacturable chip sizes, Taiwan Semiconductor Manufacturing Co. is working on its new Chip-On-Wafer-On-Substrate-L (CoWoS-L) packaging technology that...

2 by Anton Shilov on 5/26/2023TSMC’s Version of EMIB is ‘LSI’: Currently in Pre-Qualification

Whilst process node technologies and Moore’s Law are slowing down, manufacturers and chip designers are looking to new creative solutions to further enable device and performance scaling. Advanced packaging...

19 by Andrei Frumusanu on 8/25/2020