AMD Zen Microarchitecture: Dual Schedulers, Micro-Op Cache and Memory Hierarchy Revealed

by Ian Cutress on August 18, 2016 9:00 AM ESTDeciphering the New Cache Hierarchy

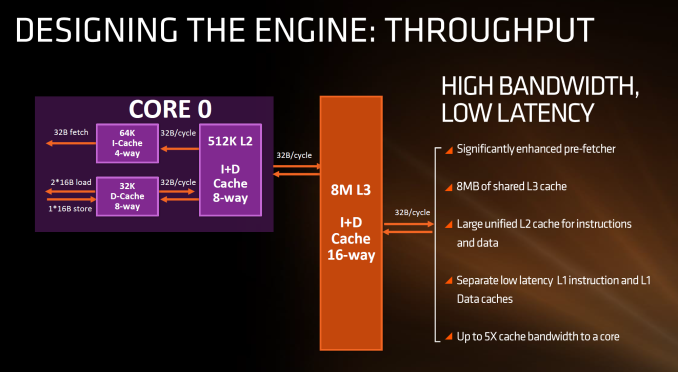

The cache hierarchy is a significant deviation from recent previous AMD designs, and most likely to its advantage. The L1 data cache is both double in size and increased in associativity compared to Bulldozer, as well as being write-back rather than write-through. It also uses an asymmetric load/store implementation, identifying that loads happen more often than stores in the critical paths of most work flows. The instruction cache is no longer shared between two cores as well as doubling in associativity, which should decrease the proportion of cache misses. AMD states that both the L1-D and L1-I are low latency, with details to come.

The L2 cache sits at half a megabyte per core with 8-way associativity, which is double that of Intel’s Skylake which has 256 KB/core and is only 4-way. On the other hand, Intel’s L3/LLC on their high-end Skylake SKUs is at 2 MB/core or 8 MB/CPU, whereas Zen will feature 1 MB/core and both are at 16-way associativity.

Edit 7:18am: Actually, the slide above is being slightly evasive in its description. It doesn't say how many cores the L3 cache is stretched over, or if there is a common LLC between all cores in the chip. However, we have recieved information from a source (which can't be confirmed via public AMD documents) that states that Zen will feature two sets of 8MB L3 cache between two groups of four cores each, giving 16 MB of L3 total. This would means 2 MB/core, but it also implies that there is no last-level unified cache in silicon across all cores, which Intel has. The reasons behind something like this is typically to do with modularity, and being able to scale a core design from low core counts to high core counts. But it would still leave a Zen core with the same L3 cache per core as Intel.

| Cache Levels | ||||

| Bulldozer FX-8150 |

Zen | Broadwell-E i7-6950X |

Skylake i7-6700K |

|

| L1 Instruction | 64 KB 2-way per module |

64 KB 4-way | 32 KB 8-way | 32 KB 8-way |

| L1 Data | 16 KB 4-way Write Through |

32 KB 8-way Write Back |

32 KB 8-way Write-Back |

32 KB 8-way Write-Back |

| L2 | 2 MB 16-way per module |

512 KB 8-way | 256 KB 8-way | 256 KB 4-way |

| L3 | 1 MB/core 64-way |

1 or 2 MB/core ? 16-way |

2.5 MB/core 16/20-way |

2 MB/core 16-way |

What this means, between the L2 and the L3, is that AMD is putting more lower level cache nearer the core than Intel, and as it is low level it becomes separate to each core which can potentially improve single thread performance. The downside of bigger and lower (but separate) caches is how each of the cores will perform snoop in each other’s large caches to ensure clean data is being passed around and that old data in L3 is not out-of-date. AMD’s big headline number overall is that Zen will offer up to 5x cache bandwidth to a core over previous designs.

216 Comments

View All Comments

Zingam - Thursday, August 18, 2016 - link

AMD realized finally that there is nothing better in the x86 world than copying Intel.tarqsharq - Thursday, August 18, 2016 - link

The same way Intel copied x86-64 from AMD? Or how AMD put out a superior dual core solution?Copying has gone both ways.

Stuka87 - Thursday, August 18, 2016 - link

Intel did not copy x86-64, they licensed it from AMD.Krysto - Thursday, August 18, 2016 - link

Which by the way is one of the reasons why the argument that "Intel would never allow AMD to be sold to another company" is so STUPID. If they do something like that and somehow retract their own licensing to AMD, let's see how well Intel does in the market without the 64-bit support licensed from AMD......That's why I believe AMD could easily sell itself to Qualcomm or Samsung if it wanted to. Intel may throw a hissy fit, but at the end of the day there's nothing they can do about it. Worst case scenario, whoever buys AMD, has to pay a little more for Intel's IP, but nothing that would break the company.

Kvaern1 - Thursday, August 18, 2016 - link

The licensing agreement is automatically terminated if either part goes through a change of control.Piraal - Thursday, August 18, 2016 - link

If intel wasn't licensed then it would be monopoly for AMD in no time, ever wonder why they licensed intel?Guess what intel licensed x86 to AMD before that for the same reason. It is funny how few people understand why AMD, and Intel before that 'had' to essentially give up something that would destroy their biggest competitor.

Morawka - Thursday, August 18, 2016 - link

IIRC if was part of a settlement between AMD and Intel that lead to the x64 getting licensed. i could be wrong thoSamus - Friday, August 19, 2016 - link

Actually the way I last read the licensing agreement worked is as long as AMD licenses x86, Intel has exclusive use of any AMD innovations in x86. That's how Intel essentially "licensed" x86-64 for free.It's like Mazda licensing a platform to Ford to build, and in return Mazda is allowed to monitor improvements to the platform to use on their own vehicles. This is commonly referred to as a joint venture technology agreement, and although AMD and Intel don't call it that, it's what it appears to be because the fine print of Intel licensing permits them to peak inside architectural improvements.

Note that this has nothing to do with the manufacturing end, unlike my Mazda>Ford analogy which is exclusively manufacturing based.

Anato - Saturday, August 20, 2016 - link

"Actually the way I last read the licensing agreement worked is as long as AMD licenses x86, Intel has exclusive use of any AMD innovations in x86. That's how Intel essentially "licensed" x86-64 for free."I doubt this, as this would mean that terminating AMD would terminate Intel x86-64 license. Think IBM, Samsung, Oracle or Apple buying AMD and stop making x86. Then Intel would not have x86-64 license anymore. So by paying 5-10B$ for AMD you could stop Intel's current 64 license which is >70% (?) of their revenue or use this as ransom.

Samus - Saturday, August 20, 2016 - link

All past-tense licensed innovation is grandfathered in upon a technology agreement termination. Legally. For instance, Mazda and Ford can use each others previous platforms indefinitely.