The Apple iPad Pro Review

by Ryan Smith, Joshua Ho & Brandon Chester on January 22, 2016 8:10 AM ESTSoC Analysis: On x86 vs ARMv8

Before we get to the benchmarks, I want to spend a bit of time talking about the impact of CPU architectures at a middle degree of technical depth. At a high level, there are a number of peripheral issues when it comes to comparing these two SoCs, such as the quality of their fixed-function blocks. But when you look at what consumes the vast majority of the power, it turns out that the CPU is competing with things like the modem/RF front-end and GPU.

x86-64 ISA registers

Probably the easiest place to start when we’re comparing things like Skylake and Twister is the ISA (instruction set architecture). This subject alone is probably worthy of an article, but the short version for those that aren't really familiar with this topic is that an ISA defines how a processor should behave in response to certain instructions, and how these instructions should be encoded. For example, if you were to add two integers together in the EAX and EDX registers, x86-32 dictates that this would be equivalent to 01d0 in hexadecimal. In response to this instruction, the CPU would add whatever value that was in the EDX register to the value in the EAX register and leave the result in the EDX register.

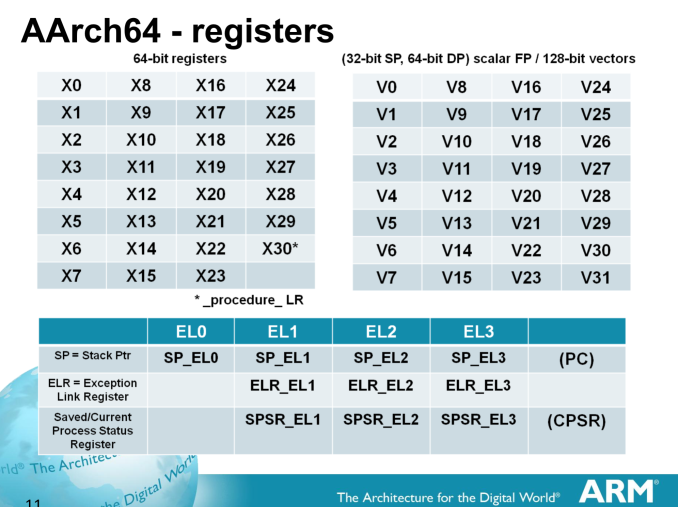

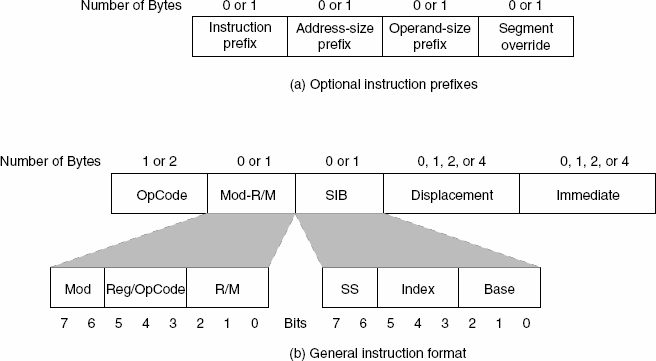

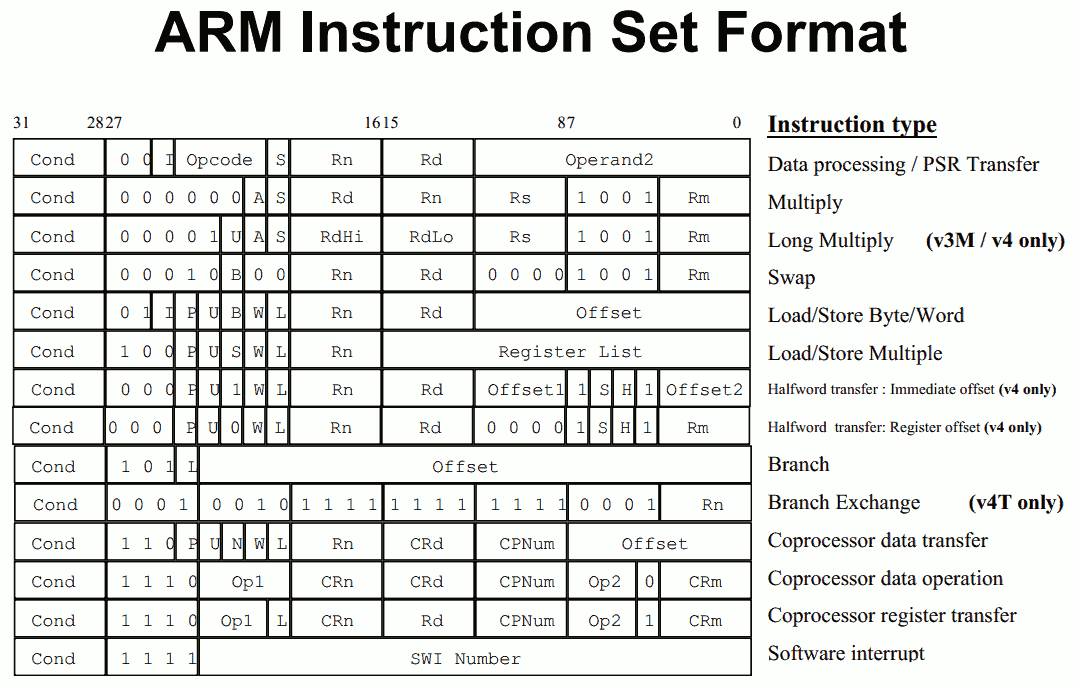

The fundamental difference between x86 and ARM is that x86 is a relatively complex ISA, while ARM is relatively simple by comparison. One key difference is that ARM dictates that every instruction is a fixed number of bits. In the case of ARMv8-A and ARMv7-A, all instructions are 32-bits long unless you're in thumb mode, which means that all instructions are 16-bit long, but the same sort of trade-offs that come from a fixed length instruction encoding still apply. Thumb-2 is a variable length ISA, so in some sense the same trade-offs apply. It’s important to make a distinction between instruction and data here, because even though AArch64 uses 32-bit instructions the register width is 64 bits, which is what determines things like how much memory can be addressed and the range of values that a single register can hold. By comparison, Intel’s x86 ISA has variable length instructions. In both x86-32 and x86-64/AMD64, each instruction can range anywhere from 8 to 120 bits long depending upon how the instruction is encoded.

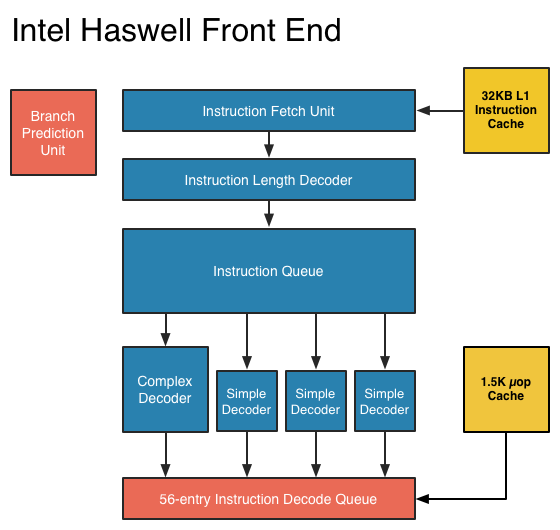

At this point, it might be evident that on the implementation side of things, a decoder for x86 instructions is going to be more complex. For a CPU implementing the ARM ISA, because the instructions are of a fixed length the decoder simply reads instructions 2 or 4 bytes at a time. On the other hand, a CPU implementing the x86 ISA would have to determine how many bytes to pull in at a time for an instruction based upon the preceding bytes.

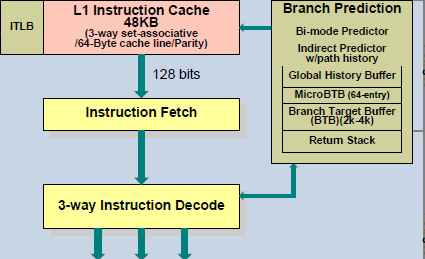

A57 Front-End Decode, Note the lack of uop cache

While it might sound like the x86 ISA is just clearly at a disadvantage here, it’s important to avoid oversimplifying the problem. Although the decoder of an ARM CPU already knows how many bytes it needs to pull in at a time, this inherently means that unless all 2 or 4 bytes of the instruction are used, each instruction contains wasted bits. While it may not seem like a big deal to “waste” a byte here and there, this can actually become a significant bottleneck in how quickly instructions can get from the L1 instruction cache to the front-end instruction decoder of the CPU. The major issue here is that due to RC delay in the metal wire interconnects of a chip, increasing the size of an instruction cache inherently increases the number of cycles that it takes for an instruction to get from the L1 cache to the instruction decoder on the CPU. If a cache doesn’t have the instruction that you need, it could take hundreds of cycles for it to arrive from main memory.

Of course, there are other issues worth considering. For example, in the case of x86, the instructions themselves can be incredibly complex. One of the simplest cases of this is just some cases of the add instruction, where you can have either a source or destination be in memory, although both source and destination cannot be in memory. An example of this might be addq (%rax,%rbx,2), %rdx, which could take 5 CPU cycles to happen in something like Skylake. Of course, pipelining and other tricks can make the throughput of such instructions much higher but that's another topic that can't be properly addressed within the scope of this article.

By comparison, the ARM ISA has no direct equivalent to this instruction. Looking at our example of an add instruction, ARM would require a load instruction before the add instruction. This has two notable implications. The first is that this once again is an advantage for an x86 CPU in terms of instruction density because fewer bits are needed to express a single instruction. The second is that for a “pure” CISC CPU you now have a barrier for a number of performance and power optimizations as any instruction dependent upon the result from the current instruction wouldn’t be able to be pipelined or executed in parallel.

The final issue here is that x86 just has an enormous number of instructions that have to be supported due to backwards compatibility. Part of the reason why x86 became so dominant in the market was that code compiled for the original Intel 8086 would work with any future x86 CPU, but the original 8086 didn’t even have memory protection. As a result, all x86 CPUs made today still have to start in real mode and support the original 16-bit registers and instructions, in addition to 32-bit and 64-bit registers and instructions. Of course, to run a program in 8086 mode is a non-trivial task, but even in the x86-64 ISA it isn't unusual to see instructions that are identical to the x86-32 equivalent. By comparison, ARMv8 is designed such that you can only execute ARMv7 or AArch32 code across exception boundaries, so practically programs are only going to run one type of code or the other.

Back in the 1980s up to the 1990s, this became one of the major reasons why RISC was rapidly becoming dominant as CISC ISAs like x86 ended up creating CPUs that generally used more power and die area for the same performance. However, today ISA is basically irrelevant to the discussion due to a number of factors. The first is that beginning with the Intel Pentium Pro and AMD K5, x86 CPUs were really RISC CPU cores with microcode or some other logic to translate x86 CPU instructions to the internal RISC CPU instructions. The second is that decoding of these instructions has been increasingly optimized around only a few instructions that are commonly used by compilers, which makes the x86 ISA practically less complex than what the standard might suggest. The final change here has been that ARM and other RISC ISAs have gotten increasingly complex as well, as it became necessary to enable instructions that support floating point math, SIMD operations, CPU virtualization, and cryptography. As a result, the RISC/CISC distinction is mostly irrelevant when it comes to discussions of power efficiency and performance as microarchitecture is really the main factor at play now.

408 Comments

View All Comments

FunBunny2 - Sunday, January 24, 2016 - link

-- Remember the original x86? What a horrendous, incompetently conceived turd!well. legend has it that IBM chose Intel over Motorola just because Intel a BK waiting to happen, thus easy to manipulate. Motorola, at that time with the 68K family, was the King Kong of microprocessors. or so the legend says.

Constructor - Sunday, January 24, 2016 - link

Wouldn't surprise me much. It's also said the priority at IBM was to just head off the emerging threat of companies like Apple (with the Apple II back then, whose construction the IBM PC closely copied) but absolutely not do anything to impact the then-dominant IBM mainframe business, so the IBM PC had to be relatively weak and limited.RafaelHerschel - Saturday, January 23, 2016 - link

A lot of companies use 8 year old PCs without any problems.For most professionals a big monitor and a full sized keyboard plus a mouse are the keys to productivity.

Constructor - Saturday, January 23, 2016 - link

To limited productivity in various cases where the only reason their workers even have to have and walk to a desk is that they don't have any mobile devices available which could serve the same purposes where the actual work is being done.That doesn't apply to every workplace, of course, but to quite a bunch of them.

FunBunny2 - Saturday, January 23, 2016 - link

-- Pretty much any computer is disposable in 4 years because the shelf life for hardware before it goes obsolete is about 3 years.yes. and no. yes, Intel keeps making ever more big chips with, arguably, faster cpu. most of the real estate for years has been used by non-cpu functions. even an i7 is really an SoC. Intel gets monopoly control of computing.

the reason pc sales have tanked in the last decade or so is simple: except for gearhead gamers, a Pentium does what most folks want to do good enough. it used to be that Windoze Next demanded the Intel Next processor just to run Word or Excel. not any more.

used to be: "the top 10 applications for the PC are spreadsheets, word processing, email..." still is.

Relic74 - Saturday, February 27, 2016 - link

Really, you have no problem moving files around in iOS, yeah, sorry but I don't believe you. I haven't met a single person, Dia hard Apple nuts as well that couldn't stand the lack of a decent file-management system. It's probably the worst I have ever seen on any OS. Everytime I download, edit and than upload to the cloud I create at least 4 copies if the same file. My system is littered with duplicates. File-managers in iOS do very little to alleviate this problem, it's just another place to hold more copies.MaxIT - Saturday, February 13, 2016 - link

When was last time you actually use an iDevice ? iOS 5 ?The whole argument about the file system is utterly ridiculous and outdated...

You can manage your files in a lot of different ways in iOS as of today.

Do you need a parallel port or a VGA exit on your tablet in 2016 ?

Sc0rp - Friday, January 22, 2016 - link

Well, as someone that uses an iPad Pro, I like the idea of taking my work wherever I go and not having to deal with the overhead that comes from a traditional OS.10101010 - Friday, January 22, 2016 - link

From what I see in my work, a lot of people think the same way. iOS is simple, reliable, consistent, and offers far less maintenance and security headaches compared to a traditional OS. The iPad Pro is showing up mostly in a "paper and pencil" replacement role, i.e. a role where a purpose-built tablet makes sense.Sure, files are clunky to access in iOS, but this also means that malicious apps can't get to your files. It's a compromise that many seem very willing to make vs. the near total lack of security in the Windows file system, for example.

Murloc - Saturday, January 23, 2016 - link

download OrCad Capture and try drawing a circuit with it.Now think about how you can do the same with a smaller touch screen and NO mouse (so big buttons are a no-no because fingers) at the same speed.

Can you fit the whole interface in the screen? If no, then component insertion is already slower than a PC, so a 10 years old school desktop computer wins, the tablet loses.

This software requires no computational power at all.