The IBM POWER8 Review: Challenging the Intel Xeon

by Johan De Gelas on November 6, 2015 8:00 AM EST- Posted in

- IT Computing

- CPUs

- Enterprise

- Enterprise CPUs

- IBM

- POWER

- POWER8

Database Performance: MySQL

Both MySQL and PostgreSQL do not scale well enough to make use of 72 threads (Dual Xeon E5), let alone 160 threads (Dual POWER8). We installed Percona MySQL Server 5.6, which is the most scalable InnoDB based MySQL server.

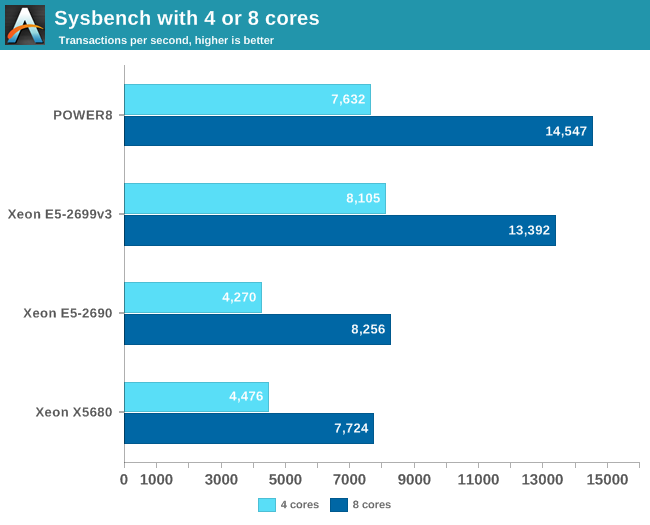

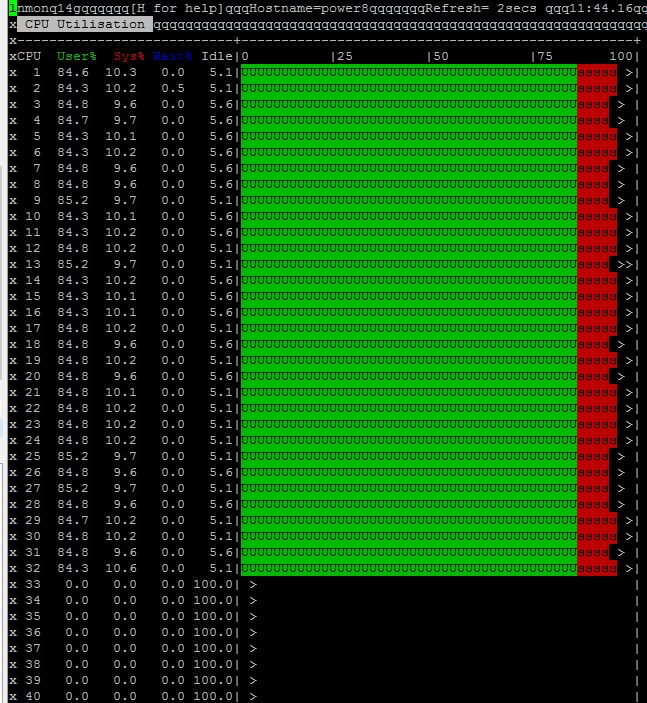

We used the MySQL Sysbench benchmark, but we limited MySQL with taskset to run on 4 or 8 physical cores. We verified that this was actually the case by running "nmon" on top of the IBM server.

You can clearly see that the first 32 threads are used (CPU 0 - 7).

Sysbench allows us to place an OLTP load on a MySQL test database, and you can chose the regular test or the read-only test. We chose read only as even with solid state storage, Sysbench is quickly disk I/O limited.

We tested with 10 million records and 100,000 requests. The main reason why we tested with Sysbench is to get a huge amount of queries that only select very small parts (a few or one row) of the tables, Sysbench allows you to test with any number of threads you like, but there is no "think time" feature. That means all queries fire off as quickly as possible, so you cannot simulate "light" and "medium" loads.

The response times are very small, which is typical for an OLTP test. To take them into account, we are showing you the highest throughput at around 3-4 ms. As the results tend to vary a bit, we give you the average of three runs.

With only 4 cores active, the Xeon E5-2699 v3 is still running at 3.3 GHz. Once we use 8 cores, the clockspeed lowers to 2.9 GHz, and the POWER8 outperforms the best Xeon by a small margin. However, we are only testing a part of the CPUs, similar to running only one VM. Ultimately what this means is that total performance will be:

- the POWER8 will be around 36k (14400/8 * 20 cores)

- the Xeon E5-2699 v3 will be around 60k (13400/8 * 36 cores)

- the Xeon E5-2695 v3 will be around 45k (13000/8 * 28 cores)

So the current MySQL performance on top of POWER8 is good, but MySQL runs still a lot better on the Xeons.

146 Comments

View All Comments

FunBunny2 - Friday, November 6, 2015 - link

"The z10 processor was co-developed with and shares many design traits with the POWER6 processor, such as fabrication technology, logic design, execution unit, floating-point units, bus technology (GX bus) and pipeline design style, i.e., a high frequency, low latency, deep (14 stages in the z10), in-order pipeline." from the Wiki.Yes, the z continues the CISC ISA from the 360 (well, sort of) rather than hardware RISC, but as Intel (amongst others) has demonstrated, CISC ISA doesn't have to be in hardware. In fact, the 360/30 (lowest tier) was wholly emulated, as was admitted then. Today, we'd say "micro-instructions". All those billions of transistors could have been used to implement X86 in hardware, but Intel went with emulation, sorry micro-ops.

What matters is the underlying fab tech. That's not going anywhere.

FunBunny2 - Friday, November 6, 2015 - link

^^ should have gone to KevinG!!Kevin G - Saturday, November 7, 2015 - link

The GX bus in the mainframes was indeed shared by POWER chips as that enabled system level component sharing (think chipsets).However, attributes like the execution unit and the pipeline depth are different between the POWER6 and z10. At a bird's eye view, they do look similar but the implementation is genuinely different.

Other features like SMT were introduced with the POWER5 but only the most recent z13 chip has 2 way SMT. Features like out-of-order execution, SMT, SIMD were once considered too exotic to validate in the mainframe market that needed absolute certainty in its hardware states. However, recent zArch chips have implemented these features, sometimes decades after being introduced in POWER.

The other thing is that IBM has been attempting to get get more and more of the zArch instruction set to be executed by hardware and no microcode. Roughly 75% to 80% of instructions are handled by microcode (there is a bit of a range here as some are conditional to use microcode).

JohanAnandtech - Saturday, November 7, 2015 - link

I believe that benchmark uses about 8 threads and not very well either? Secondly, it is probably very well optimized for SSE/AVX. So you can imagine that the POWER8 will not be very good at it, unless we manually optimize it for Altivec/VSX. And that is beyond my skills :-)UrQuan3 - Monday, December 21, 2015 - link

I'm sure no one is still reading this as I'm posting over a month later, but...I tested handbrake/x264 on a bunch of cross-platform builds including Raspberry Pi 2. I found it would take 24 RPi2s to match a single i5-4670K. That was a gcc compiled handbrake on Raspbian vs the heavily optimized DL copy for Windows. Not too bad really. Also, x264 seems to scale fairly well with the number of cores. Still, POWER8 unoptimized would be interesting, though not a fair test.

BTW, I'd encourage you to use a more standard Linux version than 6-month experimental little-endian version of Ubuntu. The slides you show advertise support for Ubuntu 14.04 LTS, not 15.04. For something this new, you may need the latest, but that is often not the case.

stun - Friday, November 6, 2015 - link

@Johan You might want to fix "the platform" hyperlink at the bottom of page 4. It is invalid.JohanAnandtech - Friday, November 6, 2015 - link

Thanks and fixed.Ahkorishaan - Friday, November 6, 2015 - link

Couldn't read past the graphic on page 1. It's 2015 IBM, time to use a font that doesn't look like a toddler's handwriting.xype - Sunday, November 8, 2015 - link

To be fair, it seems that the slide is meant for management types… :PJtaylor1986 - Friday, November 6, 2015 - link

Using decimals instead of commas to denote thousands is jarring to your North American readers.