The Intel 6th Gen Skylake Review: Core i7-6700K and i5-6600K Tested

by Ian Cutress on August 5, 2015 8:00 AM ESTThe Skylake CPU Architecture

As with any new Intel architecture, the devil is in the details. Previously at AnandTech we have been able to provide deep dives into what exactly is going on in the belly of the beast, although the launch of Skylake has posed a fair share of problems.

Nominally we rely on a certain amount of openness from the processor/SoC manufacturer in providing low level details that we can verify and/or explain. In the past, this information has typically been provided in advance of the launch by way of several meetings/consultations with discussions talking to the engineers. There are some things we can probe, but others are like a black box. The black box nature of some elements, such as Qualcomm’s Adreno graphics, means that it will remain a mystery until Pandora’s box is opened.

In the lead up to the launch of Intel’s Skylake platform, architecture details have been both thin on the ground and thin in the air, even when it comes down to fundamental details about the EU counts of the integrated graphics, or explanations regarding the change in processor naming scheme. In almost all circumstances, we’ve been told to wait until Intel’s Developer Forum in mid-August for the main reason that the launch today is not the full stack Skylake launch, which will take place later in the quarter. Both Ryan and I will be at IDF taking fastidious notes and asking questions for everyone, but at this point in time a good portion of our analysis comes from information provided by sources other than Intel, and while we trust it, we can't fully verify it as we normally would.

As a result, the details on the following few pages have been formed through investigation, discussion and collaboration outside the normal channels, and may be updated as more information is discovered or confirmed. Some of this information is mirrored in our other coverage in order to offer a complete picture in each article as well. After IDF we plan to put together a more detailed architecture piece as a fundamental block in analyzing our end results.

The CPU

As bad as it sounds, the best image of the underlying processor architecture is the block diagram:

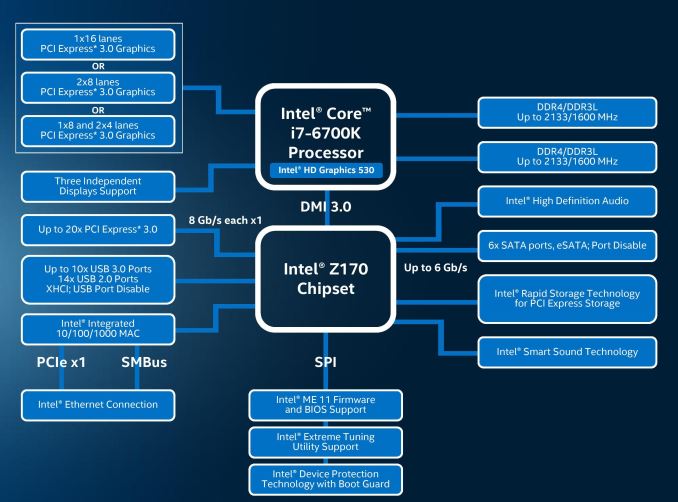

From a CPU connectivity standpoint, we discussed the DDR3L/DDR4 dual memory controller design on the previous page so we won’t go over it again here. On the PCI-Express Graphics allocation side, the Skylake processors will have sixteen PCIe 3.0 lanes to use for directly attached devices to the processor, similar to Intel's previous generation processors. These can be split into a single PCIe 3.0 x16, x8/x8 or x8/x4/x4 with basic motherboard design. (Note that this is different to early reports of Skylake having 20 PCIe 3.0 lanes for GPUs. It does not.)

With this, SLI will work up to x8/x8. If a motherboard supports x8/x4/x4 and a PCIe card is placed into that bottom slot, SLI will not work because only one GPU will have eight lanes. NVIDIA requires a minimum of PCIe x8 in order to enable SLI. Crossfire has no such limitation, which makes the possible configurations interesting. Below we discuss that the chipset has 20 (!) PCIe 3.0 lanes to use in five sets of four lanes, and these could be used for graphics cards as well. That means a motherboard can support x8/x8 from the CPU and PCIe 3.0 x4 from the chipset and end up with either dual-SLI or tri-CFX enabled when all the slots are populated.

DMI 3.0

The processor is connected to the chipset by the four-lane DMI 3.0 interface. The DMI 3.0 protocol is an upgrade over the previous generation which used DMI 2.0 – this upgrade boosts the speed from 5.0 GT/s (2GB/sec) to 8.0 GT/s (~3.93GB/sec), essentially upgrading DMI from PCIe 2 to PCIe 3, but requires the motherboard traces between the CPU and chipset to be shorter (7 inches rather than 8 inches) in order to maintain signal speed and integrity. This also allows one of the biggest upgrades to the system, chipset connectivity, as shown below in the HSIO section.

CPU Power Arrangements

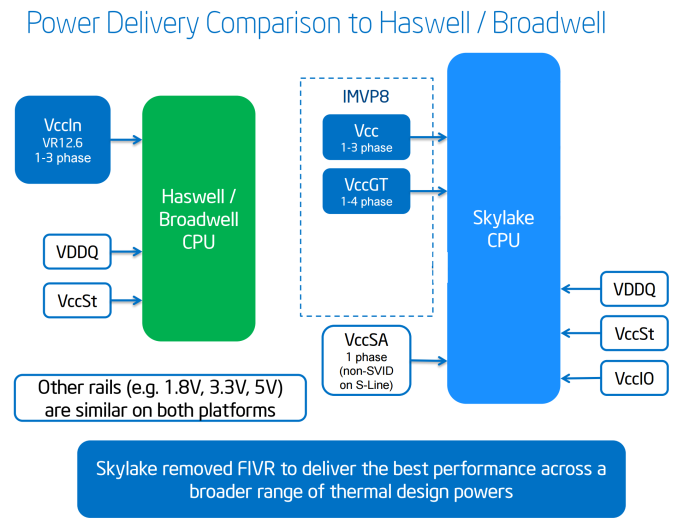

Moving on to power arrangements, with Skylake the situation changes as compared to Haswell. Prior to Haswell, voltage regulation was performed by the motherboard and the right voltages were then put into the processor. This was deemed inefficient for power consumption, and for the Haswell/Broadwell processors Intel decided to create a fully integrated voltage regulator (FIVR) in order to reduce motherboard cost and reduce power consumption. This had an unintended side-effect – while it was more efficient (good for mobile platforms), it also acted as a source of heat generation inside the CPU with high frequencies. As a result, overclocking was limited by temperatures and the quality of the FIVR led to a large variation in results. For Skylake on the desktop, the voltage regulation is moved back into the hands of the motherboard manufacturers. This should allow for cooler processors depending on how the silicon works, but it will result in slightly more expensive motherboards.

A slight indication of this will be that some motherboards will go back to having a large amount of multiplexed phases on the motherboard, and it will allow some manufacturers to use this as a differentiating point, although the usefulness of such a design is sometimes questionable.

477 Comments

View All Comments

AntDX316 - Thursday, November 12, 2015 - link

as my last greatest laptop was back in like 2007.. I had bad laptops ever since and when skylake had huge power saving options I decided to get an Alienware 17 R3 with 4k IGZO screen and 980mmikael.skytter - Wednesday, August 5, 2015 - link

Looking forward to read up :) Gonna be an awsome review - as always!Thanks!

Zponxie - Wednesday, August 5, 2015 - link

In the section "Skylake's Launch Chipset: Z170":

"In the previous Z97 chipset, there are a total of 18 Flex-IO ports that can flip between PCIe lanes, USB 3.0 ports or SATA 6 Gbps ports. For Z97, this moves up to 26 and can be used in a variety of configurations"

Was that last Z97 meant to be Z170?

Also, thank you for another quality review

Ryan Smith - Wednesday, August 5, 2015 - link

"Was that last Z97 meant to be Z170?"Indeed it was. Thank you for pointing it out.

ingwe - Wednesday, August 5, 2015 - link

Man I have been waiting for this! Pumped about DDR4.freaqiedude - Wednesday, August 5, 2015 - link

why? it basically has no performance impact whatsoever...and the powerbenefits are negligable, and it's more expensive...

I never understand why people buy premium RAM anymore, it simply has no impact on performance except for very very specialized benchmarking applications.

richardginn - Wednesday, August 5, 2015 - link

This CPU is a total joke.... Why Intel would make us pay over 300 bucks for a CPU and not put in GT4e graphics is a total fail.A5 - Wednesday, August 5, 2015 - link

Good integrated graphics are a waste here.richardginn - Wednesday, August 5, 2015 - link

A full on waste. If you are going to spend 300 bucks plus on a CPU you are going to spend at least 200 bucks on a GPU, BUTTT when you can throw in GT3e graphics in a broadwell i7-5775c CPU you must no bring us the pile of crap that is GT2 graphics for the 6700k CPU.8steve8 - Wednesday, August 5, 2015 - link

not true, i'd gladly pay for the best CPU, but have littler interest in buying a GPU that takes extra space and energy/heat.Not everyone who wants CPU performance is a hardcore gamer.