The Apple Watch Review

by Joshua Ho & Brandon Chester on July 20, 2015 8:00 AM EST- Posted in

- Wearables

- Apple

- Mobile

- Apple Watch

Apple S1 Analysis

One of the biggest issues with the smartwatch trend that I’ve seen is that as a result of most companies entering the market with smartphone backgrounds, we tend to see a lot of OEMs trying to shove smartphone parts into a smartwatch form factor. There have been a lot of different Android Wear watches, but for the most part everything seems to use Qualcomm’s Snapdragon 400 without the modem. Even though A7 is relatively low power for a smartphone, it’s probably closer to the edge of what is acceptable in terms of TDP for a smartwatch. Given that pretty much every Android Wear watch has around a 400 mAh battery at a 3.8 or 3.85 volt chemistry to attempt to reach 1-2 days of battery life and a relatively large PCB, the end result is that these smartwatches are really just too big for a significant segment of the market. In order to make a smartwatch that can scale down to sizes small enough to cover most of the market, it’s necessary to make an SoC specifically targeted at the smartwatch form factor.

Capped Apple S1 SoC (Image Courtesy iFixit)

The real question here is what Apple has done. As alluded to in the introduction, it turns out the answer is quite a bit. However, this SoC is basically a complete mystery. There’s really not much in the way of proper benchmarking tools or anything that can be run on the Watch to dig deeper here. Based on teardowns, this SoC is fabricated on Samsung’s 28nm LP process, although it’s not clear which flavor of LP is used. It’s pretty easy to eliminate the high power processes, so it’s really just a toss-up between HKMG and poly SiON gate structure. For those that are unfamiliar with what these terms mean, the main difference that results from this choice is a difference in power efficiency, as an HKMG process has less leakage power. Given how little cost is involved in this difference in process compared to a move to 20/14nm processes, it’s probably a safe bet that Apple is using an HKMG process here especially when we look at how the move from 28LP to 28HPm at TSMC dramatically affected battery life in the case of SoCs like Snapdragon 600 and 800.

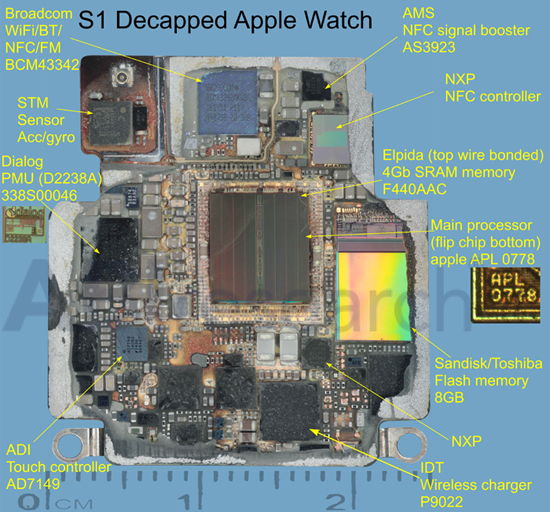

Decapped & Labeled S1 SoC (Image Courtesy ABI Research)

We also know that binaries compiled for the watch target ARMv7k. Unfortunately, this is effectively an undocumented ISA. We know that Watch OS is built on iOS/Darwin, so this means that a memory management unit (MMU) is necessary in order to make it possible to have memory protection and key abstractions like virtual memory. This rules out MCU ISAs like ARMv7m even if it's possible to add an MMU to such an architecture, so it’s likely that we’re looking at some derivative of ARMv7-A, possibly with some unnecessary instructions stripped out to try and improve power consumption.

The GPU isn’t nearly as much of a mystery here. Given that the PowerVR drivers present in the Apple Watch, it’s fairly conclusive that the S1 uses some kind of PowerVR Series 5 GPU. However which Series 5 GPU is up to debate. There are reasons to believe it may be a PowerVR SGX543MP1, however I suspect that it is in fact PowerVR's GX5300, a specialized wearables GPU from the same family as the SGX543 and would use a very similar driver. Most likely, dedicated competitive intelligence firms (e.g. Chipworks) know the answer, though it's admittedly also the kind of information we expect they would hold on to in order to sell it to clients as part of their day-to-day business activities.

In any case, given that native applications won’t arrive until WatchOS 2 is released I don’t think we’ll be able to really do much in the way of extensive digging on what’s going on here as I suspect that graphics benchmarks will be rare even with the launch of WatchOS 2.

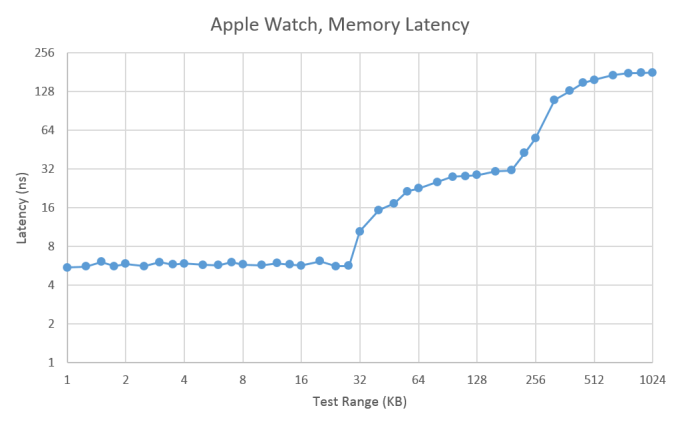

Meanwhile, after a lot of work and even more research, we're finally able to start shining a light on the CPU architecture in this first iteration of Apple's latest device. One of the first things we can start to look at is the memory hierarchy, which is information crucial to applications that require optimization to ensure that code has enough spatial and/or temporal locality to ensure that code is performant.

As one can see, there’s a pretty dramatic fall-off that happens between 28 and 64KB of “DRAM”, as we exit the local maximum of L1 data cache, so we can safely bet that the L1 data cache size is 32KB given current shipping products tend to fall somewhere between 32 and 64KB of L1 data cache. Given the dramatic fall-off that begins to happen around 224KB, we can also safely bet that we’re looking at a 256KB L2 combined cache which is fairly small compared to the 1-2MB shared cache that we might be used to from today’s large smartphone CPUs, but compared to something like an A5 or A7 it’s about right.

If Apple had just implemented the Cortex A7 as their CPU of choice, the obvious question at this point is whether they’ve really made anything “original” here. To try and dive deeper here, we can start looking past the memory hierarchy and looking closer at the machine itself. One of the first things that is obvious is that we’re looking at a CPU with a maximum frequency of 520 MHz, which is telling of the kind of maximum power that Apple is targeting here.

| Apple S1 CPU Latency and Throughput | ||||

| Instruction | Throughput (Cycles/Result) | Latency (Cycles/Result) | ||

| Loads (ldr reg,[reg]) | 1 | N/A | ||

| Stores (str reg,[reg]) | 1 | N/A | ||

| Move (mov reg, reg) | 1/2 | - | ||

| Integer Add (add reg, reg, imm8) | 1/2 | - | ||

| Integer Add (add reg,reg,reg) | 1 | 1 | ||

| Integer Multiply (mul reg,reg,reg) | 1 | 3 | ||

| Bitwise Shift (lsl reg,reg) | 1 | 2 | ||

| Float Add (vadd.f32 reg,reg,reg) | 1 | 4 | ||

| Double Add (vadd.f64 reg,reg,reg) | 1 | 4 | ||

| Float Multiply (vmul.f32 reg,reg,reg) | 1 | 4 | ||

| Double Multiply (vmul.f64 reg,reg,reg) | 4 | 7 | ||

| Double Divide (vdiv.f64 reg,reg,reg) | 29 | 32 | ||

Obviously, talking about the cache hierarchy isn’t enough, so let’s get into the actual architecture. On the integer side of things, integer add latency is a single cycle, but integer multiplication latency is three cycles. However, due to pipelining integer multiplication throughput can produce a result every clock cycle. Similarly, bitshifts take two cycles to complete, but the throughput can be once per clock. Attempting to interleave multiplies and adds results in only achieving half the throughput. We can guess that this is because the integer add block and the integer multiply block are the same block, but that doesn’t really make sense because of just how different addition and multiplication are at the logic level.

Integers are just half of the equation when it comes to data types. We may have Booleans, characters, strings, and varying bit sizes of integers, but when we need to represent decimal values we have to use floating point to enable a whole host of applications. In the case of low power CPUs like this one, floating point will also often be far slower than integers because the rules involved in doing floating point math is complex. At any rate, a float (32-bit) can be added with a throughput of one result per cycle, and a latency of four cycles. The same is true of adding a double or multiplying a float. However, multiplying or dividing doubles is definitely not a good idea here because peak throughput of multiplying doubles is one result per four clock cycles, with a latency of 7 clock cycles. Dividing doubles has a peak throughput of a result every 29 clock cycles, with a latency of 32 clock cycles.

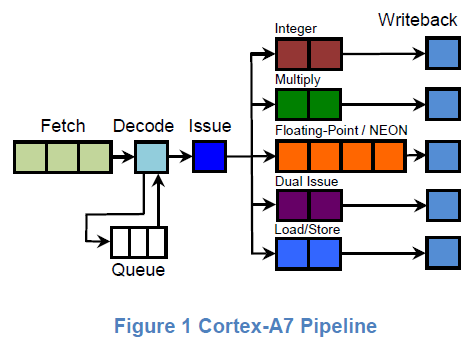

If you happen to have a webpage open with the latency and throughput timings for Cortex A7, you’d probably guess that this is a Cortex A7, and you’d probably be right as well. Attempting to do a load and a store together has a timing that indicates these are XOR operations which cannot be executed in a parallel manner. The same is true of multiplication and addition even though the two operations shouldn’t have any shared logic. Conveniently, the Cortex A7 has a two-wide pipeline that has similar limitations. Cortex A5 is purely single-issue, so despite some similarity it can't explain why addition with an immediate/constant value and a register can happen twice per clock.

Given the overwhelming amount of evidence at the timing level of all these instructions, it’s almost guaranteed that we’re looking at a single core Cortex A7 or a derivative of it at 520 MHz. Even if this is just a Cortex A7, targeting a far lower maximum clock speed means that logic design can prioritize power efficiency over performance. Standard cells can favor techniques and styles that would otherwise unacceptably compromise performance in a 2+ GHz chip could be easily used in a 520 MHz chip such as device stacking, sleepy stack layout, higher Vt selection with negative active body biasing, and other techniques that would allow for either lower voltage at the same frequency, or reduced capacitance in dynamic power and reduced static leakage. Given that Cortex A7 has generally been a winning design for perf/W metrics, I suspect that key points of differentiation will come from implementation rather than architecture for the near future. Although I was hoping to see Apple Watch on a more leading-edge process like 14LPP/16FF+, I suspect this will be deferred until Apple Watch 2 or 3.

270 Comments

View All Comments

cknobman - Tuesday, July 21, 2015 - link

Tell me what I was wrong about.In regards to it being a flop here are some links (from very recent articles) that prove outside of initial launch sales and preorders it is selling poorly:

http://www.cnet.com/news/apple-watch-sales-sluggis...

http://www.usatoday.com/story/tech/2015/07/20/appl...

http://techcrunch.com/2015/07/21/apple-watch-sales...

In regards to its features, please discredit my claims. It is big, its user interface sucks (not only in my limited use but the actual users who have it have explained to me why they think it sucks), it does not do squat without an iphone tethered to it, and it is expensive.

mrochester - Tuesday, July 21, 2015 - link

This is all speculation, not proof. We won't know anything official until/if Apple start announcing Watch sales separately from their 'other' category.thomasguide - Wednesday, July 22, 2015 - link

I hear that argument a lot from people and this is little Timmy's comments about that “We don’t intend to provide insight that could help our competitors,”Yet they seem to provide a lot of insight that could help their competitors by releasing iphone and ipad sales figures. Why is that? Is itbecause iphones are selling like hot cakes and it makes the company look good? They don't release watch numbers because sales have been dismal. Had they sold 20 million units, you bet your ass little Timmy would separate smartwatches into their own category rather than lumping them in with ipods. This way they can blame the lackluster sales on declining ipods instead the flopping watch.

Looks like all the fanboys bought their i-toy in April, now what Timmy?

S2k15 - Wednesday, July 29, 2015 - link

It's so sad that you need to disrespect Tim Cook by calling him "little Timmy" in order to make yourself feel better, as well as your no doubt empty life. So very sad.Oh, and ignore the fact that Apple announced that they would not break out Watch figures MONTHS ago, it's not a decision they made after they found out sales. Your entire argument is moot.

S2k15 - Wednesday, July 29, 2015 - link

Uh, Tim Cook stated as a fact that Watch sales were higher in May than April, and higher in June than May. Another rabid Apple hating lying troll caught in their lies. But this is the internet, so cowards like you will never admit they're wrong.hlovatt - Wednesday, July 22, 2015 - link

Apple announced today that the watch sales were over $1 billion. I guess it's going OK :)darwinosx - Monday, July 20, 2015 - link

Nobody but Apple knows what Apple watch sales have been like and you sure don't The Slice report has already been widely discredited.Battery life is not terrible at all further indication you have no idea what you are talking about.

Galps - Monday, July 20, 2015 - link

First off, sales haven't been announced so none of us really know how successful or not it really has been but the last estimates I heard put sales close to 3 million. In comparison, only about 720,000 smartwatches sold in 2014 total. So if more than tripling smartwatch sales in 3 months is a failure, then I need to start failing at things more like Apple. Second, design taste is completely opinion but I think I'll trust Vogue and Beyonce for fashion advice over some neck beard commenting on a tech article. Don't know what "owners" you've talked but anecdotal evidence is still anecdotal evidence. I could tell you about how all Android phones suck because me and my 4 friends each had a Galaxy S3 and our battery life was terrible and the UI was buggy and laggy. But that wouldn't matter because there are many other people who loved their S3s regardless of my anecdotal evidence to the contrary. In my opinion, I don't find the watch to be bulky or thick at all. To the contrary actually. I find it to be a lot smaller than most other smartwatches. Lastly, it will do plenty without the phone. You can go on a run and it will still track calories, time/pace, and heart rate. You can still use all the watch functions without the phone. When Watch OS 2 comes out, you'll be able to update all your apps via wifi independent of the phone. You can listen to music independent of the phone as well. Really the only thing you can't do without the phone is get notifications. And battery life is great. I have yet to make it through a whole day with less than 45% battery by the time I go to bed and my 6 Plus has been pushed to 3 days without a charge. Granted those are my experiences so I can't speak to everyone else's experience but I haven't had a single battery issue or any trouble getting my watch and phone to last me at least a day and half at minimum.Also, expensive is a relative term based off of your own income. I'm not trying to sound elitist (although this is going to sound really elitist so I'm sorry) but I have no issues spending $400 on a smartwatch. I have enough disposable income that spending a few hundred bucks on a watch isn't going to set me back in any significant amount what so ever. Maybe you have a hard time coming up with an extra $400 but some of us have money and don't really look at $400 as a large amount. Again, I know it sounds elitist and I'm not judging you if $400 is too much, I'm just trying to get the point across that a lot of people don't look at $400 as a lot of money.

navysandsquid - Monday, July 20, 2015 - link

her you need some lotion for your butthurt lol its ok pal we know you don't have any money you don't have to tell us. hate on brothername99 - Monday, July 20, 2015 - link

"Apple watch has been largely a market failure so far"What do you define as a market failure? Especially in a new market?

Apple have apparently sold around 4x as many watches as the entire Android Wear sales. That would seem to indicate a success.

They have apparently matched the internal Apple sales targets. Again indicates success.

Almost everyone who actually OWNS and has USED an Apple watch (as opposed to simply bitching about it) loves it. You see this both in reviews and in the most recent customer survey from Wristly research.

So where exactly is this failure you speak of?