Plextor M6S & M6M (256GB) Review

by Kristian Vättö on April 10, 2014 6:00 AM ESTThe Math of Marketing: Not All 19nm NAND Is the Same

Almost a year ago, Toshiba/SanDisk announced their second generation 19nm NAND. It's typical for NAND manufacturers to use the same process node for more than one generation because manufacturers can cut the die size by increasing either the page, block, or die capacity (or even all three at once), which will lead to lower production costs. However, Toshiba/SanDisk had already upped the page size to 16KB and the die capacity remained at 64Gbit, so how did they manage to decrease the die size by 17%? We'll need to dig a little deeper into the die to find that out but first (no, I'm not gonna take a selfie) let's quickly revise how NAND works.

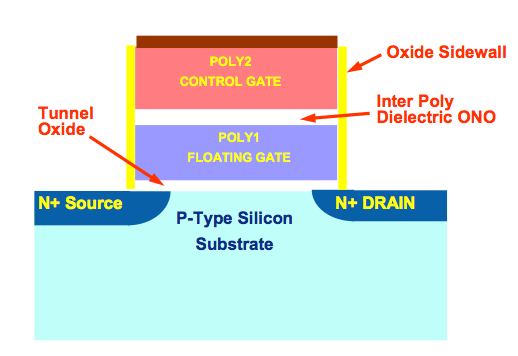

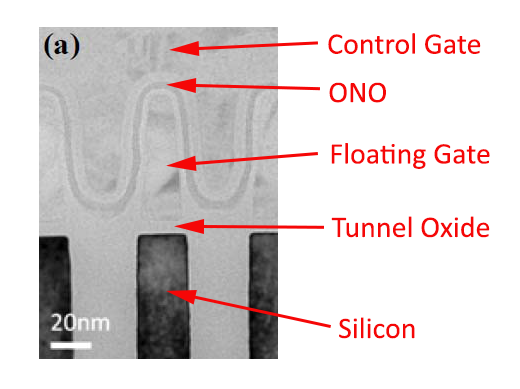

That is what a cross-section of a NAND cell looks like when it's turned into nice colorful graph. This is what it looks like in practice:

Not as nice as the graph above, right? The reason we need the cross-section photo is because the graph is a bit too simplified and doesn't show one crucial thing: the control gate isn't something that just sits on top of the floating gate and the inter poly dielectric - it actually wraps around the whole floating gate. That's to keep the capacitance between the control and floating gates as high as possible, which in turn helps to maintain the charge in the floating gate and increase performance (the math behind this is actually more simple than you would expect but I'm not going to scare people off with a bunch of equations here). B ut that is just one cell. To truly understand the structure of NAND, we need to zoom out a bit.

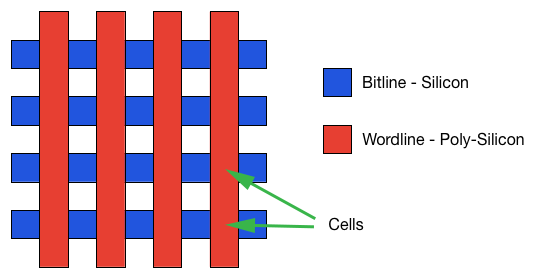

That is what a bunch of NAND cells look like from above. The bitlines (i.e. silicon in the cross-section photo above) are made of silicon and on top of them are the wordlines that are also known as control gates. At every intersection of a bitline and wordline, there is one cell capable of holding one (SLC), two (MLC) or three (TLC) bits of data.

Traditionally cells are symmetrical. The process node refers to the size of one cell, so in the case of 20nm NAND, the cell size would be 20nm x 20nm. However, there is no rule against making an asymmetrical cell and that is in fact what Toshiba/SanDisk did with their first generation 19nm NAND. Instead of being a symmetrical 19nm x 19nm design, the cell size was 19nm x 26nm. Compared to IMFT's symmetrical 20nm design, the actual cell size is quite a bit larger (494 nm2 vs 400 nm2 ), yet in terms of marketing Toshiba's/SanDisk's "19nm" NAND was smaller and more advanced.

You could call that cheating but there is a good technical reason as to why building an asymmetrical design makes sense. As I mentioned earlier, the wordline (control gate) wraps around every floating gate and between them is an insulating inter poly dielectric (often referred to as ONO due to its oxide-nitride-oxide structure, or just IPD). Since the floating gate is where the electrons are stored, it needs to be insulated; otherwise the electrons could easily escape the floating gate and you would have a brick that can't reliably hold data.

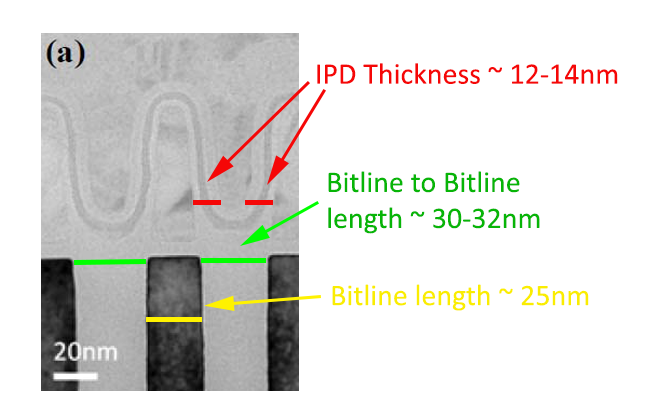

The inter poly dielectric (IPD) is the tricky part here -- because it wraps around every floating gate, the minimum distance between two floating gates (and hence bitlines) must be at least twice the thickness of the IPD. Scaling the IPD is difficult because if you make it too thin, the cell becomes vulnerable to leakage because the IPD won't be able to reliably insulate the floating gate. Generally it's considered impossible to scale the IPD below 10nm, so 26nm is already pretty good and 20nm is hitting the limits.

IMFT's approach is different. It's a high-k metal gate design and the wordline no longer needs to be wrapped around the floating gate, but I'm not going to go into more detail about that here. The short summary is that it allows for a symmetrical 20nm design without sacrificing reliability.

Courtesy of EETimes.com

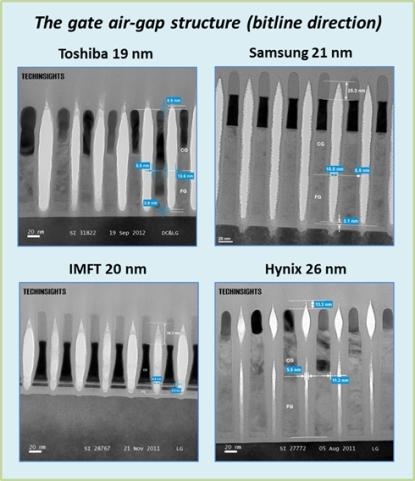

In addition, you will want to have some conducting poly-silicon (i.e. wordline/control gate) between every bitline as well to build up capacitance, so in reality it's much harder scale the bitline length compared to the wordline. There is no wrapping issue with wordlines and the only thing you really have to take into account is wordline to wordline interference. To battle that, all NAND manufacturers are currently using tiny air gaps between every wordline to reduce the interference and still be able to scale down the NAND.

| IMFT (Intel/Micron) | Toshiba/SanDisk | |||

| NAND Process | 20nm 64Gbit | 20nm 128Gbit | 19nm 64Gbit (1st gen) | A19nm 64Gbit (2nd gen) |

| Cell Size | 20nm x 20nm | 19nm x 26nm | 19nm x 19.5nm | |

| Die Size | 118mm2 | 202mm2 | 113mm2 | 94mm2 |

| Gbit per mm2 | 0.542 | 0.634 | 0.566 | 0.681 |

With the second generation 19nm NAND, Toshiba/SanDisk has been able to cut the bitline length from 26nm to 19.5nm. It's still 19nm per marketing standards but at the engineering level this is pretty significant. Unfortunately the NAND is so new that I don't know what Toshiba/SanDisk has done to achieve a 19nm x 19.5nm cell size. It's certainly possible that Toshiba/SanDisk has also transitioned to a high-k metal gate process but we'll know more when the chip is put under a microscope.

It's interesting that while IMFT's 20nm NAND has smaller cell size than Toshiba's/SanDisk's first generation 19nm die, the density is still lower. I believe this has to do with IMFT's relatively poor memory area efficiency, which is only 52% for the 20nm 64Gbit die (i.e. 52% of the die is the actual memory part; the rest is peripheral circuits like interconnects and alike).

The real question for most users will be what sort of performance you can get out of the new NAND, however, so let's move on to benchmarks with the Plextor M6S/M6M.

30 Comments

View All Comments

nick2crete - Thursday, April 10, 2014 - link

Christian ,the Crucial M550 has the Marvell 9189 controller ,so what are the differences from 9187,9188 and 9189

Kristian Vättö - Friday, April 11, 2014 - link

9189 is an updated version of the 9187 with full DevSleep and LPDDR support.9188 is a light version of the 9187 with four channels instead of eight.

nick2crete - Friday, April 11, 2014 - link

Thank you !maybe you should correct it in the review ,because as it is written is meant that the M550 has the 9187 or you meant the M500 probably ..

HisDivineOrder - Thursday, April 10, 2014 - link

The main reason to release a derivative product is because "the other guys" are releasing new products and you don't want to seem behind.AKA AMD re-releasing the 7xxx series as R9 parts with new branding and new "newness." nVidia, Intel, they all do it. In fact, Intel's about to do it again.

payton2037 - Sunday, April 13, 2014 - link

Start a Second Income™with the company that's first with Internet entrepreneurs!For more Details Please visit at :--

http://www.sfi4.com/14161637/FREE

watersb - Monday, April 14, 2014 - link

Fantastic overview of NAND drive internals. Bundle this up as an Amazon Single for $1.99 and take my money.AbRASiON - Wednesday, April 16, 2014 - link

Would I be right in assuming when the author writes "manufacturers are preparing for the PCI-e era" regarding SSD storage, we're looking at that NGFF or whatever it is, next gen mSATA port? I mean surely they don't expect us to blow a PCI-e port on storage? (I would if it was worth it, most wouldn't)Antronman - Monday, April 21, 2014 - link

PCIe storage already exists at the consumer level...Extremely expensive, 1.4TB Read 700MB Write PCIe SSDs.

420GB, 1500USD.

Ultraspark - Thursday, April 24, 2014 - link

On Amazon Plextor m5p 128gb cost about 117$, and not 200$. I wonder how did you found such price. Or on newegg prices are updated once per 2 year, or this is an cheap review "paid" by someone to put Plextor in a bad light. It is well known that the controller+memory tandem is a half job. The firmware do the other half of job. You'll never feel in real life few tens of Mbps or few thousands of IOPS. The main goal of plextor is reliability! Just remember the Sandforce devices with shitty firmware who die like no one else. The MxS series is a preparation for MxP series. Remember the new revision of M5S. It is almost M5P with very small difference, without a chance to feel that difference in real life. Just different firmware and case. So, let's be honest dear reviwer: a good car is just a half job. If you want to win you need a good driver. The same is with plextor. This is 1st firmware. It is just to work. The future firmwares will do the magic, like on M5 Series. And When you search for price, be honest to search for lowest, not for highest. Please correct from 200$ to 117$Ultraspark - Thursday, April 24, 2014 - link

Or change the supplier. I never buy from newegg.