The Bulldozer Review: AMD FX-8150 Tested

by Anand Lal Shimpi on October 12, 2011 1:27 AM ESTThe Architecture

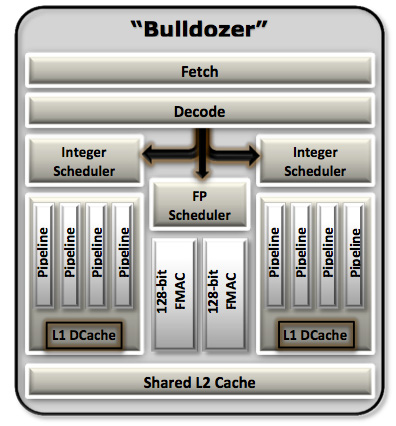

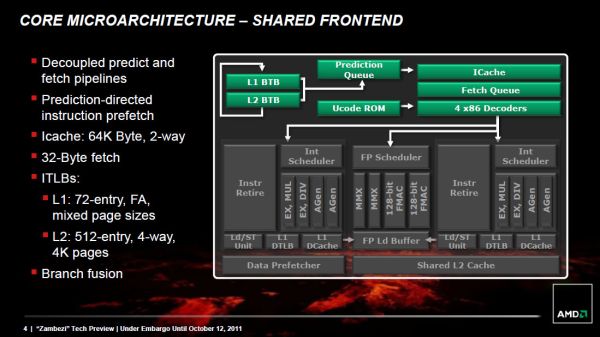

We'll start, logically, at the front end of a Bulldozer module. The fetch and decode logic in each module is shared by both integer cores. The role this logic plays is to fetch the next instruction in the thread being executed, decode the x86 instruction into AMD's own internal format, and pass the decoded instruction onto the scheduling hardware for execution.

AMD widened the K8 front end with Bulldozer. Each module is now able to fetch and decode up to four x86 instructions from a single thread in parallel. Each of the four decoders are equally capable. Remembering that each Bulldozer module appears as two cores, the front end can only pick 4 instructions to fetch and decode from a single thread at a time. A single Bulldozer module can switch between threads as often as every clock.

Decode hardware isn't very expensive on its own, but duplicating it four times across multiple cores quickly adds up. Although decode width has increased for a single core, multi-core Bulldozer configurations can actually be at a disadvantage compared to previous AMD architectures. Let's look at the table below to understand why:

| Front End Comparison | |||||

| AMD Phenom II | AMD FX | Intel Core i7 | |||

| Instruction Decode Width | 3-wide | 4-wide | 4-wide | ||

| Single Core Peak Decode Rate | 3 instructions | 4 instructions | 4 instructions | ||

| Dual Core Peak Decode Rate | 6 instructions | 4 instructions | 8 instructions | ||

| Quad Core Peak Decode Rate | 12 instructions | 8 instructions | 16 instructions | ||

| Six/Eight Core Peak Decode Rate | 18 instructions (6C) | 16 instructions | 24 instructions (6C) | ||

For a single instruction thread, Bulldozer offers more front end bandwidth than its predecessor. The front end is wider and just as capable so this makes sense. But note what happens when we scale up core count.

Since fetch and decode hardware is shared per module, and AMD counts each module as two cores, given an equivalent number of cores the old Phenom II actually offers a higher peak instruction fetch/decode rate than the FX. The theory is obviously that the situations where you're fetch/decode bound are infrequent enough to justify the sharing of hardware. AMD is correct for the most part. Many instructions can take multiple cycles to decode, and by switching between threads each cycle the pipelined front end hardware can be more efficiently utilized. It's only in unusually bursty situations where the front end can become a limit.

Compared to Intel's Core architecture however, AMD is at a disadvantage here. In the high-end offerings where Intel enables Hyper Threading, AMD has zero advantage as Intel can weave in instructions from two threads every clock. It's compared to the non-HT enabled Core CPUs that the advantage isn't so clear. Intel maintains a higher instantaneous decode bandwidth per clock, however overall decoder utilization could go down as a result of only being able to fill each fetch queue from a single thread.

After the decoders AMD enables certain operations to be fused together and treated as a single operation down the rest of the pipeline. This is similar to what Intel calls micro-ops fusion, a technology first introduced in its Banias CPU in 2003. Compare + branch, test + branch and some other operations can be fused together after decode in Bulldozer—effectively widening the execution back end of the CPU. This wasn't previously possible in Phenom II and obviously helps increase IPC.

A Decoupled Branch Predictor

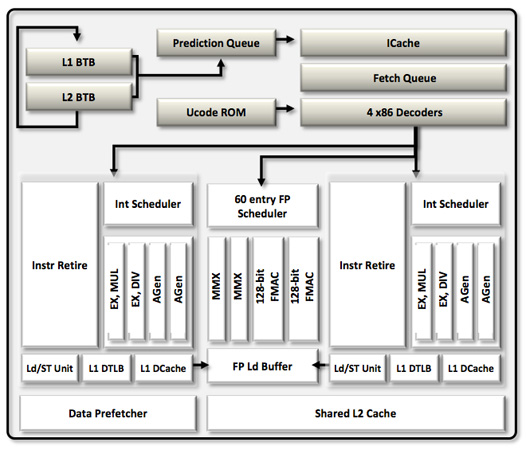

AMD didn't disclose too much about the configuration of the branch predictor hardware in Bulldozer, but it is quick to point out one significant improvement: the branch predictor is now significantly decoupled from the processor's front end.

The role of the branch predictor is to intercept branch instructions and predict their target address, rather than allowing for tons of cycles to go by until the branch target is known for sure. Branches are predicted based on historical data. The more data you have, and the better your branch predictors are tuned to your workload, the more accurate your predictions can be. Accurate branch prediction is particularly important in architectures with deep pipelines as a mispredict causes more instructions to be flushed out of the pipe. Bulldozer introduces a significantly deeper pipeline than its predecessor (more on this later), and thus branch prediction improvements are necessary.

In both Phenom II and Bulldozer, branches are predicted in the front end of the pipe alongside the fetch hardware. In Phenom II however, any stall in the fetch pipeline (e.g. fetching an instruction that wasn't in cache) would stop the whole pipeline including future branch predictions. Bulldozer decouples the branch prediction hardware from the fetch pipeline by way of a prediction queue. If there's a stall in the fetch pipeline, Bulldozer's branch prediction hardware is allowed to run ahead and continue making future predictions until the prediction queue is full.

We'll get to the effectiveness of this approach shortly.

Scheduling and Execution Improvements

As with Sandy Bridge, AMD migrated to a physical register file architecture with Bulldozer. Data is now only stored in one location (the physical register file) and is tracked via pointers back to the PRF as operations make their way through the execution engine. This is a move to save power as copying data around a chip is hardly power efficient.

The buffers and queues that feed into the execution engines of the chip are all larger on Bulldozer than they were on Phenom II. Larger data structures allows for better instruction level parallelism when trying to execute operations out of order. In other words, the issue hardware in Bulldozer is beefier than its predecessor.

Unfortunately where AMD took one step forward in issue hardware, it does a bit of a shuffle when it comes to execution resources themselves. Let's start with the positive: Bulldozer's integer execution cores.

Integer Execution

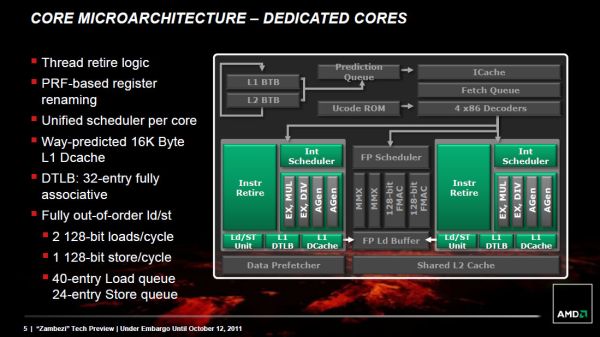

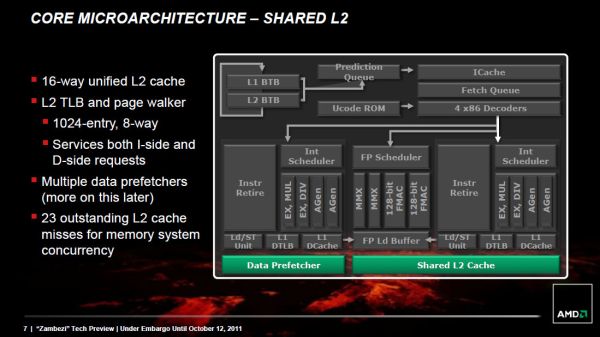

Each Bulldozer module features two fully independent integer cores. Each core has its own integer scheduler, register file and 16KB L1 data cache. The integer schedulers are both larger than their counterparts in the Phenom II.

The biggest change here is each integer core now has two ports instead of three. A single integer core features two AGU/ALU ports, compared to three in the previous design. AMD claims the third ALU/AGU pair went mostly unused in Phenom II, and as a result it's been removed from Bulldozer.

With larger structures feeding into the integer cores, AMD should be able to have an easier time of making use of the integer units than in previous designs. AMD could, in theory, execute more integer operations per core in Phenom II however AMD claims the architecture was typically bound elsewhere.

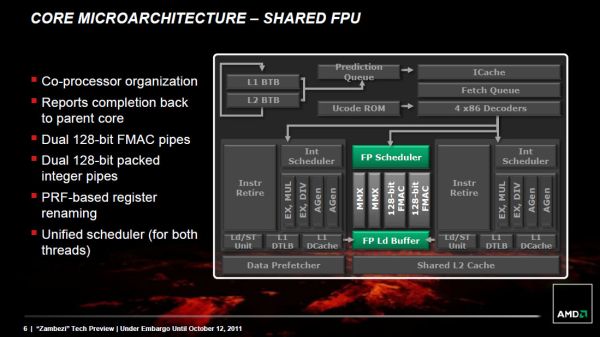

The Shared FP Core

A single Bulldozer module has a single shared FP core for use by up to two threads. If there's only a single FP thread available, it is given full access to the FP execution hardware, otherwise the resources are shared between the two threads.

Compared to a quad-core Phenom II, AMD's eight-core (quad-module) FX sees no drop in floating point execution resources. AMD's architecture has always had independent scheduling for integer and floating point instructions, and we see the same number of execution ports between Phenom II cores and FX modules. Just as is the case with the integer cores, the shared FP core in a Bulldozer module has larger scheduling hardware in front of it than the FPU in Phenom II.

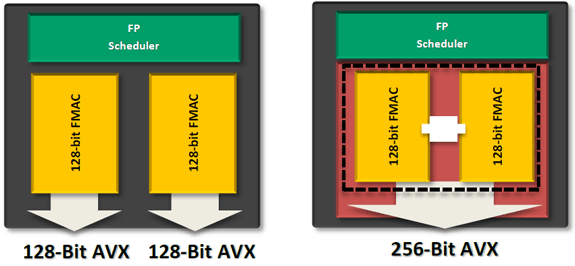

The problem is AMD had to increase the functionality of its FPU with the move to Bulldozer. The Phenom II architecture lacks SSE4 and AVX support, both of which were added in Bulldozer. Furthermore, AMD chose Bulldozer as the architecture to include support for fused multiply-add instructions (FMA). Enabling FMA support also increases the relative die area of the FPU. So while the throughput of Bulldozer's FPU hasn't increased over K8, its capabilities have. Unfortunately this means that peak FP throughput running x87/SSE2/3 workloads remains unchanged compared to the previous generation. Bulldozer will only be faster if newer SSE, AVX or FMA instructions are used, or if its clock speed is significantly higher than Phenom II.

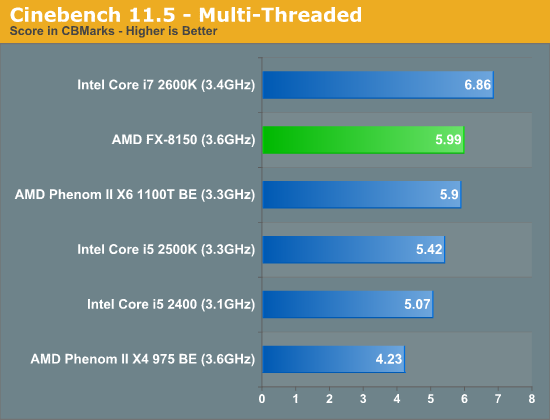

Looking at our Cinebench 11.5 multithreaded workload we see the perfect example of this performance shuffle:

Despite a 9% higher base clock speed (more if you include turbo core), a 3.6GHz 8-core Bulldozer is only able to outperform a 3.3GHz 6-core Phenom II by less than 2%. Heavily threaded floating point workloads may not see huge gains on Bulldozer compared to their 6-core predecessors.

There's another issue. Bulldozer, at least at launch, won't have to simply outperform its quad-core predecessor. It will need to do better than a six-core Phenom II. In this comparison unfortunately, the Phenom II has the definite throughput advantage. The Phenom II X6 can execute 50% more SSE2/3 and x87 FP instructions than a Bulldozer based FX.

Since the release of the Phenom II X6, AMD's major advantage has been in heavily threaded workloads—particularly floating point workloads thanks to the sheer number of resources available per chip. Bulldozer actually takes a step back in this regard and as a result, you will see some of those same workloads perform worse, if not the same as the outgoing Phenom II X6.

Compared to Sandy Bridge, Bulldozer only has two advantages in FP performance: FMA support and higher 128-bit AVX throughput. There's very little code available today that uses AMD's FMA instruction, while the 128-bit AVX advantage is tangible.

Cache Hierarchy and Memory Subsystem

Each integer core features its own dedicated L1 data cache. The shared FP core sends loads/stores through either of the integer cores, similar to how it works in Phenom II although there are two integer cores to deal with now instead of just one. Bulldozer enables fully out-of-order loads and stores, an improvement over Phenom II putting it on parity with current Intel architectures. The L1 instruction cache is shared by the entire bulldozer module, as is the L2 cache.

The instruction cache is a large 64KB 2-way set associative cache, similar in size to the Phenom II's L1 cache but obviously shared by more "cores". A four-core Phenom II would have 256KB of total L1 I-Cache, while a four core Bulldozer will have half of that. The L1 data caches are also significantly smaller than Bulldozer's predecessor. While Phenom II offered a 64KB L1 D-Cache per core, Bulldozer only offers 16KB per integer core.

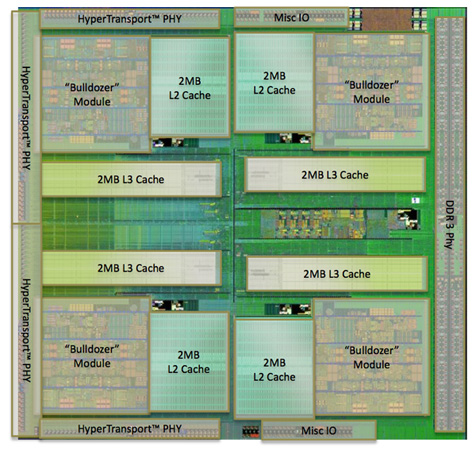

The L2 cache is much larger than what we saw in multi-core Phenom II designs however. Each Bulldozer module has a private 2MB L2 cache.

There's a single 8MB L3 cache that's shared among all Bulldozer modules on a chip. In its first incarnation, AMD has no plans to offer a desktop part without an L3 cache. However AMD indicated that the L3 cache was only really useful in server workloads and we might expect future Bulldozer derivatives (ahem, Trinity?) to forgo the L3 cache entirely as a result.

Cache accesses require more clocks in Bulldozer, due to a combination of size and AMD's desire to make Bulldozer a very high clock speed part...

430 Comments

View All Comments

vectorm12 - Wednesday, October 12, 2011 - link

As both AMD and Intel now use dedicated hardware for AES I feel simply testing AES performance isn't enough. A benchmark of the AES+Twofish+Serpent or atleast AES+Serpent would serve as a more telling benchmark at this point. Don't get me wrong I love that you guys even run a benchmark related to Encryption but it needs to be updated.About BD I'm also extremely bummed out that it didn't turn out better than this. Ofc there might be room for improvements with patches/cpu-driver for windows7 etc but considering the TDP, transistor-count and everything else this is a huge loss for AMD.

I'm still interested in seeing how the Opteron versions will perform in specific tasks as the architecture itself seems really interesting. Someone obviously spent a lot of time thinking this design through and I'd like to believe there's at least one particular workload where BD can actually flex it's muscles for real.

fri2219 - Wednesday, October 12, 2011 - link

Since Bulldozer wasn't created with 3D shooters in mind, it would have been nice to see some financial/engineering/scientific benchmarks instead. Anandtech used to differentiate itself from the kiddie sites by providing that sort of analysis. I guess things change, like my RSS subscription to Anandtech articles will.That said, the power consumption numbers pretty much say everything I need to know about the CPU series- the constraint on almost all HPC is power, not SPECint or peak flops.

chillmelt - Wednesday, October 12, 2011 - link

Unfortunately a huge majority of the enthusiast market are gamers. If you truly want productivity benchmarks then wait for server chips. FX CPUs aren't marketed as such, but does perform like one.With that said, the FX lineup is a decent multi-threading powerhouse, and not flop in that respect.

Read tomshardware's review for more benchmarks.

Malih - Wednesday, October 12, 2011 - link

well, i guess there'll be follow up posts."My sample actually arrived less than 12 hours ago, so expect a follow up with performance analysis later this week."

lagrande - Wednesday, October 12, 2011 - link

I'm not AMD fan boy, but the reason AMD gave is pretty reasonable. Thread locality is an important factor in bulldozer architecture, primarily because the memory latency on the cache level is pretty high. If the OS can't schedule the thread properly to the correct core, then there will be a lot of inter-core data movement and probably problem like false sharing can be more apparent.GatorLord - Wednesday, October 12, 2011 - link

While on one hand as a PC user and builder...and really wanting to build a BD based mindblower, I'm a little disappointed...OK, more than a little...by these results. On the other hand, as an MBA and investor in AMD, I see the big picture and have to reluctantly agree...and hopefully profit.If you have constrained and finite capabilities in both design and manufacture (GloFo needs its butt kicked), you maximize along a marginal ROI track and right now that would be server chips to support the growing and lucrative cloud, data warehouse, HPC, and corporate servers and the growing fusion space integrating modest x86 with robust video on low wattage single chips, you end up with exactly what we have here. BD (a server chip rebranded) and Llano with plans to improve both with descendents.

In highway terms it would be akin to building semis and commuter cars. This is the high performance forum and while the Ferrari Enzos are cool and badass, it's hard to fault AMD for the approach. After all, when you're on the road today, you'll see a bunch of semis and commuter cars...its economics. Performance sells magazines, utility sells products.

BD must be a killer server beast because Cray (you know Cray, right?) just got a $97M contract from Oak Ridge NL about a month or so after taking possession of the first box of BD based server chips. I think Cray knows a thing or two about making computers haul butt.

Now we'll see if any of that translates into the client space...

MossySF - Wednesday, October 12, 2011 - link

I'll agree with this. We have a ton of servers -- both Intel and AMD. More integer cores are better. FPU? Games? 3D? Media encoding? Who cares. Hyper-threading does nothing when you peg all cores with VMs running at full blast. For example, we have 1 configuration where we run 4 VMs on a Phenom II x4 3ghz and it performs roughly the same as our 4-core i7 2.8ghz. If we add a 5th VM, both slow down equally showing that there are simply no free resources in the CPU pipeline for hyper-threading to steal.So where the bulldozer platform is extra good is for cheap / disposable / uniform VM hosts running Linux. Instead of 1 mega expensive quad xeon costing $100K, you have 10 x 1U Bulldozers that can handle 8VMs each at full utilization without speed degradation for $10K. In addition, you'd probably run something like Centos (or RHEL) the default packages are not compiled with Intels uber compiler so many of the +25% you see in benchmarks here don't exist at all in the Linux world.

The most disappointing part though (which I mentioned previously) is the lack of speed improvement for the chipset. The first bottleneck for adding more VMs is CPU core but the 2nd is disk bandwidth. If you have disk intensive VMs, you need a separate hard drive for each VM to avoid HD seek latency killing performance. But putting 8 HDs in a 1U is impossible so you need 2U/4U servers taking up too much rackspace.

The answer of course is a fast SSD ... 500MB/s with 0 latency can be split off to separate VMs with a linear degradation versus exponential for HDs. But the SB950 chipset at 2GB/s bidirectional can only handle 2 fast SSDs. So 1000 MB/s divided by 8 VMs reading at full blast is 125 MB/s per VM -- which is regular SATA3 HD speed. Double that to 4 GB/s and you can put easily put 4 x 2.5" SATA3 SSDs in a 1U delivering 250 MB/s to each VM. Now we're back to at least 2nd generation SSD performance.

(Note, all the Intel chipsets also max out at 2GB/s bidirectional and stuffing a super expensive raid controller in a 1U is not cost effective.)

GatorLord - Wednesday, October 12, 2011 - link

Great analysis...I'm not a server guy and can hardly keep up with the average 15 year old on desktop jargon and theory, but it seems that the bigger cache would mitigate the roundtrips to disk in the conditions you describe. I guess that's why they left that fat L3 cache on the die...assuming Interlagos and Zambezi are really closer than cousins...more like siblings.Great financial case...that I get. I heard a joke the other day that went something like "Whenever they say it's not about the money, it's about the money". It's always about the money... :)

Macabre215 - Wednesday, October 12, 2011 - link

This is reminiscent of the Phenom I launch without the TLB bug. You have a chip that barely outperforms its predecessor and at times performs a little worse. AMD might be able to make a Phenom II like product out of Bulldozer but I I think it's too late. They needed to start out well out of the gate with this one.Right now I'm on a Phenom II and will be upgrading to Sandy Bridge soon. I'm done with AMD on the desktop front; a platform which is probably a dead one in the next ten to twenty years anyway. AMD should just stick to the server market and mobile platforms for CPUs as that's where they have a dog in the hunt.

BTW, this is a disgrace to the FX name.

Iketh - Wednesday, October 12, 2011 - link

I understand why AMD execs resigned in the past 2 years... can you imagine what it musta looked like then? "Nah, we've actually gotten slower per thread, and will need 4ghz+ to compete now..."