Everything You Always Wanted to Know About SDRAM (Memory): But Were Afraid to Ask

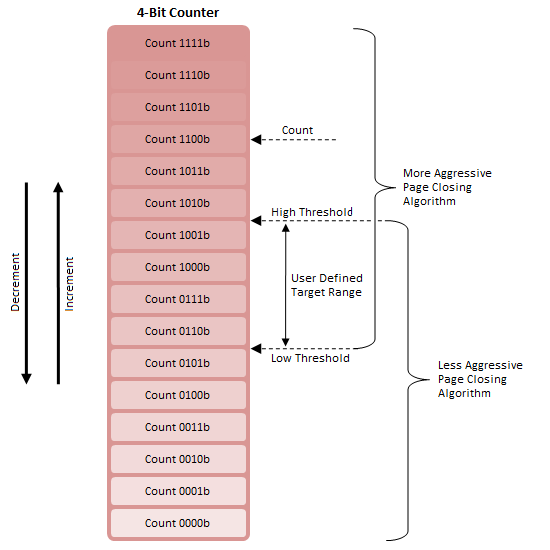

by Rajinder Gill on August 15, 2010 10:59 PM ESTFirst, consider a 4-bit counter with two adjustable thresholds (Figure 12). When Count is greater than High Threshold, Algorithm A is deemed appropriate; the same is true concerning Algorithm B and Count less than Low Threshold.

For the range between High Threshold and Low Threshold, either algorithm may be in effect. This is because a switch from Algorithm B to Algorithm A will occur only with Count greater than High Threshold and increasing and a switch from Algorithm A to Algorithm B will occur only with Count less than Low Threshold and decreasing.

The overlap range is also the Target Range as the system will naturally attempt to maintain Counter between these two points. This is true since Algorithm A tends to lower Count while Algorithm B tends to raise Count. This system acts to reduce or eliminate rapid thrashing between algorithms.

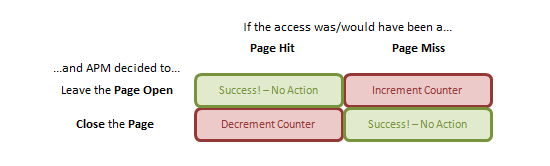

Next, define a truth table (Figure 13) defining how Count will vary. By doing so we can encode a feedback mechanism into our system. Successful predictions by the Adaptive Page Close Logic - a prevented page-miss access (good) in response to a decision to close a page or a facilitated page-hit access (good) in response to a decision to leave a page open - suggest no change to policy is required and so never modify Count.

For a facilitated page-miss access (bad) due to a poor decision to leave a page open, increment Count. If Count were to trend upward we could conceivably conclude that the current policy was most often wrong and not only that, tended to leave pages open far too long while "fishing" for page-hit operations. The current algorithm must not be closing pages aggressively enough.

For a prevented page-hit access (bad) due to a poor decision to close a page early, decrement Count. If Count were to trend downward we would suspect the opposite: the algorithm is too aggressively closing pages and leaving potential page-hits on the cutting room floor.

As best we can tell, this construct represent reality for APM Technology. Although we would like to believe the system has more than two gears (algorithms), our model perfectly explains the existing control register both in type and number.

Looking ahead you will see Max Page Close Limit and Min Page Close Limit are the specified High and Low Threshold values, respectively. Setting a larger difference increases the size of the feedback dead band, slowing the rate at which system responds to its own evaluative efforts. Mistake Counter is represented by the starting Count and should be set somewhere near the middle of the dead band.

Adaptive Timeout Counter sets the assertion time of any decision to keep a page open (i.e. how long before the decision to keep a page open stands before we give up hope of a page-hit access). Repeated access to the same page will reset this counter each time as long as the remaining lifetime is non-zero. Lower values result in a more aggressive page close policy and vice versa for higher values.

Request Rate, we believe, controls how often Count (Mistake Counter) is updated, and therefore how smoothly the system adapts to quickly changing workloads. There must be a good reason not to flippantly set this interrupt rate as low as possible. Perhaps this depletes hardware resources needed for other operations or maybe higher duty cycles disproportionally raises power consumption. Whatever the reason, there's more than a fair chance you can hurt performance if you're just spit-balling with this setting.

46 Comments

View All Comments

mupilot - Monday, August 16, 2010 - link

Nice article, its very in depth, but easy to read! I'll have to read through a couple times if I truly want to understand how my memory works so I can actually understand what I'm doing when I overclock my memory and adjust the timings.Cool Mike - Monday, August 16, 2010 - link

I find memory a bit confusing. What type of memory would be best (or even work) on an AMD system - for example the Asus M4N98TD EVO. Will the lower voltage modules work? I'd like to get some pretty decent memory, but almost all of the discussions are around Intel based chipsets. Any help would be appreciated.vajm1234 - Monday, August 16, 2010 - link

---- well i too wanna see a comparison how AMD works against the intelPrinceGaz - Monday, August 16, 2010 - link

Whilst the text for the Mistake Counter is incorrect, the bit count in the table does match the text-- the PARAMS2 register holds the 9, not 8 MSBs of each parameter (the internal values being 13 bit, not 12 bit), and the text and diagram both agree on this.PrinceGaz - Monday, August 16, 2010 - link

Oh and by the way, thankyou for an extremely informative article which has refreshed (hehe) and added to what I knew about how RAM operates and the effects of the main timings.Icepop66 - Monday, August 16, 2010 - link

Thanks for touching on some of the important aspects of sdram architecture and function and how they're related. My understanding is better now. Thanks for consistently good articles and reviews.Gary Key - Monday, August 16, 2010 - link

Rampage III Extreme -BIOS 0878 -

1. Opened Memory Timing Selections for Ultimate Tweaking

2. General Performance Enhancements for Overclocking

3. AnandTech Memory Article BIOS - Support provided by ASUS USA Tech Support (that would be me).

http://www.mediafire.com/?850dsymmc9j7jdd

lowenz - Monday, August 16, 2010 - link

Simply AWESOME article!Muhammed - Monday, August 16, 2010 - link

You didn't mention the fact that (for example) DDR3 1600MHz actually works @200 MHz , and by fetching 8-bits per clock , it can effectively work like a 1600MHz RAM .DDR2 @800 MHz , actually works at 200MHz too but fetching 4-bits per clock .

DDR@400 MHz , actually works at 200MHz too , fetching 2-bits per clock .

MrBrownSound - Monday, August 16, 2010 - link

Thank you for helping me understand. Yes I was afraid to ask, or maybe I just felt I didn't need to know. I was wrong.