AMD's Radeon HD 5870: Bringing About the Next Generation Of GPUs

by Ryan Smith on September 23, 2009 9:00 AM EST- Posted in

- GPUs

More GDDR5 Technologies: Memory Error Detection & Temperature Compensation

As we previously mentioned, for Cypress AMD’s memory controllers have implemented a greater part of the GDDR5 specification. Beyond gaining the ability to use GDDR5’s power saving abilities, AMD has also been working on implementing features to allow their cards to reach higher memory clock speeds. Chief among these is support for GDDR5’s error detection capabilities.

One of the biggest problems in using a high-speed memory device like GDDR5 is that it requires a bus that’s both fast and fairly wide - properties that generally run counter to each other in designing a device bus. A single GDDR5 memory chip on the 5870 needs to connect to a bus that’s 32 bits wide and runs at base speed of 1.2GHz, which requires a bus that can meeting exceedingly precise tolerances. Adding to the challenge is that for a card like the 5870 with a 256-bit total memory bus, eight of these buses will be required, leading to more noise from adjoining buses and less room to work in.

Because of the difficulty in building such a bus, the memory bus has become the weak point for video cards using GDDR5. The GPU’s memory controller can do more and the memory chips themselves can do more, but the bus can’t keep up.

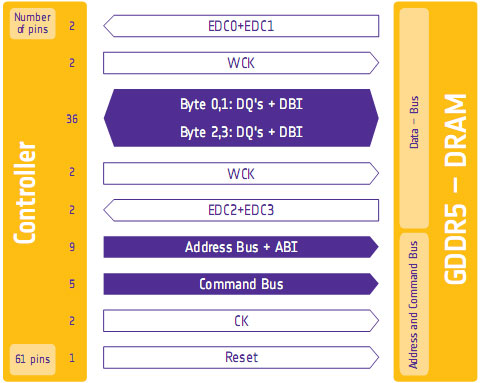

To combat this, GDDR5 memory controllers can perform basic error detection on both reads and writes by implementing a CRC-8 hash function. With this feature enabled, for each 64-bit data burst an 8-bit cyclic redundancy check hash (CRC-8) is transmitted via a set of four dedicated EDC pins. This CRC is then used to check the contents of the data burst, to determine whether any errors were introduced into the data burst during transmission.

The specific CRC function used in GDDR5 can detect 1-bit and 2-bit errors with 100% accuracy, with that accuracy falling with additional erroneous bits. This is due to the fact that the CRC function used can generate collisions, which means that the CRC of an erroneous data burst could match the proper CRC in an unlikely situation. But as the odds decrease for additional errors, the vast majority of errors should be limited to 1-bit and 2-bit errors.

Should an error be found, the GDDR5 controller will request a retransmission of the faulty data burst, and it will keep doing this until the data burst finally goes through correctly. A retransmission request is also used to re-train the GDDR5 link (once again taking advantage of fast link re-training) to correct any potential link problems brought about by changing environmental conditions. Note that this does not involve changing the clock speed of the GDDR5 (i.e. it does not step down in speed); rather it’s merely reinitializing the link. If the errors are due the bus being outright unable to perfectly handle the requested clock speed, errors will continue to happen and be caught. Keep this in mind as it will be important when we get to overclocking.

Finally, we should also note that this error detection scheme is only for detecting bus errors. Errors in the GDDR5 memory modules or errors in the memory controller will not be detected, so it’s still possible to end up with bad data should either of those two devices malfunction. By the same token this is solely a detection scheme, so there are no error correction abilities. The only way to correct a transmission error is to keep trying until the bus gets it right.

Now in spite of the difficulties in building and operating such a high speed bus, error detection is not necessary for its operation. As AMD was quick to point out to us, cards still need to ship defect-free and not produce any errors. Or in other words, the error detection mechanism is a failsafe mechanism rather than a tool specifically to attain higher memory speeds. Memory supplier Qimonda’s own whitepaper on GDDR5 pitches error correction as a necessary precaution due to the increasing amount of code stored in graphics memory, where a failure can lead to a crash rather than just a bad pixel.

In any case, for normal use the ramifications of using GDDR5’s error detection capabilities should be non-existent. In practice, this is going to lead to more stable cards since memory bus errors have been eliminated, but we don’t know to what degree. The full use of the system to retransmit a data burst would itself be a catch-22 after all – it means an error has occurred when it shouldn’t have.

Like the changes to VRM monitoring, the significant ramifications of this will be felt with overclocking. Overclocking attempts that previously would push the bus too hard and lead to errors now will no longer do so, making higher overclocks possible. However this is a bit of an illusion as retransmissions reduce performance. The scenario laid out to us by AMD is that overclockers who have reached the limits of their card’s memory bus will now see the impact of this as a drop in performance due to retransmissions, rather than crashing or graphical corruption. This means assessing an overclock will require monitoring the performance of a card, along with continuing to look for traditional signs as those will still indicate problems in memory chips and the memory controller itself.

Ideally there would be a more absolute and expedient way to check for errors than looking at overall performance, but at this time AMD doesn’t have a way to deliver error notices. Maybe in the future they will?

Wrapping things up, we have previously discussed fast link re-training as a tool to allow AMD to clock down GDDR5 during idle periods, and as part of a failsafe method to be used with error detection. However it also serves as a tool to enable higher memory speeds through its use in temperature compensation.

Once again due to the high speeds of GDDR5, it’s more sensitive to memory chip temperatures than previous memory technologies were. Under normal circumstances this sensitivity would limit memory speeds, as temperature swings would change the performance of the memory chips enough to make it difficult to maintain a stable link with the memory controller. By monitoring the temperature of the chips and re-training the link when there are significant shifts in temperature, higher memory speeds are made possible by preventing link failures.

And while temperature compensation may not sound complex, that doesn’t mean it’s not important. As we have mentioned a few times now, the biggest bottleneck in memory performance is the bus. The memory chips can go faster; it’s the bus that can’t. So anything that can help maintain a link along these fragile buses becomes an important tool in achieving higher memory speeds.

327 Comments

View All Comments

Ryan Smith - Wednesday, September 23, 2009 - link

The load temp is the same as a single card.ilnot1 - Wednesday, September 23, 2009 - link

Does anyone have a link to any review that compares 4850's, 4870's, and 4890's in Crossfire against the 5870 & 5870 CF setup?T2k - Wednesday, September 23, 2009 - link

FWIW: http://www.techpowerup.com/reviews/AMD/HD_5870_PCI...">http://www.techpowerup.com/reviews/AMD/HD_5870_PCI...T2k - Wednesday, September 23, 2009 - link

Ehh, I meant: http://www.techpowerup.com/reviews/ATI/Radeon_HD_5...">http://www.techpowerup.com/reviews/ATI/Radeon_HD_5...ilnot1 - Wednesday, September 23, 2009 - link

Thanks T2k, but the only cards that are in Crossfire in that review are the 58XX's. There are no other comparisons to cards in CF or SLI. Since Ryan included some of the most recent nVida cards in SLI I was hoping to find the 48XX's in CF.T2k - Thursday, September 24, 2009 - link

Basically the rule of thumb seems to be that at 1920x1200 a single 5870 is still slightly slower than 4870X2 and probably slightly faster than a 4850X2 2GB.I own the latter so I will wait this time - either they lower the initial price of the 5870X2 or they release a 5850X2, otherwise I'll pass because single 5870 is simply OVERPRICED as it is already.

T2k - Wednesday, September 23, 2009 - link

Seriously: we get a very nice technical background section - then you top it with this more than idiotic collection of games for testing, leaving out 4850X2 2GB, 5850, using TWO stupid CryEngine-based PoS from Crytek, the most un-optimized code producers or WoW, of which even you admit it's CPU-bounded but now CoD:WaW, no Clear Sky, no UT3 or rather a single current Unreal Eninge-based game?Benchmarking part is ALMOST WORTHLESS, the only useful info is that unless you go above 1920x1200 the 4870X2 pretty much owns 5870's @ss as of now.

Ryan Smith - Wednesday, September 23, 2009 - link

For what it's worth, Batman: Arkham Asylum is UE3 engine based.T2k - Wednesday, September 23, 2009 - link

OK, I missed that (probably because I found the game shots ugly and became uninterested.)But how about ET:QW? Yes, it's not the best looking game but it is still popular, let alone World at War which is both great looking and crazy popular, let alone Clear Sky which is a very demanding DX10.1 game? Where is Fallout 3? Where is Modern Warfare?

FFS the most demanding are the quick ation-shooters and we, FPS players are the first one to upgrade to new cards...

Werelds - Thursday, September 24, 2009 - link

How would ET:QW be a good benchmark? Last I checked, it's still limited to the 30 FPS animations, which makes running it at more than 30 FPS pointless because everything will look jerky.I agree something like the CoD games should be included for comparison's sake, but they're hardly a good benchmark or taxing on a system. QW does not fall into the same category though, it has a smaller active playerbase than even L4D which lost a lot of players due to the lack of updates.