Foxconn Black Ops - Raw, Unadulterated Power

by Rajinder Gill on July 30, 2008 11:00 PM EST- Posted in

- Motherboards

Quick BIOS Overview

We're going to provide a small breakdown of important BIOS functions in this section. Any functions not highlighted below can generally be left safely at defaults or are self-explanatory to those who benchmark.

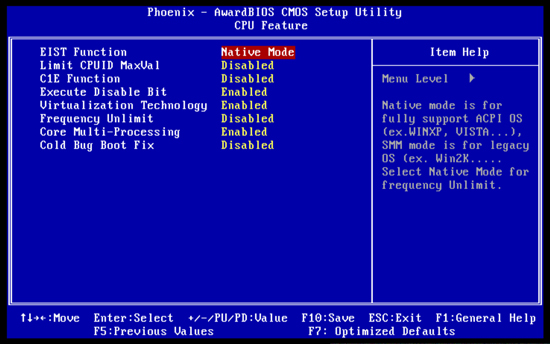

Cold Bug Boot Fix

Enabling this function shifts the PWM sensing of the processor max-min temperature threshold down to 50C, allowing the board to boot below -120C. Until now, X38/X48-based motherboards have been plagued with non-booting issues below -50C. Foxconn managed to work around CPU and motherboard minimum temperature limits with this function. Only use "Enabled" if extreme cooling is employed to cool the processor, as maximum core temperature with this function enabled is 50C.

|

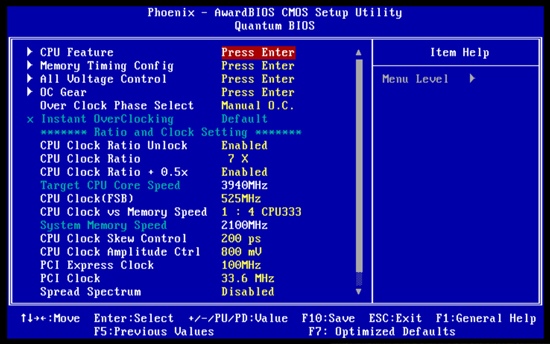

CPU Clock vs. Memory Speed

The best memory divider for overclocking is generally 1:4.333. 1:3.2 may be used if FSB speeds exceed the maximum memory speed of your modules. Please note that onboard FSB jumpers may need to be set to the FSB speed of your processor for the lower ratio dividers to work.

CPU Clock Skew Control

This function adjusts the PLL reference clock output by delaying the clock signal output to the MCH. The range of interest is between 0 and 300ps. Between 500 and 540 FSB we used 200ps; anything higher may require a setting of 300ps. Any changes to this function will also manifest downstream for memory channel skews (especially CTRL and CMD skew), which will need readjustment if CPU Clock Skew values are changed.

Clock Amplitude Control

Default here is 800mv and we found the default setting to be best. If you change the voltage, be prepared to realign MCH skew values in the memory settings page as a higher or lower output voltage affects the waveform integrity/jitter of the output clock signal from the PLL chip. Maximum FSB speeds are generally reached with 800mv.

PCI Express Clock

For 24/7 systems a setting of 100MHz is preferred; for benchmarking small gains in 3D application scores may be realized by using bus speeds up to 120MHz depending on processor frequency, raw GPU transfer rates and MCH capacitive loading (depending on the graphics card used). Like other X48 boards, we found a maximum of around 110 MHz was possible for benchmarking runs with our QX9650 clocked to 5.4GHz using the G28 BIOS with a GTX 280 graphics card. There are minor scoring gains available, but success will vary from system to system depending on the components used.

In fact, while we write this, would it not be great if the next series of chipsets and graphics cards allow the user level tuning of advance PCI-E latencies/transfer rates and perhaps even drive strengths? While most of us will never need to make changes to such registers, running components way out of specification often requires the adjustment of parameters just to provide that extra margin for signal transfers or a little bit of give and take in bandwidth vs. latency when shooting for top scores in various benchmarks. It seems current PCI-E and GPU architectures are not providing us with the full flexibility that we have become accustomed to when it comes to overclocking other vital system components such as tRD, and to a lesser degree memory timings.

|

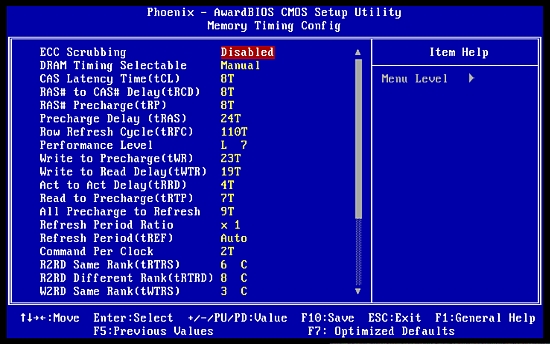

Performance Level (aka tRD)

We've said enough over the last few months about tRD for everyone to realize the importance of keeping this value as low as possible. tRD scaling of the Black Ops is generally very good; 45nm quad-core processors should have no problem benchmarking with a tRD of 6 at 455FSB - and even higher at times. Alternatively, a setting of 5 at 400-420FSB may be used with a higher processor multiplier, which also allows for some very tight sub-timing ranges. For 45nm processors, a value of 6 may be used up to 470FSB while a setting of 7 will scale to around 515FSB. Don't be surprised if you can set timings such as tWTR remarkably low for benchmarking. We've seen values as low as 2 at 414FSB using quad-cores at speeds in excess of 5.7GHz.

|

R2RD (Same), R2RD (Different), W2RD (Same), W2RD (Different)

For maximum FSB scaling, set these four options in the following order: 6, 8, 3, and 6. For benchmarking purposes, default settings are sufficient and give a small boost in memory access latency and read bandwidth.

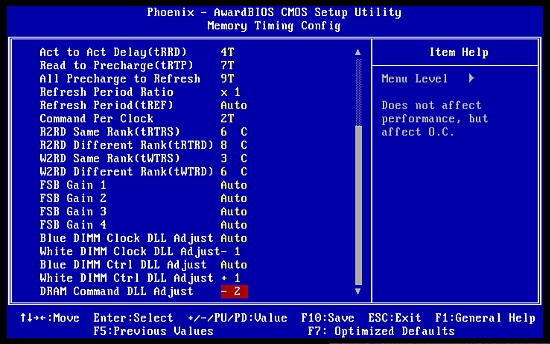

FSB Gain 1, 2, 3, 4

These four settings are best left at default. FSB Gain 1 affects memory copy bandwidth. The range for FSB Gain 1 is from -15 to +15; positive numbers are generally more aggressive while the negative range gives a very small FSB scaling gain in return for performance. FSB Gain 2 ranges from +1 to +7. Values higher than 2 are prone to cause non-boots. Out of all the FSB Gain settings, this one is best left on Auto. FSB Gain 3 and 4 affect memory access latency. Again, scales run from +1 to +7.

Higher numbers in all scales generally give more performance, although we found all four Gain settings do not follow a linear curve of performance within their respective scales. Foxconn might be better off combining all four of these settings into a single BIOS option with reduced parameters and a scale running from relaxed to aggressive to make things a little more intuitive for the end user. As they stand at present, these four settings are best left at Auto.

CLK, CTRL, and CMD Skew settings

For quad-core processors using 1GB modules for benchmarking, these settings can usually be left at default (this is due to the fact the FSB speeds usually max out at 470 FSB or so). For 2GB modules based on Micron chips, CLK and CTRL skews usually need to be set to a +2 value over 1500MHz DDR3 while CMD skew will usually prefer being left on Auto or -1.

As FSB is scaled over 460FSB, these settings will likely need further adjustment, so be prepared to sacrifice time finding the right combinations. The G28 BIOS sees the addition of separate CLK/CMD skew functions for each individual memory slot. If you're only using two modules on the G28 BIOS, we recommend using slots 2 and 4. Also, CLK and CMD skews should use the same setting. Leave CTRL skews for the empty slots on AUTO and set the value for the populated slots manually. The main item to note is that skew tuning is largely system specific and a matter of trial and error - we can't stress this enough.

VMCH will also affect the level of skews required from Foxconn's selected defaults at AUTO. This becomes especially apparent at VMCH values over 1.76V where we had to reduce all three skew parameters by one digit for a successful boot. The reason for this likely stems from the association of key MCH Vref values and the signal output stages of the MCH deriving some of their voltage from a proportion of VMCH. A higher rail voltage probably changes signal waveforms to an extent that requires less overall signal skew than stock Auto values. So, if you want to play around with high levels of VMCH for benchmarking sprints, be prepared to adjust skew values when using higher memory divider ratios.

32 Comments

View All Comments

elfguy - Thursday, July 31, 2008 - link

I disagree. A company that gets called on a screwed up practice, and gets tons of bad press, will always try to justify itself and if they see potential profit loss, they will say whatever they can to calm things down. We still don't know for sure if it was intentional or not, we only have their word for it.If they had not been called on it, things would have stayed broken. Many companies do screwed up things, and the best thing we can do is show them that look, you go against your customers needs, and you will suffer for it, in the only way they care about, that is loss sales. So I say support your alternative OSes, boycott Foxconn.

AmberClad - Thursday, July 31, 2008 - link

Good luck on trying to boycott Foxconn. The vast majority of their business is not in retail motherboards -- it's in the manufacturing of game consoles, cell phones, and various electronic components. Any motherboard you buy from another manufacturer is more than likely going to have some Foxconn components in them.