ASUS ROG Rampage Formula: Why we were wrong about the Intel X48

by Kris Boughton on January 25, 2008 4:30 AM EST- Posted in

- Motherboards

The Rules of Working with tRD: What's Allowed and What Isn't

We mentioned earlier that there are a few rules pertaining to the modification of the default tRD value for a particular memory subsystem configuration. These rules are actually more of a set of equations that we have derived in order to assist the user in pre-determining whether or not a system will POST and operate given the settings in question. They can also be used to explain after the fact why certain configurations refuse to function.

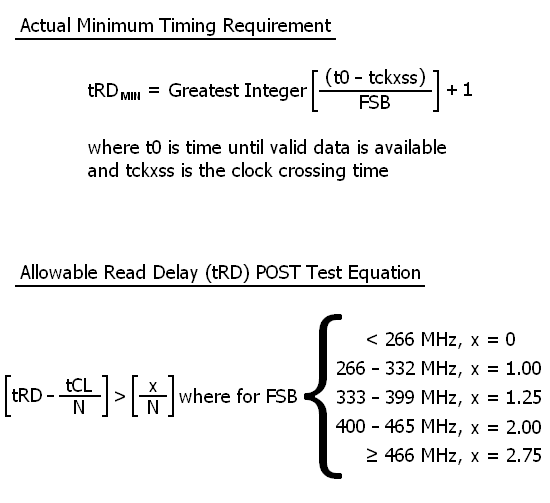

In actuality, there is only one requirement that must be satisfied when setting tRD: The MCH must have a minimum amount of time to complete the clock crossing procedure for each data bit translated from one clocking domain to the other. We have shown the equation below for those that care to know. Unfortunately it does not lend itself well to being solved as the input variables ("t0" and "tckxss") are not readily obtainable.

"t0" is the total time it takes data being returned to the CPU as read in memory to cross from the memory bus domain to the system data bus domain. This is dependent on a number of variables, including memory burst length (4 or 8 cycles), Command Rate (1N or 2N), the memory divider in use, CAS (tCL) timing, and the current FSB. "tckxss" is a little more esoteric in nature and is outside the scope of this discussion; the value is generally very small when compared to "t0". The difference in these times, rounded to the lowest integer plus one, bounds the lowest potential tRD setting necessary for data to be properly transferred from one bus to the other.

Because the first expression is too difficult to warrant everyday use, we spent many hours populating a large test matrix table created for recording the POST (Power On Self Test) results of every strap/divider/FSB/CAS setting combination that our test bench was physically capable of supporting. Using this data, we then developed the method and equation you see above, which can determine whether or not a desired memory subsystem configuration will work. It is possible, and rather probable, that there is another step discontinuity in the logic for FSB speeds in excess of the high value in our test range (466MHz). We will leave the discovery of some such value up to others - unless Intel is kind enough to send us additional 45nm dual-core processors, in which case further testing on our part might be justified.

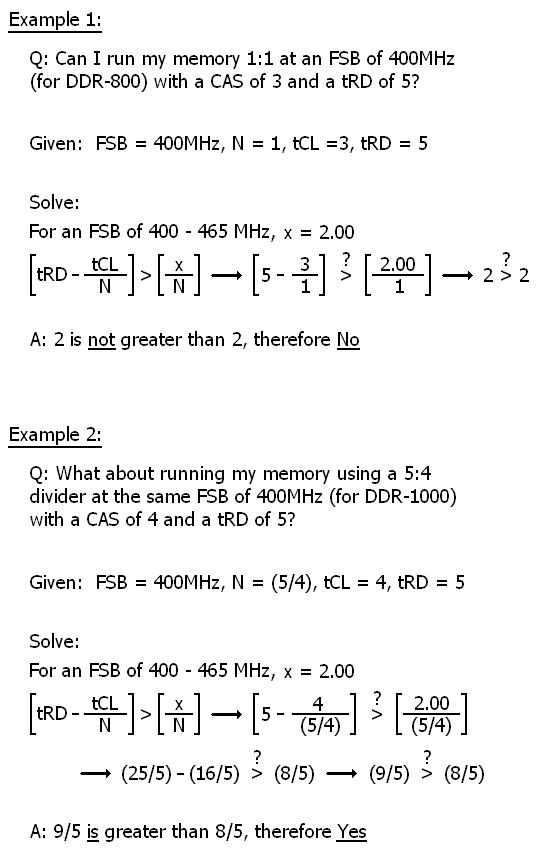

Entering arguments for the use of the "POST Test Equation" are as follows: tRD, in clocks; tCL (CAS), in clocks; FSB, in megahertz (MHz); N, the memory divider in use, expressed in fractional form (i.e. 3:2 would be 3/2); and "x", which should be chosen from the options provided, depending on the FSB in use. Evaluate the left and right side of the equation separately. The expression is satisfied if the left (actual margin) is greater than but not equal to the right (the minimum required margin).

There are no units purposefully associated with these numbers, as this equation is intended as nothing more than a test to determine whether a system will POST using the desired parameters. If the expression is false, the configuration/system will fail to boot; if it is true then the configuration is allowed and the POST event should at least occur. Keep in mind that this equation provides absolutely no assurance that the system will be stable at the settings provided - just because you want to run your memory at DDR2-1200 CAS 3 and the equation says this is possible, does not mean that your wish will be fulfilled. Let's go through a quick exercise of what we have learned regarding the proper use of the "POST Test Equation" with a few practical examples.

If you can follow these examples then you are ready to move on to the next step - determining optimal system performance points and then validating your results. There are many choices when it comes to deciding how to configure a system for the best possible experience. Some choices are clearly better while other decisions may come to down to personal preference. For instance, some users may be willing to subject their expensive hardware components to higher voltages, creating an environment of accelerated wear and earlier failure. Others may be far less concerned with the consequences of their choices; in either case the trade-offs will be clear. We will now take what we have learned and provide our rationale for why we would feel one overclocking approach to be superior to another. After all, overclocking should always be based on an intelligent decision making process and not the clumsy application of brute-force.

73 Comments

View All Comments

dallas - Monday, March 24, 2008 - link

I was wondering how this chipset and Windows Vista 64-bit handles IRQ ? I have a Creative X-fi and it has had a lot of problems with PCI-latency and shared IRQ. According to the manual PCI slot 2 is the only one of the two that does not share IRQ with the graphic cards. Do you guys have any experience of this ?Second question is related also to IRQ. I have a Razer Deathadder mouse which I use at 1000Hz polling rate and it seems to cause quite a bit CPU-usage (average of 10% with AMD64 3500+ when moving mouse at desktop without overlapping anything). I guess it would be ideal to connect it to a USB-port not sharing any IRQ. Rampage Formula has 12 USB-ports total, but reading the manual it says there is USB controllers 1 to 6 and USB 2.0 controllers 1 and 2. How do I relate these figures to the actual layout of the board ? USB controllers 2 and 5 are the only ones not sharing IRQ.

http://dlsvr01.asus.com/pub/ASUS/mb/socket775/Ramp...">http://dlsvr01.asus.com/pub/ASUS/mb/soc...rmula/Ra...

Thanks

nitemareglitch - Friday, March 7, 2008 - link

My older DFI nForce 4 board had fully adjustable tRd among other things. Asus taking a play from their book?rge - Monday, February 18, 2008 - link

Granted I am using gigabyte p35 dq6 board, but I thought loadline simply was a sensor adjustment? Anyone know what is meant by induced power instabilities? measured by?I thought (and may well be wrong) that with loadline disabled, if I choose 1.25v bios as vcore, idle would be 1.23 volts (Voffset), load (dual core) would be 1.22v (Vdroop), when load stops, overshoot to 1.25v before decreasing back to 1.23 idle. Thus when you are choosing 1.25 volts in bios, you are choosing max volts ie, overshoot max, and not idle volts.

I thought loadline was simply a ~.02v sensor calibration, so when enabled, and you choose 1.25 volts in bios, you are then choosing the idle volts (instead of overshoot max) and thus it idles at 1.25V. During load you still see vdroop to 1.24v, and overshoots to 1.27v.

In other words no difference between loadline enabled 1.23v and loadline disabled 1.25v, just personal preference of making bios vcore set idle volts or max overshoot volts.

If I am wrong can someone please inform me what loadline is, and what is meant by power instabilities...mean ?greater fluctuations in volts or what?

Nickel020 - Saturday, February 16, 2008 - link

Firstly, great article! Got me a long way in increasing my memory speed and understanding the underlying factors.What I don't understand though is why the X48 is better than the X38. I already have the option to change tRD on my Gigabyte P35 DQ6, and I'm getting much better memory perfromance after manually setting it to 6.

As I see it, the option to adjust tRD is only a BIOS issue and it can be done on P35 and X38, so how does this make the X48 a better chipset?

kjboughton - Sunday, February 17, 2008 - link

The difference comes in the voltages required to run equivalent speeds/tRD settings. In fact, the X48 board are capable of running stable at much higher speeds, using tigher MCH Read Delay (tRD) values at lower voltages. More to come soon...Holmer - Monday, February 18, 2008 - link

Thanks for an excellent article.I would just love to know how well the Rampage formula handles overclocking with 4x1 GB RAM? How large is the performance hit as compared to 2x2 GB and can it handle 1200 MHz (with two 2x1 GB kits rated at this speed).

Roughly when can we expect the loon awaited X48 roundup?

Thanks a lot on beforehand.

Holmer - Friday, February 22, 2008 - link

Another question: Is is possible to manually set tRFC > 42 in BIOS? If yes what is the maximun value of tRFC?I would be very grateful for an answer.

The Ghost - Saturday, February 2, 2008 - link

With 400Mhz, tRD of 4, CL of 4 and 3:2 ratio I get this:1,334 > 1,333

Is that enough to post or is 0,001 to little to "allowed" ?

Vikendios - Wednesday, January 30, 2008 - link

It's all very fine, but as long as ATI/AMD GPU's are outclassed by Nvidia's, the gamer scene which drives the $300+ motherboard business has little interest in non-Nvidia-SLI solutions. It's bizarre that Intel focuses on chipsets that can apparently only handle well (correct me if I'm wrong) their arch-competitors AMD's GPU's in (Crossfire) arrays.Intel should hurry to develop competitors to 790i that are really neutral as to which twinned or tripled video cards are used.

Gary Key - Wednesday, January 30, 2008 - link

The last time I tested it, X38 ran SLI faster than 680i. The problem is not the chipset, it is simply a decision by NVIDIA (and/or Intel) not to "officially" license SLI on the Intel chipset platforms, except for the upcoming Skulltrail board.This whole SLI/Crossfire debate has gone on long enough, the technologies accomplish the same purpose (are practically identical from a technological viewpoint) and setting up a board/BIOS to run either is actually very easy. CF runs just fine on the NV680i/780i and SLI runs just fine on the 975X/X38/X48 if driver support is present and the proper switches are enabled in the BIOS. Personally, I would like to have the ability to run (unhindered) AMD or NVIDIA GPUs in multi-GPU configurations on either chipset platform. I just wish they would let the market determine the best multi-GPU solution, but that is pie in the sky thinking. ;)