The Era of Tera: Intel Reveals more about 80-core CPU

by Anand Lal Shimpi on February 11, 2007 5:44 PM EST- Posted in

- CPUs

Clocks and Power Management

In a modern day microprocessor, making sure the clock signal arrives at the same time across all parts of the chip can be a difficult task for a designer, especially as CPU frequencies and chip area both increase. However it's a necessary part of chip design as the clock needs to arrive at all parts of the chip within tight parameters in order for the CPU to behave normally. Intel tells us that in modern day microprocessors, clock distribution is responsible for approximately 30% of a chip's total power consumption and thus any power savings you can make here will be significant.

The teraflop chip however isn't a conventional chip; as each tile is independent, the clock only needs to arrive to all parts of a 3mm^2 tile at the same time, not to the entire 275mm^2 chip. With this in mind, Intel designed the teraflop chip to allow for the clock to arrive at individual tiles out of phase. This approach means that tile-to-tile communication may end up being a bit slower than it could, but the power savings are tremendous. Intel estimates at the power required to distribute the clock to all of the tiles on the teraflop chip at 4GHz is 2.2W, or 1.2% of total power consumption under load.

Obviously if we had a network of more complicated cores, distributing the clock within a larger more complex tile would require more power than this, but the take away point is that in a network like this you can simplify overall chip clock distribution by only worrying about the clock within a tile.

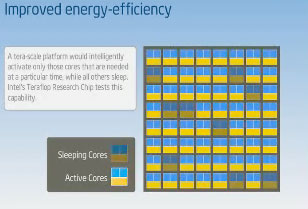

Clock management isn't the only area where Intel looked to save power, as the teraflop chip architecture is very power conscious in its design. Each tile is divided up into 21 individual sleep regions that can be powered down independently depending on the type of instruction being executed, not to mention that individual tiles can be powered down independently of one another. And as we mentioned before, the PE and router on each tile can be powered down independently.

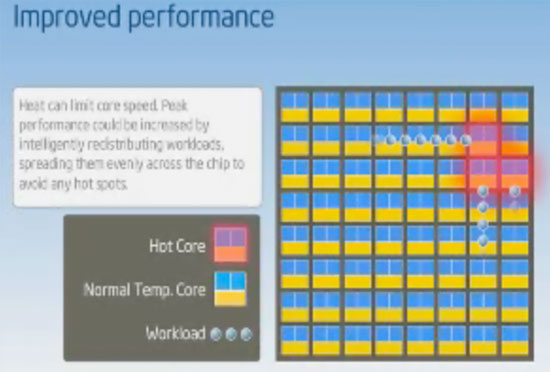

Within the router itself, each one of the five ports can be powered down independently as well. With 80 cores, the teraflop chip can also redistribute load according to thermal needs. If a handful of tiles are getting too hot, the chip can dynamically wake up a different set of tiles to begin working in order to avoid creating hotspots.

The FPMACs remain in sleep mode until they are needed, so there's an additional latency penalty when waking them up but it prevents power consumption from spiking as soon as there's load which can help simplify power delivery and other elements of the chip as well. Approximately 90% of the FPMAC logic and a total of 74% of each PE uses sleep transistors to help reduce power consumption as we described above. Intel states that sleep transistors take up, on average, 5.4% more die area than regular transistors and come with a 4% frequency penalty, but the power savings are worth it. Sleep transistors are used in other Intel processors, including the Core 2 family.

25 Comments

View All Comments

Navitron - Monday, February 12, 2007 - link

In the words of bill gates "No one will need more than 637 kb of memory for a personal computer." You sound just like him :P Don't bash the technology just because "right now" we don't need it. But what about in 10-20 years, you still think your core 2 duo is gonna cut it in 15 years? Can a IBM 80386 run doom 3? will todays AMD and Intels run -insert game here- 10 years from now.So don't assume just because we don't need it now doesn't mean we wont need it in 3 years.

cscpianoman - Sunday, February 11, 2007 - link

The average consumer might not need it, but large industries will be grabbing at these things faster than you can imagine. Think of health care, for example, the trend is to move towards genetic manipulations/prescreening. These industries want to download a person's entire genetic information, process it, and return it to you with the results of Alzhiemer's, cancer, and heart problems in a matter of minutes. Furthermore, the entertainment industry would love to create more special effects and render them that much faster. I'm sure if they could Pixar would already be placing an order for these. There are hundreds of applications out there that require the power and capability of multi-cores. Sure the consumer may not need it, but the consumer only accounts for less than approx. 5% of what Intel, AMD or whoever makes.mino - Sunday, February 11, 2007 - link

They need it (to sell). Period.Justin Case - Sunday, February 11, 2007 - link

In other words, Intel is doing the same that IBM and AMD (with Cell and Torrenza + Fusion), only with some made-up numbers and more Powerpoint charts. Unless they vastly improve their compilers' paralellization, or come up with a full suite of software optimized for multi-core chips (80? It's hard enough to take full advantage of 4!), this will remain something that "can be done", but which most people will have no use for.joex444 - Sunday, February 11, 2007 - link

attack switch