Intel Unveils Meteor Lake Architecture: Intel 4 Heralds the Disaggregated Future of Mobile CPUs

by Gavin Bonshor on September 19, 2023 11:35 AM ESTGraphics Tile: A Generational Leap Through Arc, Xe-LPG Graphics

As part of their disaggregated architecture for Meteor Lake, Intel has opted to use a separate tile for graphics. Intel has gone down an interesting route for its disaggregated graphics, with the most notable inclusion through an upgrade to Intel's Arc Graphics architecture. Powering Intel's integrated graphics for Meteor Lake is a new graphics architecture which Intel calls Xe-LPG (and no, we're not talking about fuel here). Based on Intel's current discrete graphics architecture known as Xe-HPG (used in their Arc GPUs), Intel claims 2x performance per watt compared to the Xe-LP architecture-based Iris Xe integrated graphics within Intel's 12th Gen Core series.

There are a number of different elements within the graphics and media area of Meteor Lake, the bulk of which is built into the graphics tile, where the Xe-LPG graphics architecture is located. Unlike the compute tile (Intel 4) and the SoC tile, which is manufactured on TSMC N6 (6 nm), the graphics tile is made on TSMC's N5 node (5 nm), the same generational family as the nodes used by AMD and NVIDIA's discrete and integrated GPUs.

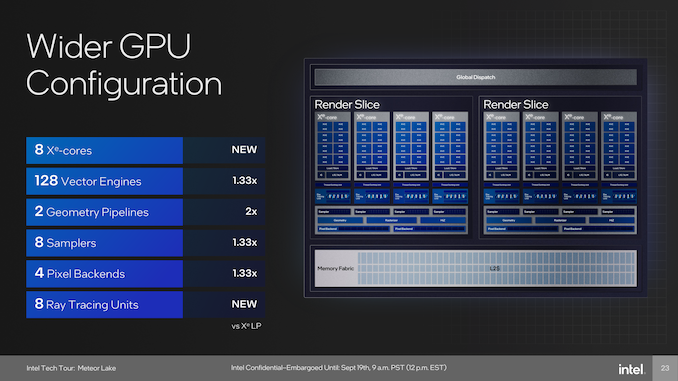

With Meteor Lake and the graphics tile with the Xe-LPG graphics processor, Intel is promising discrete-level performance in an integrated form factor. Looking at the finer specifications, Intel includes 8 x Xe graphics cores with 128 vector engines (12 per Xe core) and 8 samplers, representing a 1.33 x increase over Intel's previous Xe LP graphics. There are also 4 Pixel backends, which is an improvement over the 3 PBs on Xe LP. Intel also doubles the number of geometry pipelines within Xe-LPG, with two, and they also introduce 8 dedicated Ray Tracing Units (RTU), which is new for Intel's integrated graphics line-up.

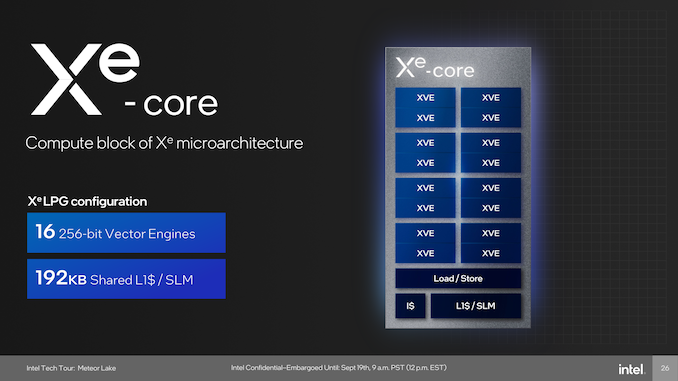

Looking at the makeup of Intel's Xe core, as previously mentioned, there are 16 Vector Engines that have a bus width of 256-bit, while each core also has 192 KB of shared L1 cache. Each Vector Engine enables 16 FP32 ops per clock, and 32 FP16 ops per clock, with a shared FP64 execution port with 64 INT8 ops per clock. One dedicated FP64 ops per clock unit is new over what's previously been seen in Raptor Lake and shares the overall design philosophy of Meteor Lake on power efficiency; pairs of Vector Engines can run in lockstep for better efficiency.

As part of Intel's goal of advancing the overall experience with Xe-LPG for users, the graphics are DX12 optimized, and Intel now brings Out of Order Samplng (OoOS) to Xe-LPG. It's worth noting that when talking about Execution Units (EUs), Intel's new and current term for this is Xe Vector Engines, or XVE for short. Intel hasn't provided us with how OoOS works within Xe-LPG, but we've reached out for more details.

| Comparing Intel Xe Integrated Graphics (Mobile) | ||||

| Meteor Lake (Xe-LPG) |

Raptor Lake (Xe-LP) |

Alder Lake GT1 (Xe-LP) |

Tiger Lake GT2 (Xe-LP) |

|

| Process Node | TSMC N5 | Intel 7 | Intel 7 | Intel 7 |

| Vector Engines/EUs | 128 | 96 | 96 | 96 |

| ALUs/Shaders | 1024 | 768 | 768 | 768 |

| TMUs | ?* | 48 | 16 | 48 |

| ROPs | ?* | 24 | 8 | 24 |

| Ray Tracing Units | 8 | - | - | - |

| TDP | ? | 15 W | 15 W | 15 W |

*Intel hasn't given us a deep dive into the finer specifications of Xe-LPG integrated graphics. Looking at an existing integrated Intel Arc equivalent with similar specs, the Meteor Lake Xe LPG could have 64 TMUs and 32 ROPs per the Arc A370M, which also has 1024 ALUs.

Comparing Intel's integrated Xe graphics from previous mobile architectures, Meteor Lake, through the Xe-LPG Arc based graphics, has 128 XVEs, which is an increase of 1.33 X or 32 XVE/EUs, than the previous Xe-LP generation. Regarding arithmetic logic units (ALUs), which are essentially shader cores, Xe-LPG has been increased to 1024, which is 128 ALUs per Xe-LPG core. As previously mentioned, Intel hasn't given us more about the finer specifications, including TMUs or ROPs, but does bring 8 Ray Tracing units, which is new for Xe-LPG when compared directly to Xe-LP.

Meanwhile, with Intel's Foveros 3D packaging technology, disaggregating the Media Engine and Display Engine from the graphics tile means when doing encoding or decoding, as well as video playback, it doesn't require the graphics tile to be powered up to do workloads on more power consuming cores.

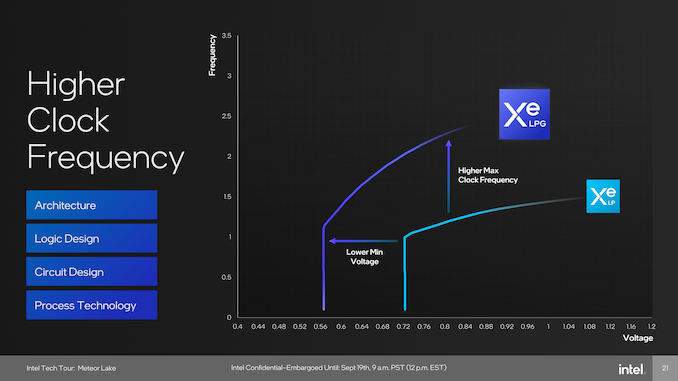

Intel Xe-LPG is the next step up from Xe LP, and one area where performance and efficiency gains are made is through a lower voltage frequency (V/F) curve, allowing the graphics to run at a lower minimum voltage with a higher maximum core clock speed. Intel has also optimized the pipelines for faster frequencies and is claiming up to 2 x performance at iso-voltages, which for a mobile platform such as Meteor Lake, adds more potential with a key focus on achieving a figure of up to 20% in power savings compared to the previous generation.

107 Comments

View All Comments

tipoo - Tuesday, September 19, 2023 - link

Is anyone at AT planning on deep diving the A17 Pro?Ryan Smith - Tuesday, September 19, 2023 - link

At the moment, no. I do not have a mobile editor to work on such projects.FWhitTrampoline - Tuesday, September 19, 2023 - link

Oh no that's bad news as Apple appears to have gone even wider with the A17 P cores than even the A14/Firestorm with decode resources on A17/P core, if the Apple promotional material is correct!Maybe Chipsandcheese will look at A17's P core design and with some Micro-benchmarks as well.

tipoo - Tuesday, September 19, 2023 - link

Yeah that's too bad, it looks like the e-cores got a bigger bump than the p-cores but they didn't advertise it with how strangely they mentioned itFWhitTrampoline - Wednesday, September 20, 2023 - link

The slide from Intel on its Crestmont E core design(Block Diagram) does not look that much different from Gracemont's block diagram and Redwood Cove(Block Diagram) core design still appears to be a 6 wide Instruction Decoder design and so Similar to Golden Cove but there needs to be more info concerning Micro-Op issue rates and other parts of Redwood Cove's core design.GeoffreyA - Thursday, September 21, 2023 - link

It's hard to see the instruction decoders being increased all that much, because of their power burden in x86.ikjadoon - Tuesday, September 19, 2023 - link

>As expected, Meteor Lake brings generational IPC gains through the new Redwood Cove cores.Redwood Cove does not have any IPC gain, I believe. Is there a citation or slide regarding this?

This will be now the third Intel CPU generation with 0% to 1% IPC gains in their P-cores.

Gavin Bonshor - Tuesday, September 19, 2023 - link

Intel confirmed to me Redwood Cove would have IP gains over Raptor Cove. When I get back (been sat at a PC a lot the last few days), I'll grab it for youkwohlt - Tuesday, September 19, 2023 - link

There's so many changes in MTL, it would make sense to just save a new P core uArch for next gen. Especially when clockspeed/watt is going up a decent amount, so it's not like perf/watt is stagnating.GeoffreyA - Thursday, September 21, 2023 - link

I think they've been following the old tick-tock system, Sunny and Golden Cove being the tocks, and Willow and Raptor the ticks. So, it's possible that Redwood would bring some proper changes.