AMD Zen 4 Ryzen 9 7950X and Ryzen 5 7600X Review: Retaking The High-End

by Ryan Smith & Gavin Bonshor on September 26, 2022 9:00 AM ESTZen 4 Execution Pipeline: Familiar Pipes With More Caching

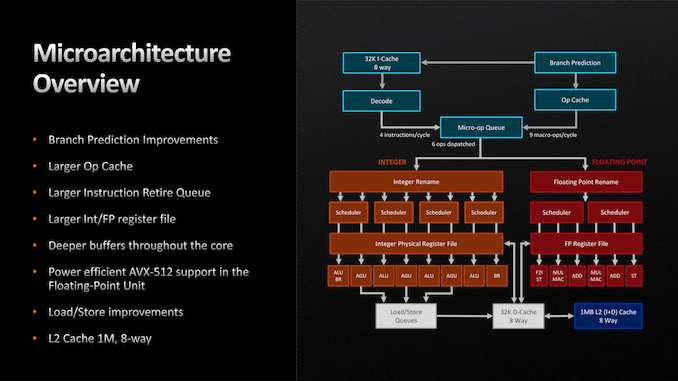

Finally, let’s take a look at the Zen 4 microarchitecture’s execution flow in-depth. As we noted before, AMD is seeing a 13% IPC improvement over Zen 3. So how did they do it?

Throughout the Zen 4 architecture, there is not any single radical change. Zen 4 does make a few notable changes, but the basics of the instruction flow are unchanged, especially on the back-end execution pipelines. Rather, many (if not most) of the IPC improvements in Zen 4 come from improving cache and buffer sizes in some respect.

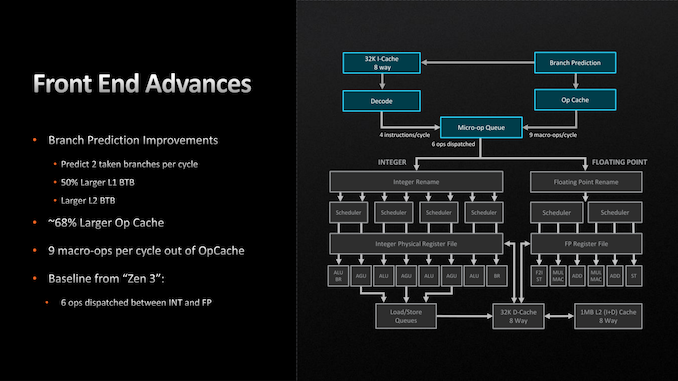

Starting with the front end, AMD has made a few important improvements here. The branch predictor, a common target for improvements given the payoffs of correct predictions, has been further iterated upon for Zen 4. While still predicting 2 branches per cycle (the same as Zen 3), AMD has increased the L1 Branch Target Buffer (BTB) cache size by 50%, to 2 x 1.5k entries. And similarly, the L2 BTB has been increased to 2 x 7k entries (though this is just an ~8% capacity increase). The net result being that the branch predictor’s accuracy is improved by being able to look over a longer history of branch targets.

Meanwhile the branch predictor’s op cache has been more significantly improved. The op cache is not only 68% larger than before (now storing 6.75k ops), but it can now spit out up to 9 macro-ops per cycle, up from 6 on Zen 3. So in scenarios where the branch predictor is doing especially well at its job and the micro-op queue can consume additional instructions, it’s possible to get up to 50% more ops out of the op cache. Besides the performance improvement, this has a positive benefit to power efficiency since tapping cached ops requires a lot less power than decoding new ones.

With that said, the output of the micro-op queue itself has not changed. The final stage of the front-end can still only spit out 6 micro-ops per clock, so the improved op cache transfer rate is only particularly useful in scenarios where the micro-op queue would otherwise be running low on ops to dispatch.

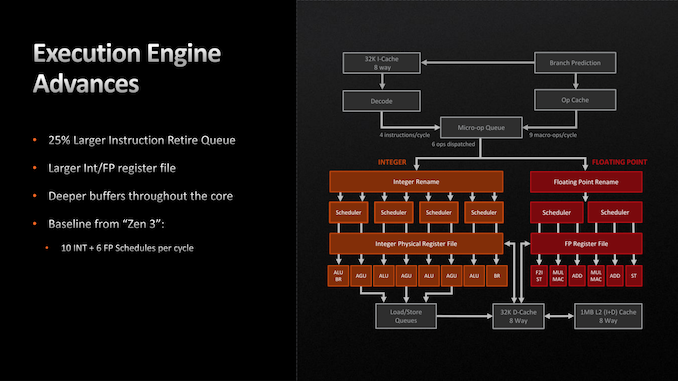

Switching to the back-end of the Zen 4 execution pipeline, things are once again relatively unchanged. There are no pipeline or port changes to speak of; Zen 4 still can (only) schedule up to 10 Integer and 6 Floating Point operations per clock. Similarly, the fundamental floating point op latency rates remain unchanged as 3 cycles for FADD and FMUL, and 4 cycles for FMA.

Instead, AMD’s improvements to the back-end of Zen 4 have here too focused on larger caches and buffers. Of note, the retire queue/reorder buffer is 25% larger, and is now 320 instructions deep, giving the CPU a wider window of instructions to look through to extract performance via out-of-order execution. Similarly, the Integer and FP register files have been increased in size by about 20% each, to 224 registers and 192 registers respectively, in order to accommodate the larger number of instructions that are now in flight.

The only other notable change here is AVX-512 support, which we touched upon earlier. AVX execution takes place in AMD’s floating point ports, and as such, those have been beefed up to support the new instructions.

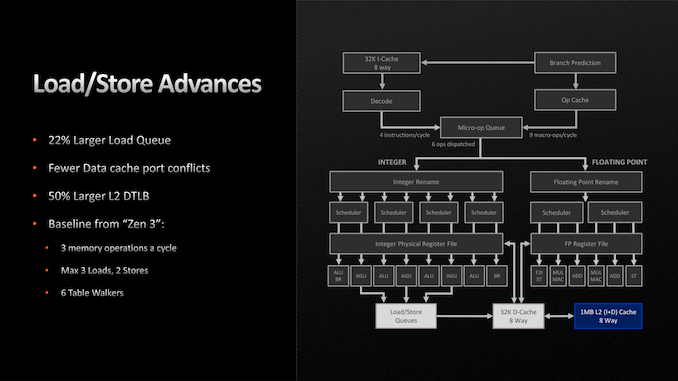

Moving on, the load/store units within each CPU core have also been given a buffer enlargement. The load queue is 22% deeper, now storing 88 loads. And according to AMD, they’ve made some unspecified changes to reduce port conflicts with their L1 data cache. Otherwise the load/store throughput remains unchanged at 3 loads and 2 stores per cycle.

Finally, let’s talk about AMD’s L2 cache. As previously disclosed by the company, the Zen 4 architecture is doubling the size of the L2 cache on each CPU core, taking it from 512KB to a full 1MB. As with AMD’s lower-level buffer improvements, the larger L2 cache is designed to further improve performance/IPC by keeping more relevant data closer to the CPU cores, as opposed to ending up in the L3 cache, or worse, main memory. Beyond that, the L3 cache remains unchanged at 32MB for an 8 core CCX, functioning as a victim cache for each CPU core’s L2 cache.

All told, we aren’t seeing very many major changes in the Zen 4 execution pipeline, and that’s okay. Increasing cache and buffer sizes is another tried and true way to improve the performance of an architecture by keeping an existing design filled and working more often, and that’s what AMD has opted to do for Zen 4. Especially coming in conjunction with the jump from TSMC 7nm to 5nm and the resulting increase in transistor budget, this is good way to put those additional transistors to good use while AMD works on a more significant overhaul to the Zen architecture for Zen 5.

205 Comments

View All Comments

Freeb!rd - Monday, September 26, 2022 - link

This paragraph reads like someone having a stroke while writing it..."Although this is overridable through manually overclocking with a maximum TJ Max of up to 115°C, it’s key tovitalte that users will need to use more premium and aggressive cooling types to squeeze every last drop of performance from ZAMD intended thistended when designing Zen 4, and as such, has opted not to bundls own CPU coolers with the retail packages."

and someone's spell checker is broken. Reply

gryer7421 - Monday, September 26, 2022 - link

It reads like a GTP-3 BOT .... :( ReplyThreska - Monday, September 26, 2022 - link

We now know "Zencally " is a word. ReplyGavin Bonshor - Monday, September 26, 2022 - link

Hi, yeah something screwy happened, but it's fixed now. Apologies. I think it may be time to update to a new system, and software. This isn't the first time it's jumbled stuff up for me. ReplyCow86 - Monday, September 26, 2022 - link

I wish I could say that all the errors in the article are fixed, but that very paragraph even still has several (big) errors in it... A missing letter is one thing, half a sentence just missing and going into the next is another. Replyherozeros - Monday, September 26, 2022 - link

Keep the copy editor awake, or fire them. Grammar/syntax/CMS error, it doesn't matter if it gives me a headache reading this. ReplyRyan Smith - Monday, September 26, 2022 - link

Unfortunately we're having to do this kind of live. It's been a very busy past two weeks and we haven't had as much time to prepare as we like. So most of what you're seeing is first-draft copy, which I'll get around to editing as I can.Digital publications do not employ dedicated copy editors any more. They have all been let go for cost efficiency reasons. Reply

flyingpants265 - Monday, September 26, 2022 - link

What? Come on now. ReplyHifihedgehog - Monday, September 26, 2022 - link

@flypants265: It's kind of like Microsoft who got rid of their QA team and made all of their developers honorary QA tests. They can't help it that their leadership is being stupid. Don't blame Ryan or Gavin. Blame these greedy cheapskates that likewise didn't want to pay Ian Cutress enough to want to stay. ReplyHifihedgehog - Monday, September 26, 2022 - link

*QA testers Reply