The Intel 12th Gen Core i9-12900K Review: Hybrid Performance Brings Hybrid Complexity

by Dr. Ian Cutress & Andrei Frumusanu on November 4, 2021 9:00 AM ESTCPU Tests: SPEC ST Performance on P-Cores & E-Cores

SPEC2017 is a series of standardized tests used to probe the overall performance between different systems, different architectures, different microarchitectures, and setups. The code has to be compiled, and then the results can be submitted to an online database for comparison. It covers a range of integer and floating point workloads, and can be very optimized for each CPU, so it is important to check how the benchmarks are being compiled and run.

For compilers, we use LLVM both for C/C++ and Fortan tests, and for Fortran we’re using the Flang compiler. The rationale of using LLVM over GCC is better cross-platform comparisons to platforms that have only have LLVM support and future articles where we’ll investigate this aspect more. We’re not considering closed-sourced compilers such as MSVC or ICC.

clang version 10.0.0

clang version 7.0.1 (ssh://git@github.com/flang-compiler/flang-driver.git

24bd54da5c41af04838bbe7b68f830840d47fc03)

-Ofast -fomit-frame-pointer

-march=x86-64

-mtune=core-avx2

-mfma -mavx -mavx2

Our compiler flags are straightforward, with basic –Ofast and relevant ISA switches to allow for AVX2 instructions. We decided to build our SPEC binaries on AVX2, which puts a limit on Haswell as how old we can go before the testing will fall over. This also means we don’t have AVX512 binaries, primarily because in order to get the best performance, the AVX-512 intrinsic should be packed by a proper expert, as with our AVX-512 benchmark. All of the major vendors, AMD, Intel, and Arm, all support the way in which we are testing SPEC.

To note, the requirements for the SPEC licence state that any benchmark results from SPEC have to be labeled ‘estimated’ until they are verified on the SPEC website as a meaningful representation of the expected performance. This is most often done by the big companies and OEMs to showcase performance to customers, however is quite over the top for what we do as reviewers.

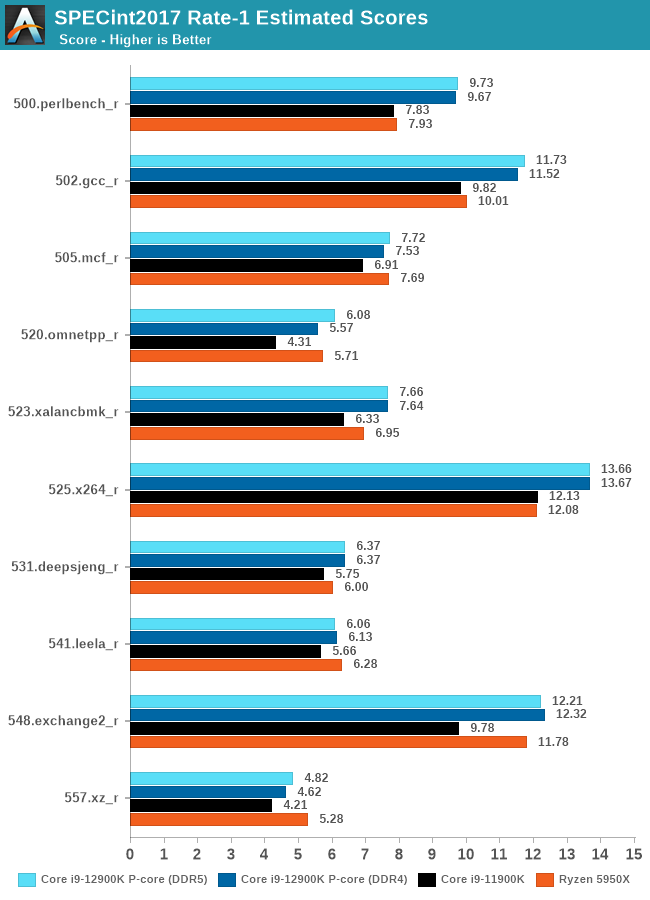

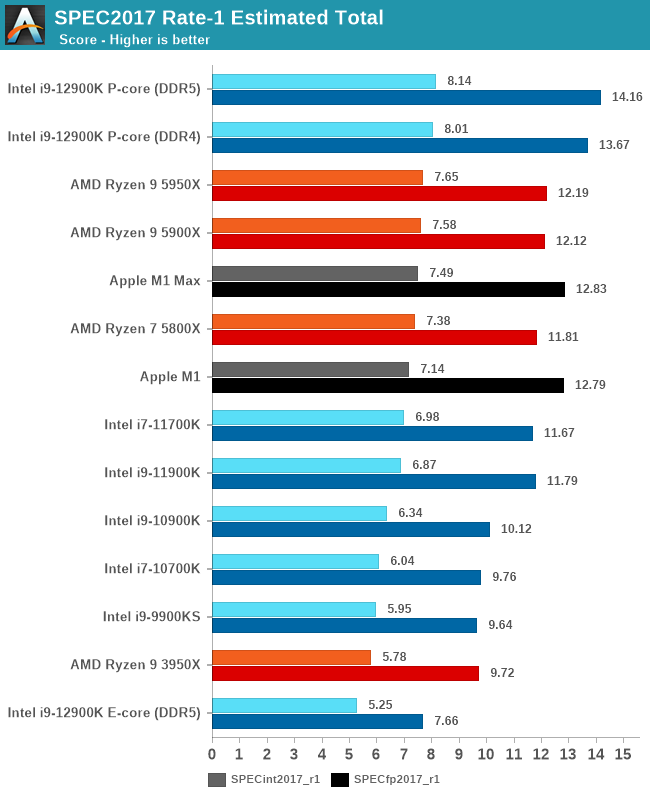

For Alder Lake, we start off with a comparison of the Golden Cove cores, both in DDR5 as well as DDR4 variants. We’re pitting them as direct comparison against Rocket Lake’s Cypress Cove cores, as well as AMD’s Zen3.

Starting off in SPECint2017, the first thing I’d say is that for single-thread workloads, it seems that DDR5 doesn’t showcase any major improvements over DDR4. The biggest increase for the Golden Cove cores are in 520.omnetpp_r at 9.2% - the workload is defined by sparse memory accessing in a parallel way, so DDR5’s doubled up channel count here is likely what’s affecting the test the most.

Comparing the DDR5 results against RKL’s WLC cores, ADL’s GLC showcases some large advantages in several workloads: 24% in perlbench, +29% in omnetpp, +21% in xalancbmk, and +26% in exchange2 – all of the workloads here are likely boosted by the new core’s larger out of order window which has grown to up to 512 instructions. Perlbench is more heavily instruction pressure biased, at least compared to other workloads in the suite, so the new 6-wide decoder also likely is a big reason we see such a large increase.

The smallest increases are in mcf, which is more pure memory latency bound, and deepsjeng and leela, the latter which is particularly branch mispredict heavy. Whilst Golden Cove improves its branch predictors, the core also had to add an additional cycle of misprediction penalty, so the relative smaller increases here make sense with that as a context.

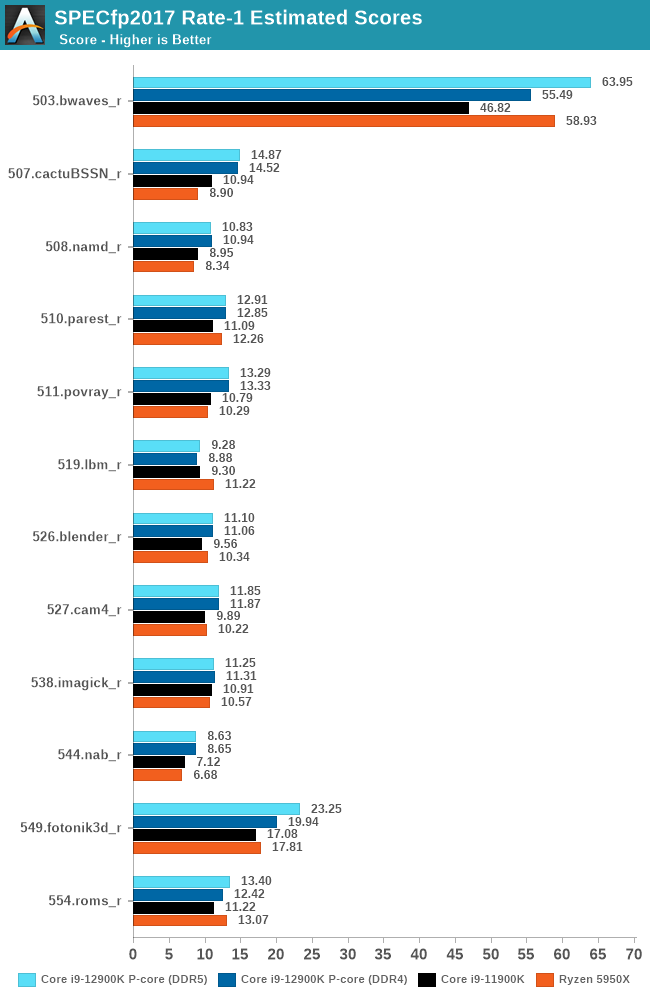

In the FP suite, the DDR5 results have a few larger outliers compared to the DDR4 set, bwaves and fotonik3d showcase +15% and +17% just due to the memory change, which is no surprise given both workloads extremely heavy memory bandwidth characteristic.

Compared to RKL, ADL showcases also some very large gains in some of the workloads, +33% in cactuBBSN, +24% in povray. The latter is a surprise to me as it should be a more execution-bound workload, so maybe the new added FADD units of the cores are coming into play here.

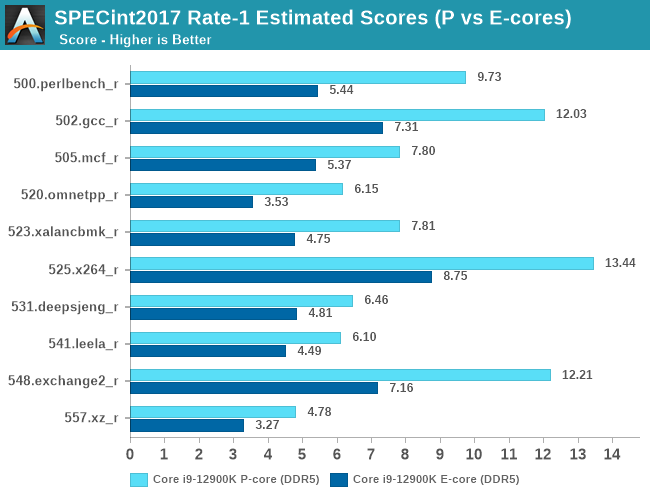

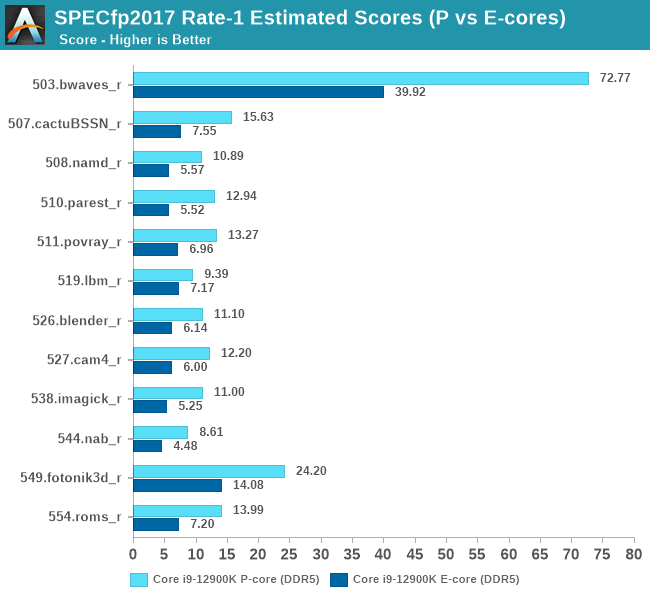

We’ve had not too much time to test out the Gracemont cores in isolation, but we are able to showcase some results. This set here is done on native Linux rather than WSL due to affinity issues on Windows, the results are within margin of error between the platforms, however there are a few % points outliers on the FP suite. Still, comparing the P to E-cores are in apples-to-apples conditions in these set of graphs:

When Intel mentioned that the Gracemont E-cores of Alder Lake were matching the ST performance of the original Skylake, Intel was very much correct in that description. Unlike what we consider “little” cores in a normal big.LITTLE setup, the E-cores of Alder Lake are still quite performant.

In the aggregate scores, an E-core is roughly 54-64% of a P-core, however this percentage can go as high as 65-73%. Given the die size differences between the two microarchitectures, and the fact that in multi-threaded scenarios the P-cores would normally have to clock down anyway because of power limits, it’s pretty evident how Intel’s setup with efficiency and density cores allows for much higher performance within a given die size and power envelope.

In SPEC, in terms of package power, the P-cores averaged 25.3W in the integer suite and 29.2W in the FP suite, in contrast to respectively 10.7W and 11.5W for the E-cores, both under single-threaded scenarios. Idle package power ran in at 1.9W.

Alder Lake and the Golden Cove cores are able to reclaim the single-threaded performance crown from AMD and Apple. The increases over Rocket Lake come in at +18-20%, and Intel’s advantage over AMD is now at 6.4% and 16.1% depending on the suite, maybe closer than what Intel would have liked given V-cache variants of Zen3 are just a few months away.

Again, the E-core performance of ADL is impressive, while not extraordinary ahead in the FP suite, they can match the performance of some middle-stack Zen2 CPUs from only a couple of years ago in the integer suite.

474 Comments

View All Comments

Wrs - Saturday, November 6, 2021 - link

Nah, they just weren't that competitive. Athlon64 was decent (lot of credit to Jim Keller) but didn't let AMD take massive advantage of Intel's weakness during the Pentium 4 era because AMD fabs were capacity limited. Once Conroe came out mid 2006 the margins dried up rapidly and AMD had no good response and suffered a talent exodus. It's true Intel made it worse with exclusivity bonuses, but I think AMD's spiral toward selling their fabs would have happened anyway. No way they were going to catch up with tick-tock and Intel's wallet.GeoffreyA - Monday, November 8, 2021 - link

I've always felt the K10 wasn't aggressive enough, owing to AMD not having factored Conroe into their equations when K10 was designed. Then, like startled folk, they tried to take back the lead by a drastic departure in the form of Bulldozer; and that, as we know, sank them into the ditch. Nonetheless, I'm glad they went through the pain of Bulldozer: Zen wouldn't have been as good otherwise.mode_13h - Tuesday, November 9, 2021 - link

> FX series was as bad as it was for a couple of reasonsI thought I also heard they switched from full-custom layout to ASIC flow (maybe for the sake of APUs?). If so, that definitely left some performance on the table.

bunnyfubbles - Thursday, November 4, 2021 - link

3D v-cache will be out before Zen 4 and should help close the gap if not regain the overall lead on the high end. The problem for AMD is the competition below the i9 vs R9 realm, where the E cores really pull more than their weight and help the i9 compete with the R9s in multi, but for the i5s and i7s vs their R5 and R7 counterparts, its even-Steven with performance cores, then you have the E cores as the trump card.MDD1963 - Thursday, November 4, 2021 - link

If AMD gains an averge of ~10% in gaming FPS with the 3D cache onslaught, that should put them right back near the top...certainly much closer to the 12900K....geoxile - Thursday, November 4, 2021 - link

15% on average. 25% at the highest. Intel really should have offered a 16 P-core die for desktop smdh, classic intel blunderSpunjji - Friday, November 5, 2021 - link

That would be a hell of a large die and necessitate a total redesign of the on-chip fabric. I don't think it would really make any sense at all.RSAUser - Monday, November 8, 2021 - link

12900K is already huge, each performance core is the size of about 4 E cores, going 16C P-Core would probably mean a 70% die size increase, and then you run into core to core communication issues, AMD got around it with infinity fabric but that's why you have the higher latency access between cores in different core complexes and Intel gives a more consistent access time on higher end products. Intel's current cores are mosly ringbus, so travel from one core to the next, getting to 16 doesn't scale well, they used a mesh topology in some Skylake CPU's, that latency was too high and hampered performance badly, you'd run into that same issue with 16C.That's without checking into yield, getting 16C on one wafer that are all perfectly clocking high is going to be a very, very rare chip; AMD gets around it using the core complexes (CX) of 4 cores each, together into a CCD (core chiplet die) and then in Zen 3 (5000 series) is supposedly 8C CCX, which makes rare chips 8C if full ccx works well, else 6C if 2 can't make it turns into a 5600X.

StevoLincolnite - Friday, November 5, 2021 - link

AMD has an answer before Zen 4.And that is Zen 3 with V-Cache.

Spunjji - Friday, November 5, 2021 - link

"This is their Zen 1 moment"Indeed!

"at a lower price"

Not really, if you take platform into account (and you have to!)

"Zen 4 isnt even competing with Alder Lake, Raptor Lake is rumored to be out before Zen 4"

Potentially, but Zen 4 is a bigger jump from Zen 3 than Raptor is predicted to be from Alder. Raptor will have more E cores but it's on the same process, so it's likely to offer better perf/watt in multithreading but unlikely to increase overall performance substantially (unless they allow maximum power draw to increase).

"AMD has really screwed up with their launch cycle"

Not really? They're still competitive in both price/performance (accounting for platform cost) and perf/watt. Zen 3D should shore up that position well enough.

"Intel is truly back"

Yup!