Arm Announces Mobile Armv9 CPU Microarchitectures: Cortex-X2, Cortex-A710 & Cortex-A510

by Andrei Frumusanu on May 25, 2021 9:00 AM EST- Posted in

- SoCs

- CPUs

- Arm

- Smartphones

- Mobile

- Cortex

- ARMv9

- Cortex-X2

- Cortex-A710

- Cortex-A510

Conclusion & First Impressions

Today’s Arm Client TechDay disclosures were generally quite a lot more extensive than in the last few years, especially given the number of new IP releases we’ve covered. Three new CPU microarchitectures, a new DSU/L3 cluster design, and two new SoC interconnect IPs is quite a bit more than we’re used to, and it goes to underscore just how much effort Arm is putting into updating all of the parts of its client IP.

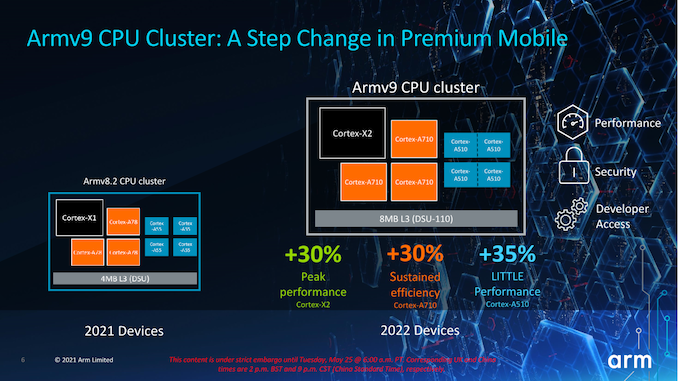

Starting off with the CPUs, the new Cortex-X2 and Cortex-A710 cores are meant to be iterative designs compared to their predecessors, and that's certainly what they are from a performance and efficiency viewpoint. On a generational basis, Arm is promising a 10-16% improvement in IPC. However these figures are somewhat muddled by the fact we’re also comparing 4MB and 8MB L3 caches. Generally, it’s a reasonable expectation of what we’ll be seeing in 2022 devices, but it’s also hard to disambiguate and attribute the performance of the cores versus that of the new DSU-110 L3 cluster design.

Arm has also made some more lofty performance claims when it comes to actual device implementations in 2022, such as +30% peak-to-peak performance boosts on the parts of the X2 cores. Generally, given our expectations that both the next Snapdragon and the next Exynos flagships will come in a similar Samsung foundry process node with smaller improvements, I’m very doubtful we’ll be seeing such larger generational improvements in practice, unless somehow MediaTek surprises us with a flagship X2 SoC made out at TSMC.

While the X2 and A710 aren’t all that groundbreaking, we have to note that the move towards Armv9 brings a lot of new architectural features that would otherwise eat into the expected yearly performance or efficiency improvements. The move to the new ISA baseline has been a long time coming and I’m curious to see what it will enable in terms of media applications (SVE) or AI (new ML instructions).

This is also the fourth and last iteration of Arm’s Austin core family, so hopefully next year’s new Sophia family will see larger generational leaps. Arm admits that we’re nearing diminishing returns and it’s certainly not at the same break-neck pace it was moving a few years ago, but there’s still a lot which can be done.

Today we also saw the unveiling of a brand-new little core in the form of the Cortex-A510. A new clean-sheet design from the Cambridge team, it’s certainly using an innovative approach given its “merged core” design, sharing the L2 cache hierarchy and the FP/SIMD back-end amongst two otherwise full featured cores. The performance and IPC gains are claimed to be quite large at +35-50%, however it seems that this generation hasn’t improved the efficiency curve all that much. It’s still a much better design and will have effective benefits for power efficiency in real-world workloads due to how workloads interact between the little and larger cores, but leaves us with a feeling that it doesn’t provide a knock-out convincing jump we had expected after 4 years. The silver lining here is that Arm is promising further generational improvements in performance and power with subsequent iterations, so we won’t be left with the current state of affairs the same way we saw the Cortex-A55 stagnate.

One of the more key points I saw Arm put their focus on was the new possibilities in larger form-factor devices beyond mobile. The new DSU-110 now supports up to 8 Cortex-X2 cores, a theoretical setup that would pretty much blow away the current Cortex-A76 based Arm laptop SoCs such as the Snapdragon 8cx family. The new cluster design allows for large L3 caches of up to 16MB, and while I don’t know if we’ll see the new interconnect IPs used by the larger vendors, it surely also makes a big argument for larger performance designs. The catch is that if Qualcomm were to adopt and make such a design, it would seemingly be short-lived given their recent Nuvia acquisition and intent on using custom cores. Otherwise, because of a lack of Mali Windows drivers, this really only leaves space for a theoretical Samsung laptop SoC with AMD RDNA GPU, but such a SoC could nonetheless be very successful.

Overall, this year’s CPU and system IP announcements from Arm are extremely solid new IP offerings, really laying down a new foundation, both architecturally with Armv9, and microarchitecturally thanks to elements such as the new DSU and the new little core CPUs. We’re looking forward to the new 2022 SoCs and products that will be powered by the new Arm IP.

181 Comments

View All Comments

Thala - Tuesday, May 25, 2021 - link

You compare only peak performance. ARM has demonstrated that SVE2 can have big advantages over NEON, in particular for computational kernel, which does not parallelize well for NEON.WorBlux - Thursday, May 27, 2021 - link

>If they are sticking with in-order, I hoped the A510 could’ve done something more over four years.In order is hard. The A55 was pretty cool in allowing certain instruction dependencies to be issued together. The traditional way to get more IPC out of in-order is VLIW, but would require an ABI break or at least a special sort of compiler optimization and quasi-long-words that in the end wouldn't do any better than the A55/A510 on legacy and non-optimized code.

mode_13h - Tuesday, May 25, 2021 - link

x86 is indeed on the way out, but your analysis is too facile.SarahKerrigan - Tuesday, May 25, 2021 - link

Essentially agreed.yeeeeman - Tuesday, May 25, 2021 - link

x86 maybe dead if you don't understand how and why things stand like they do.First of all, Apple is in a very very special situation where they control everything. Hardware, software, product. Plus they use the best process there is at the moment. All of this, contributes to their results. Which are very good, but they stem from what I told you.

Now, a better picture of what ARM is actually capable of in ... real life is the snapdragon 8cx, which for all intents and purposes is still alive only because qualcomm has a ton of money and can throw it away for projects that don't really sell.

Apple is using just ARM ISA. If Apple has great performance and great efficiency, it doesn't mean automatically that ARM and the companies that work with them will also reach that point. The truth is, Apple has put a LOT of money and R&D and got the best talents there are to get where they are today. Their cores are not exactly suited for the plethora of android devices that range from 50 bucks to 2000+.

Now, regarding x86, if you compare amd's zen 3 with m1, you'll see that they are not that far off, in perf and in efficiency. And AMD is using 7nm, not 5nm! Also, nowdays, all the cpus are risc inside, so x86 cpus are very similar inside to arm cpus, with the addition of the extra decoding and micro ops.

x86 main weakness is also its greatest advantage. Backwards compatibility is very important and needs to stay. ARM cpus lose compatibility totally once in a while, which is not something that will work in the long run.

Also, don't forget that Intel hasn't introduced anything major since 2015! Ice Lake/Tigerlake are just a bump in execution units over skylake, which on its own brings 20% better IPC. But Intel has stayed still for so many years, that is why ARM has got the chance to close the gap.

SarahKerrigan - Tuesday, May 25, 2021 - link

What? SNC is not merely a bump in execution units from SKL at all. It's a new, wider, more aggressive uarch across the board. SNC is a larger change than SKL itself was, and not by a small margin.boredsysadmin - Tuesday, May 25, 2021 - link

@yeeeeman - "Also, nowdays, all the cpus are risc inside, so x86 cpus are very similar inside to arm cpus, with the addition of the extra decoding and micro ops."Excuse, where did you get this BS? Only Arm, Risk-V, MIPS, and PowerPC are using RISC. x86 from both Intel and AMD are very much still CISC. So, no they aren't very similar in any share and form.

Drumsticks - Tuesday, May 25, 2021 - link

All x86 CPUs crack CISC macro instructions into smaller RISC like operations. The actual execution of the CPU operates on these smaller micro ops. Beyond the initial decode/cracking stage, it's pretty much a RISC operation.They are CISC from an architectural perspective, but they've been RISC in execution for some time.

vvid - Tuesday, May 25, 2021 - link

>> All x86 CPUs crack CISC macro instructions into smaller RISC like operations.RISC-like is not RISC. It is like saying that a woman with pear-like figure shape is actually a pear.

x86 uops are pretty much corresponding to CISC ISA now.

>> but they've been RISC in execution for some time

RISC-like.

mode_13h - Wednesday, May 26, 2021 - link

> they've been RISC in execution for some time.And sadly, Internet Oversimplification Syndrome claims another victim.