The AMD Zen and Ryzen 7 Review: A Deep Dive on 1800X, 1700X and 1700

by Ian Cutress on March 2, 2017 9:00 AM ESTFetch

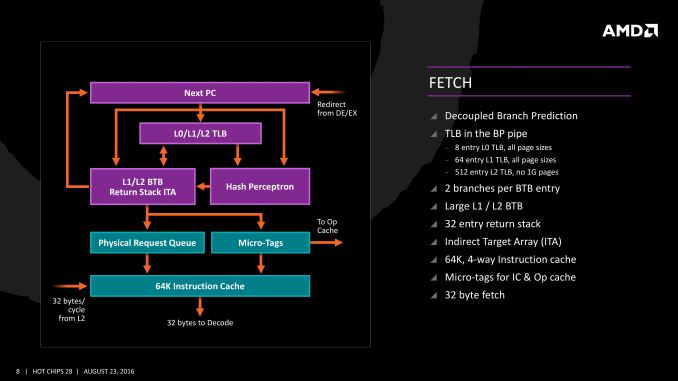

For Zen, AMD has implemented a decoupled branch predictor. This allows support to speculate on incoming instruction pointers to fill a queue, as well as look for direct and indirect targets. The branch target buffer (BTB) for Zen is described as ‘large’ but with no numbers as of yet, however there is an L1/L2 hierarchical arrangement for the BTB. For comparison, Bulldozer afforded a 512-entry, 4-way L1 BTB with a single cycle latency, and a 5120 entry, 5-way L2 BTB with additional latency; AMD doesn’t state that Zen is larger, just that it is large and supports dual branches. The 32 entry return stack for indirect targets is also devoid of entry numbers at this point as well.

The decoupled branch predictor also allows it to run ahead of instruction fetches and fill the queues based on the internal algorithms. Going too far into a specific branch that fails will obviously incur a power penalty, but successes will help with latency and memory parallelism.

The Translation Lookaside Buffer (TLB) in the branch prediction looks for recent virtual memory translations of physical addresses to reduce load latency, and operates in three levels: L0 with 8 entries of any page size, L1 with 64 entries of any page size, and L2 with 512 entries and support for 4K and 256K pages only. The L2 won’t support 1G pages as the L1 can already support 64 of them, and implementing 1G support at the L2 level is a more complex addition (there may also be power/die area benefits).

When the instruction comes through as a recently used one, it acquires a micro-tag and is set via the op-cache, otherwise it is placed into the instruction cache for decode. The L1-Instruction Cache can also accept 32 Bytes/cycle from the L2 cache as other instructions are placed through the load/store unit for another cycle around for execution.

Decode

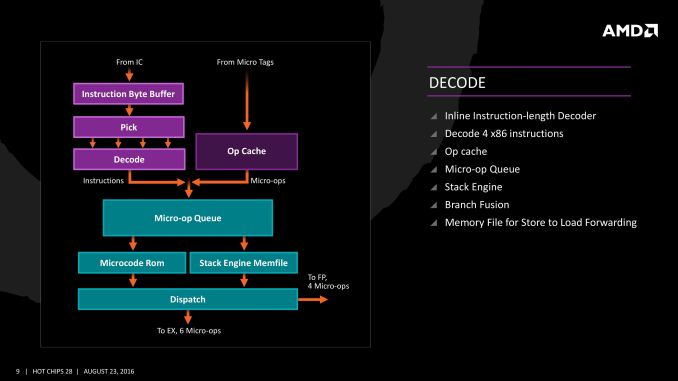

The instruction cache will then send the data through the decoder, which can decode four instructions per cycle. As mentioned previously, the decoder can fuse operations together in a fast-path, such that a single micro-op will go through to the micro-op queue but still represent two instructions, but these will be split when hitting the schedulers. The purpose of this allows the system to fit more into the micro-op queue and afford a higher throughput when possible.

The new Stack Engine comes into play between the queue and the dispatch, allowing for a low-power address generation when it is already known from previous cycles. This allows the system to save power from going through the AGU and cycling back around to the caches.

Finally, the dispatch can apply six instructions per cycle, at a maximum rate of 6/cycle to the INT scheduler or 4/cycle to the FP scheduler. We confirmed with AMD that the dispatch unit can simultaneously dispatch to both INT and FP inside the same cycle, which can maximize throughput (the alternative would be to alternate each cycle, which reduces efficiency). We are told that the operations used in Zen for the uOp cache are ‘pretty dense’, and equivalent to x86 operations in most cases.

574 Comments

View All Comments

rudolphna - Thursday, March 2, 2017 - link

Demonizing gamers in your post does nothing to contribute to your credibility, and will only turn off more well reasoned people from listening, or caring, about your opinion.samer1970 - Friday, March 3, 2017 - link

Gamers dont buy 8 cores chips .. If you want good AMD gaming chip at very low price , wait for the 6 and 4 cores Ryzen and then judge ...I expect the 4 cores/8 threads Ryzen at 150$ to blow Intel to pieces ... SOON ..

Imagine a 4.5Ghz AMD Ryzen 4 cores for $150 then talk .

Sttm - Friday, March 3, 2017 - link

4 cores that are noticeably slower than Intel's 4 cores, which sell in a handsome i5 package for $200. I think they need a software miracle and they need it fast to win over the gaming crowd.Cooe - Sunday, February 28, 2021 - link

Bet you're feeling like a massive idiot now if you actually got that 4c/4t Kaby Lake i5 over a 6c/12t Ryzen 5 1600. It was about as fast at 1080p gaming in 2017 as the R5, but nowadays isn't even in the same UNIVERSE as the Ryzen chip. Let alone the performance difference for literally EVERYTHING else.Diji1 - Thursday, March 2, 2017 - link

Hurr durr you don't like what I like so you're a dumbo making me smarter than you! (yes, I know but they cannot see it themselves because their so smart in their own imagination).JoeyJoJo123 - Thursday, March 2, 2017 - link

What exactly are you trying to say here?Holliday75 - Thursday, March 2, 2017 - link

I think it was "Hurr durr".BikeDude - Friday, March 3, 2017 - link

sounded more like 'hold door' to me?star-affinity - Thursday, March 2, 2017 - link

I didn't know what is considered "wasting your life" is objective – please elaborate. What do you do with your life that makes it better than someone who likes to plays RPGs?Dug - Friday, March 3, 2017 - link

I'm so glad you are the one to judge what people are when they play games. Your insight and thought process is inspiring.I'm only to guess that what you do with a computer is going to change the world.