AMD Zen Microarchitecture: Dual Schedulers, Micro-Op Cache and Memory Hierarchy Revealed

by Ian Cutress on August 18, 2016 9:00 AM ESTDeciphering the New Cache Hierarchy

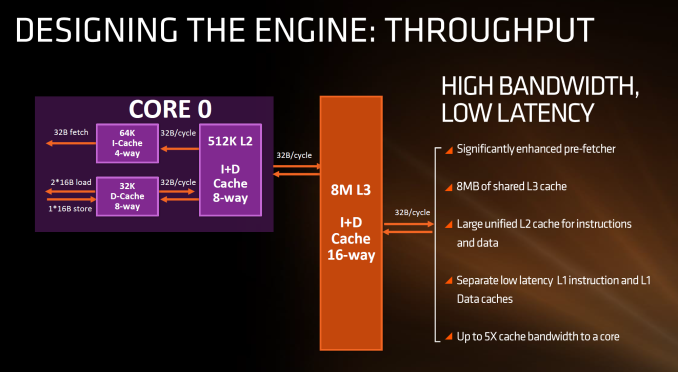

The cache hierarchy is a significant deviation from recent previous AMD designs, and most likely to its advantage. The L1 data cache is both double in size and increased in associativity compared to Bulldozer, as well as being write-back rather than write-through. It also uses an asymmetric load/store implementation, identifying that loads happen more often than stores in the critical paths of most work flows. The instruction cache is no longer shared between two cores as well as doubling in associativity, which should decrease the proportion of cache misses. AMD states that both the L1-D and L1-I are low latency, with details to come.

The L2 cache sits at half a megabyte per core with 8-way associativity, which is double that of Intel’s Skylake which has 256 KB/core and is only 4-way. On the other hand, Intel’s L3/LLC on their high-end Skylake SKUs is at 2 MB/core or 8 MB/CPU, whereas Zen will feature 1 MB/core and both are at 16-way associativity.

Edit 7:18am: Actually, the slide above is being slightly evasive in its description. It doesn't say how many cores the L3 cache is stretched over, or if there is a common LLC between all cores in the chip. However, we have recieved information from a source (which can't be confirmed via public AMD documents) that states that Zen will feature two sets of 8MB L3 cache between two groups of four cores each, giving 16 MB of L3 total. This would means 2 MB/core, but it also implies that there is no last-level unified cache in silicon across all cores, which Intel has. The reasons behind something like this is typically to do with modularity, and being able to scale a core design from low core counts to high core counts. But it would still leave a Zen core with the same L3 cache per core as Intel.

| Cache Levels | ||||

| Bulldozer FX-8150 |

Zen | Broadwell-E i7-6950X |

Skylake i7-6700K |

|

| L1 Instruction | 64 KB 2-way per module |

64 KB 4-way | 32 KB 8-way | 32 KB 8-way |

| L1 Data | 16 KB 4-way Write Through |

32 KB 8-way Write Back |

32 KB 8-way Write-Back |

32 KB 8-way Write-Back |

| L2 | 2 MB 16-way per module |

512 KB 8-way | 256 KB 8-way | 256 KB 4-way |

| L3 | 1 MB/core 64-way |

1 or 2 MB/core ? 16-way |

2.5 MB/core 16/20-way |

2 MB/core 16-way |

What this means, between the L2 and the L3, is that AMD is putting more lower level cache nearer the core than Intel, and as it is low level it becomes separate to each core which can potentially improve single thread performance. The downside of bigger and lower (but separate) caches is how each of the cores will perform snoop in each other’s large caches to ensure clean data is being passed around and that old data in L3 is not out-of-date. AMD’s big headline number overall is that Zen will offer up to 5x cache bandwidth to a core over previous designs.

216 Comments

View All Comments

Kevin G - Saturday, August 20, 2016 - link

HyperTransport was an AMD creation though they were not the first to use it. Former DEC engineers did help create it but they were employees by AMD at the time. AMD did license the EV6 bus for the the first Athlon (not Athlon 64). The first chip to that used the HT bus was Transmeta due to delays on the first generation Athlon 64/Operton.slyronit - Tuesday, August 23, 2016 - link

Ah! Good old days! I used to read all this in "Chip" magazine back in the day. Cyber cafes those days used "Cyrix" CPUs. Cheap.BMNify - Friday, August 19, 2016 - link

thats the thing, Did AMD actually learn something from their ARM inc partners and put in a real up to date interconnect or two that can lower overall latency and massively improve data throughput (ready with HBM2 perhaps) or did they cheap out again and rehash the usual antiquated suspectsnandnandnand - Thursday, August 18, 2016 - link

Good. I want Zen to perform well. Let's see Intel copy AMD and offer a 8c/16t chip at mainstream prices.akamateau - Thursday, August 18, 2016 - link

Hmmm...AMD was first with 1Ghz and faster processors.

AMD was first with multi-core processor.

AMD was first with CPU + GPU = APU. Intel has the laughably poor performing Intel IGP LOL. And to get it Intle had to poach technology from NVidia and then NVidia sued them!!!! LOL

AMD owns X86-64.

SO your point?????

AMD has a license to copy Intel and if like Frank Sinatra chooses to do it their way, it can only be good for the consumer.

So smarten up. Without AMD Intel would have killed the PC 10 years ago with $2000 CPU's!!!

smilingcrow - Thursday, August 18, 2016 - link

I don't live in the past from a decade ago. When AMD finally release their first decent CPU in 10 years wake me up.Even with negligible competition from AMD Intel has chosen to keep the prices of chips for the mainstream socket at low levels for 10 years. It was 2009 with Lynnfield that they last had a $1,000 Extreme chip for consumers and there were plenty of good chips in that range starting at under $300 so the Extreme chips were for rich fools really.

The_Countess - Saturday, August 20, 2016 - link

intel created a entire artificial market segment with the i5's because of lack of competition. they still sell dual cores for christ sake, and havent offered anything above 4 cores on the main stream market, which AMD's had for over 6 years already.On 22nm, let alone 14, there is no way they couldn't have made a affordable 6 core. but all we get are ridiculously priced -E variants on a ridiculously overpriced platform.

FMinus - Thursday, August 18, 2016 - link

that is still at most ~20 years back, AMD is on the face of the earth for 47 years and more as half of that they spend innovating nothing, but being contractors and priates of technology.tamalero - Friday, August 19, 2016 - link

whats with hardcore intel fanboys just getting out of their caves now that AMD might have a decent cpu to compete with Intel?The_Countess - Saturday, August 20, 2016 - link

and they went from that to creating the athlon64 and royally kicking intel's ass with superior innovations in just 14 years (counting from the first k5).to bad intel's monopoly abuse has already done its damage leaving AMD wofully short on production capacity meaning 80% of people still had to buy intel's crummy shit for too much money. and with AMD not making nearly as much money as it should have from the athlon64, intel could one again copy everything AMD did and then brute force outspend them.