AMD Zen Microarchitecture: Dual Schedulers, Micro-Op Cache and Memory Hierarchy Revealed

by Ian Cutress on August 18, 2016 9:00 AM ESTLow Power, FinFET and Clock Gating

When AMD launched Carrizo and Bristol Ridge for notebooks, one of the big stories was how AMD had implemented a number of techniques to improve power consumption and subsequently increase efficiency. A number of those lessons have come through with Zen, as well as a few new aspects in play due to the lithography.

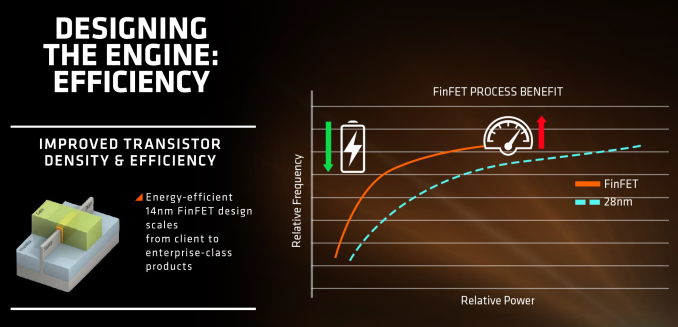

First up is the FinFET effect. Regular readers of AnandTech and those that follow the industry will already be bored to death with FinFET, but the design allows for a lower power version of a transistor at a given frequency. Now of course everyone using FinFET can have a different implementation which gives specific power/performance characteristics, but Zen on the 14nm FinFET process at Global Foundries is already a known quantity with AMD’s Polaris GPUs which are built similarly. The combination of FinFET with the fact that AMD confirmed that they will be using the density-optimised version of 14nm FinFET (which will allow for smaller die sizes and more reasonable efficiency points) also contributes to a shift of either higher performance at the same power or the same performance at lower power.

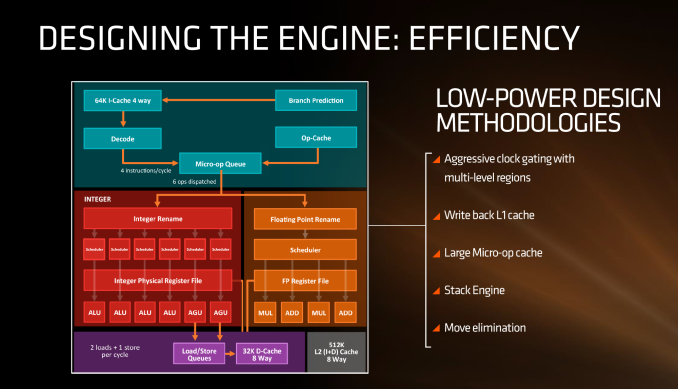

AMD stated in the brief that power consumption and efficiency was constantly drilled into the engineers, and as explained in previous briefings, there ends up being a tradeoff between performance and efficiency about what can be done for a number of elements of the core (e.g. 1% performance might cost 2% efficiency). For Zen, the micro-op cache will save power by not having to go further out to get instruction data, improved prefetch and a couple of other features such as move elimination will also reduce the work, but AMD also states that cores will be aggressively clock gated to improve efficiency.

We saw with AMD’s 7th Gen APUs that power gating was also a target with that design, especially when remaining at the best efficiency point (given specific performance) is usually the best policy. The way the diagram above is laid out would seem to suggest that different parts of the core could independently be clock gated depending on use (e.g. decode vs FP ports), although we were not able to confirm if this is the case. It also relies on having very quick (1-2 cycle) clock gating implementations, and note that clock gating is different to power-gating, which is harder to implement.

216 Comments

View All Comments

SunnyNW - Thursday, August 18, 2016 - link

Looks like the early leak (AOTS) is more/less correct at least for the ES...at the presentation they had the 8c/16t part running at 3ghz.StormyParis - Thursday, August 18, 2016 - link

"Firstly,"I object bigly to that word.

psurge - Thursday, August 18, 2016 - link

Ian - I think there's a mistake on the first page. As far as I know, AGUs do not perform loads and stores, they calculate load/store addresses. It strikes me as interesting that Zen can perform memory operations more quickly (3 per cycle) than it can generate addresses for them (2 per cycle, per the diagram).KaarlisK - Thursday, August 18, 2016 - link

"some put it as a major stepping stone for Conroe"Err, wasn't it Sandy Bridge?

MrSpadge - Thursday, August 18, 2016 - link

Good catch, I think you're right.silverblue - Thursday, August 18, 2016 - link

I thought Conroe's ace was its four-issue front end; AMD didn't have that ability until Bulldozer.farmergann - Thursday, August 18, 2016 - link

Did anyone else notice AMD's Zen has 2x GCN CUs? LOL, this is how they managed to trump broadwell-e in Blender. Slightly dishonest since they didn't mention that, but I'm proud of them for showing some competitive fire!Ian Cutress - Saturday, August 20, 2016 - link

Source?patel21 - Thursday, August 18, 2016 - link

For me, a performance comparable to i3 skylake, with power requirements at max over 20% of i3, with a good gpu integrated and at around 70% of i3's price. And My boat will sail AMD....Ho yaaiwod - Thursday, August 18, 2016 - link

Assuming no major bugs, or I/O ( AMD has ALWAYS HAD problem with I/O controller ), Zen should do very well in Server market.Yes there is Pref/ Watt, but when you compound it in the Server power usage from other component, I think Zen should be favourable to many. ( Assuming Intel dont massively drop price )