Investigating Cavium's ThunderX: The First ARM Server SoC With Ambition

by Johan De Gelas on June 15, 2016 8:00 AM EST- Posted in

- SoCs

- IT Computing

- Enterprise

- Enterprise CPUs

- Microserver

- Cavium

The Small Cavium ARM Core

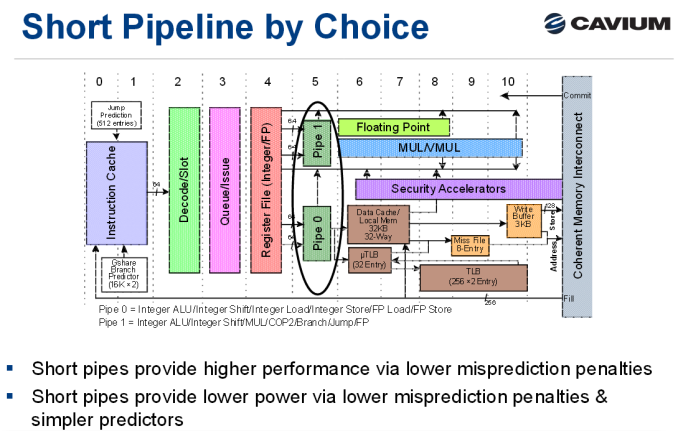

Cavium has not talked much about ThunderX's internals. But since the launch of the Octeon back in 2006, Cavium has continued to build further upon this microarchitecture. Given the similarities in specifications and what we have read and heard so far about the ThunderX, it is safe to assume that the internal architecture of ThunderX is an improved version of the Octeon III.

The Cavium core can probably only sustain 2 instructions per clock, with a very simple 4 issue back-end. To put this in perspective: Intel's latest "Broadwell/Skylake" designs can sustain 5-6 instructions per clock and issue up to 8 integer instructions (load/store included). While we are not sure whether there have not been significant changes to the backend, the basic pipeline has remained the same (9 cycles instead of 8). That means that the design might do well in branch intensive low IPC situations, which are very common in lots of server applications. But the consequence is also that it is very unlikely that the Cavium will be able to reach the turbo speeds that the Xeons reach (3.5 GHz and more).

To that end we'll test this in great detail: is the Cavium ThunderX core more like an ARM Cortex-A53, or is it a bit more muscular?

82 Comments

View All Comments

BlueBlazer - Friday, June 17, 2016 - link

Cavium is quite aware of their ThunderX single thread weakness, and directly from Cavium themselves https://www.youtube.com/watch?v=ei9uVskwPNE thanks to ARMdevices.net.TiffanyTown - Thursday, July 28, 2016 - link

hi, The JDK version you used is OpenJDK 1.8.0_91 . Did you build it yourself?