The Intel Xeon E7-8800 v3 Review: The POWER8 Killer?

by Johan De Gelas on May 8, 2015 8:00 AM EST- Posted in

- CPUs

- IT Computing

- Intel

- Xeon

- Haswell

- Enterprise

- server

- Enterprise CPUs

- POWER

- POWER8

Haswell Architecture Improvements

We have discussed the advantages that the Haswell core brings here in more detail. In a nutshell:

- The core can sustain about 10% more integer instructions per clock cycle than its predecessor, Ivy Bridge.

- Virtualized applications should perform slightly better thanks to the lower VM exit/entry latency.

- HPC applications could/should benefit much more if they are recompiled to make use of the improved AVX2 and Fused Multiply Add (FMA) support

- Database transactional applications should benefit more thanks to the lower synchronization latency.

- In-memory databases should benefit if they are adapted to make use of the AVX-2 256 bit integer vector operations.

Again, the same is true about the Xeon E5-2600v3. So what makes the E7 special?

Transactional Synchronization Extensions: I'll be back

There is one "new" - or rather "now working" - feature: TSX or the famous Transactional Synchronization eXtensions. These extensions are all about making locking more "optimistic" (you let the CPU handle the bookkeeping to maintain consistency). TSX is quite powerful, but also can be a liability in the wrong use case. Developers will need a deep understanding of the locking and parallel programming to be able to make good use of TSX, as

- ... you still have to rewrite your code (inserting hints)

- TSX may reduce performance in some situations: if indeed a pessimistic lock was necessary, the transaction has to be re-executed with a "traditional" conservative way of locking. You could call it a "lock misprediction".

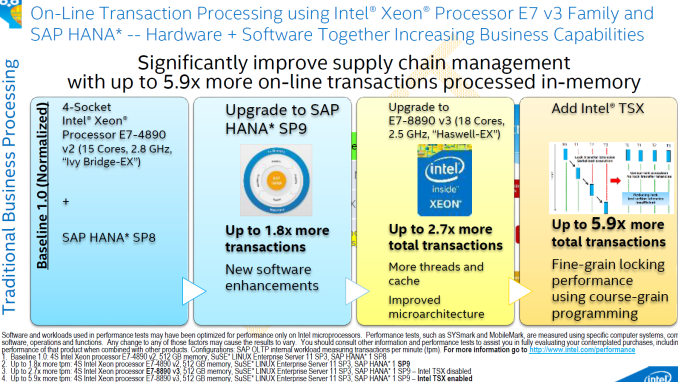

Introducing TSX in software requires assessing the different locks in application, using different libraries and quite a bit of of tuning. SAP and Intel did this for the expensive in-memory data mining SAP HANA software.

The upgrade from "Ivy Bridge EX" to "Haswell-EX" yielded 50% performance, while introducing TSX roughly doubled performance. So in TSX enabled data mining software, Haswell-EX has the potential to reduce the waiting time by a factor of 3 and more.

146 Comments

View All Comments

TheSocket - Friday, May 8, 2015 - link

They sure wouldn't lose the x86-64 license since they own it and Intel is licensing it from AMD.melgross - Saturday, May 9, 2015 - link

But without the license from Intel, it is worthless. There's also the question of how that works. I believe that Intel doesn't need to license back the 64 bit extensions.Kevin G - Monday, May 11, 2015 - link

This one of the reasons why it would be in Intelsat best interest to let AMD be bought out with the 32 bit license intact. The 64 bit license/patents going to a third party that doesn't want to share would be a dooms day scenario for Intel. Legally it wouldn't affect anything currently on the market but it'd throw Intel's future roadmap into the trash.Death666Angel - Saturday, May 9, 2015 - link

Pretty sure some regulatory bodies would step in if Intel were the only x86 game in town. And x86-64 is AMD property.JumpingJack - Saturday, May 9, 2015 - link

Any patents on x86 are long expired, AMD only owns the IP related to the extension of the x86 not the instruction set.patrickjp93 - Monday, May 11, 2015 - link

Not true. The U.S. government has them locked up under special military-based protections. Absolutely no one can make and sell x86 without Intel's and the DOD's permission.Kevin G - Monday, May 11, 2015 - link

Got a source for that?I know that DoD did some validation on x86 many years ago. (The Pentium core used by Larrabee had the DoD changes incorporated.)

haplo602 - Friday, May 8, 2015 - link

hmm ... where's the RAS feature comparison/test ? did I miss it in the article ?TeXWiller - Friday, May 8, 2015 - link

In the E7v3 vs POWER comparison table, there should be 32 PCIe lanes instead 40 in the Xeon column.TeXWiller - Friday, May 8, 2015 - link

Additionally, it is the L3 in POWER8 that runs half of the core speed. L2 runs at the core speed.