Intel's Xeon E5-2600 V2: 12-core Ivy Bridge EP for Servers

by Johan De Gelas on September 17, 2013 12:00 AM ESTLS-DYNA Power Consumption

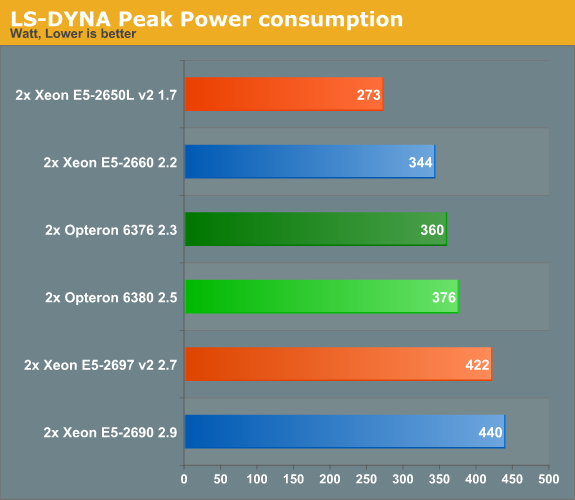

For HPC buyers, peak power tends to be a very important metric. As HPC systems are run at close to 100% CPU load, the energy consumption is at its peak for a long time. Peak power thus also determines the cooling and energy requirements. This is in sharp contrast with most other servers, where calculating the power and amps based on the peak load of a complete rack is considered wasteful as it is highly unlikely that all servers will hit 100% CPU load at the same time.

We took the 95th percentile of our power numbers. Note that the Xeon E5 numbers are not directly comparable to the Opteron numbers as the CPUs are tested in servers with different form factors.

The power savings of the new Xeon E5 2697 are not as spectacular as we witnessed in our virtualization benchmark, but they are still measureable. Our best guess is that the Ivy Bridge architecture efficiency has mostly improved for integer dominated workloads, less for floating point.

70 Comments

View All Comments

psyq321 - Tuesday, September 17, 2013 - link

Yep, EP-46xx v2 will use the same C1 stepping (for HCC SKUs) for production parts as 2P Xeons, but there will be some features enabled in microcode which did not make it in the 26xx SKUs.EX is already on D1 stepping for QS, as the validation cycle for EX is more strict due to more RAS features etc.

Casper42 - Tuesday, September 17, 2013 - link

So I work for HP and your comments about 4x1P instead of 2x2P make me wonder if you have been sneaking around our ProLiant development lab in Houston.I was there 6 weeks ago and a decent sized cluster of 1P nodes was being assembled on an as yet unannounced HP platform. I was told the early/beta customer it was for had done some testing and found for their particular HPC app, they were in fact getting measurably better overall performance.

The interesting thing about this design was they put 2 x 1P nodes on a single PCB (Motherboard) in order to more easily adapt the 1P nodes to a system largely designed with 2P space requirements in mind.

Pretty sure the chips were Haswell based as well but can't recall for sure.

André - Tuesday, September 17, 2013 - link

Would be nice to see benchmarks for OS X, considering this thing is going inside the new Mac Pro.Final Cut X, After Effects, Premiere Pro, Photoshop, Lightroom, DaVinci Resolve etc.

I believe the 2660v2 hits the sweet spot with it's 10 cores.

DanNeely - Tuesday, September 17, 2013 - link

That'd require Apple giving Anandtech a new Mac Pro to run benchmarks on...Kevin G - Tuesday, September 17, 2013 - link

Now that Intel has officially launched the new Xeons, the new Mac Pro can't be far behind.wallysb01 - Tuesday, September 17, 2013 - link

Well, you could run the CPU benchmarks just fine. But not the GPU ones.Simon G - Tuesday, September 17, 2013 - link

Typo in Conclusion section . . . " Thta's no small feat, . . ."garadante - Tuesday, September 17, 2013 - link

There's a minor error on the Cinebench single-threaded graph. It has the clock speed for the E5-2697 v2 as 2.9 instead of 2.7, as it should be. Which is semi confusing on that graph as it explains the lower single-threaded performance from the E5-2690.SanX - Tuesday, September 17, 2013 - link

This forum has most obsolete comments design of pre-Neanderthals times, no Edit, no Delete, no look at previous user comments. Effin shameMrSpadge - Tuesday, September 17, 2013 - link

You mixed up forum and article comments.