Intel’s Silvermont Architecture Revealed: Getting Serious About Mobile

by Anand Lal Shimpi on May 6, 2013 1:00 PM EST- Posted in

- CPUs

- Intel

- Silvermont

- SoCs

ISA

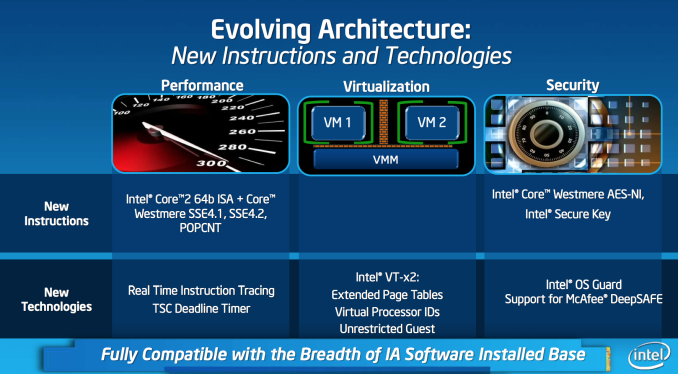

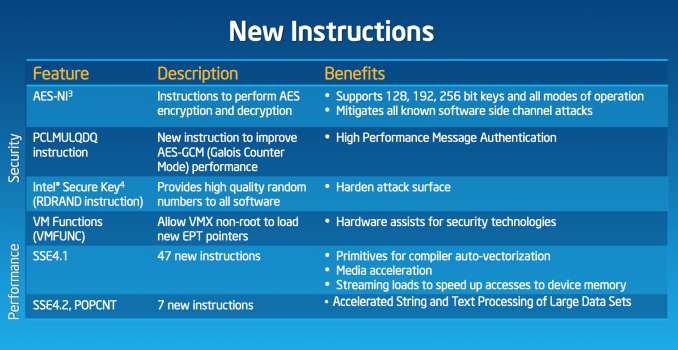

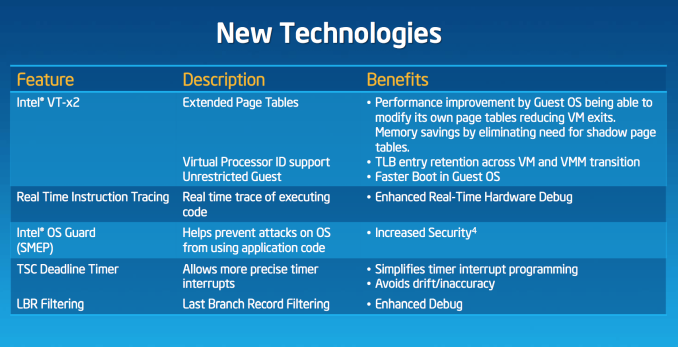

The original Atom processor enabled support for Merom/Conroe-class x86 instructions, it lacked SSE4 support due to die/power constraints; that was at 45nm, at 22nm there’s room for improvement. Silvermont brings ISA compatibility up to Westmere levels (Intel’s 2010 Core microprocessor architecture). There’s now support for SSE4.1, SSE4.2, POPCNT and AES-NI.

Silvermont is 64-bit capable, although it is up to Intel to enable 64-bit support on various SKUs similar to what we’ve seen with Atom thus far.

IPC and Frequency

The combination of everything Intel is doing on the IPC front give it, according to Intel, roughly the same single threaded performance as ARM’s Cortex A15. We’ve already established that the Cortex A15 is quite good, but here’s where Silvermont has a chance to pull ahead. We already established that Intel’s 22nm process can give it anywhere from a 18 - 37% performance uplift at the same power consumption. IPC scaling gives Silvermont stable footing, but the ability to run at considerably higher frequencies without drawing more power is what puts it over the top.

Intel isn’t talking about frequencies at this point, but I’ve heard numbers around 2 - 2.4GHz thrown around a lot. Compared to the 1.6 - 2GHz range we currently have with Bonnell based silicon, you can see how the performance story gets serious quickly. Intel is talking about a 50% improvement in IPC at the core, combine that with a 30% improvement in frequency without any power impact and you’re now at 83% better performance potentially with no power penalty. There are other advantages at the SoC level that once factored in drive things even further.

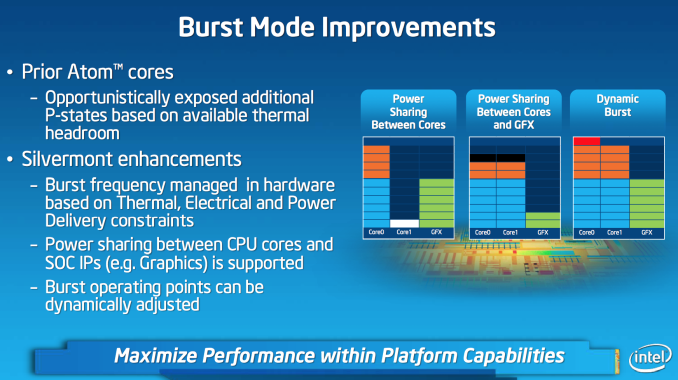

Real Turbo Modes & Power Management

Previous Atom based mobile SoCs had a very crude version of Intel’s Turbo Boost. The CPU would expose all of its available P-states to the OS and as it became thermally limited, Intel would clamp the max P-state it would expose to the OS. Everything was OS-driven and previous designs weren’t able to capitalize on unused thermal budget elsewhere in the SoC to drive up frequency in active parts of chip. This lack of flexibility even impacted the SoC at the CPU core level. When running a single threaded app, Medfield/Clover Trail/et al couldn’t take thermal budget freed up by the idle core and use it to drive the frequency of the active core. Previous Atom implementations were basically somewhere in the pre-Nehalem era of thermal/boost management. From what I’ve seen, this is also how a lot of the present day ARM architectures work as well. At best, they vary what operating states they expose to the OS and clamp max frequency depending on thermals. To the best of my knowledge, none of the SoC vendors today actively implement modern big-core-Intel-like frequency management. Silvermont fixes this.

Silvermont, like Nehalem and the architectures that followed, gets its own power control unit that monitors thermals and handles dynamic allocation of power budget to various blocks within the SoC. If I understand this correctly, Silvermont should expose a maximum base frequency to the OS but depending on instruction mix and available TDP it can turbo up beyond that maximum frequency as long as it doesn’t exceed TDP. Like Sandy Bridge, Silvermont will even be able to exceed TDP for a short period of time if the package temperature is low enough to allow it. Finally, Silvermont’s turbo can also work across IP blocks: power budget allocated to the GPU can be transferred to the CPU cores (and vice versa).

By big-core standards (especially compared to Haswell), Silvermont’s turbo isn’t all that impressive but compared to how things are currently handled in the mobile space this should be a huge step forward.

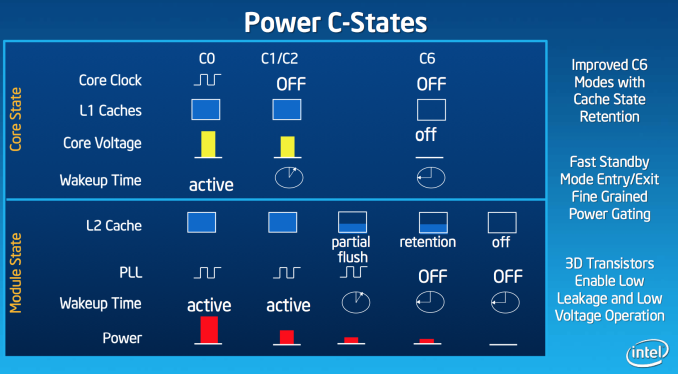

On the power management side, getting in and out of C6 should be a bit quicker. There's also a new C6 mode with cache state retention.

174 Comments

View All Comments

silverblue - Monday, May 6, 2013 - link

I do wonder how much having a dual channel memory interface helps Silvermont, though. It's something that neither Atom nor Bobcat has enjoyed previously, and I've not heard much about Jaguar on this subject (ignoring the PS4, that is). AMD certainly has the lead on ISAs though, so regardless of how good Silvermont is, it's going to trail in some places.I'm a little confused as to the virtual lack of a comparison to AMD in this piece; yes, Intel did say they wanted to beat ARM at its own game, but with Jaguar-powered devices already in the wild and AMD sporting a new custom-CPU team for whoever wants whatever, this is going to be interesting.

Benchmarks, please! ;)

powerarmour - Monday, May 6, 2013 - link

Atom had dual channel memory with the ION chipset btw.silverblue - Monday, May 6, 2013 - link

Really? Oh well, in that case then, maybe not too much.Spunjji - Wednesday, May 8, 2013 - link

Only until Intel murdered that, of course :|ajp_anton - Monday, May 6, 2013 - link

Where did you find "8x" in the slides?Gigaplex - Tuesday, May 7, 2013 - link

AMDs HSA is most definitely something to be enthusiastic about.theos83 - Monday, May 6, 2013 - link

You're right, I've seen this tendency in AT's reviews and discussions as well. I understand that a lot of it comes from reviewing PC components and processors where Intel dominated the market. Also, most of the slides here are marketing material. For example, the 22nm Ivy Bridge tri-gate plots have been out since 2011. True, Intel is the first and only foundry to bring FinFETs to the market successfully and I applaud them for that. However, the performance vs power advantage is not that evident, since even though Tri-gates allow 100mV reduction in threshold voltage and hence, supply voltage, various blogs have reported that most Ivy bridge processors did not scale down supply voltage below 0.9V. FinFETs are great for high performance parts, however, you need to really pay attention to reliability and variation to make it successful for SoCs, they are a completely different ball-game.Also, the rest of the SoC makers already have roadmaps ready for the future, they are a fast moving target. Hence lets see benchmarked numbers from Intel processors before jumping on the marketing bandwagon.

Pheesh - Monday, May 6, 2013 - link

"However, the performance vs power advantage is not that evident, since even though Tri-gates allow 100mV reduction in threshold voltage and hence, supply voltage, various blogs have reported that most Ivy bridge processors did not scale down supply voltage below 0.9V." Didn't the start of the article cover that they are using a different manufacturing process for these lower power SOC's as compared to ivy bridge processors?saurabhr8here - Monday, May 6, 2013 - link

The SoC process has some differences in the metal stack for higher density and has additional transistor flavors (longer channel lengths). Check Intel's IEDM 2012 paper for more information, however, the truth is that their tri-gate process improvements claimed in the 'plots' shown and actual performance improvements in processors have a significant gap. I think that Intel tri-gates are great, but they aren't as 'wonderful' as presented in the marketing slides.Krysto - Monday, May 6, 2013 - link

Thank You! People are starting to get it.