Intel's Haswell Architecture Analyzed: Building a New PC and a New Intel

by Anand Lal Shimpi on October 5, 2012 2:45 AM ESTThe Haswell Front End

Conroe was a very wide machine. It brought us the first 4-wide front end of any x86 micro-architecture, meaning it could fetch and decode up to 4 instructions in parallel. We've seen improvements to the front end since Conroe, but the overall machine width hasn't changed - even with Haswell.

Haswell leaves the overall pipeline untouched. It's still the same 14 - 19 stage pipeline that we saw with Sandy Bridge depending on whether or not the instruction is found in the uop cache (which happens around 80% of the time). L1/L2 cache latencies are unchanged as well. Since Nehalem, Intel's Core micro-architectures have supported execution of two instruction threads per core to improve execution hardware utilization. Haswell also supports 2-way SMT/Hyper Threading.

The front end remains 4-wide, although Haswell features a better branch predictor and hardware prefetcher so we'll see better efficiency. Since the pipeline depth hasn't increased but overall branch prediction accuracy is up we'll see a positive impact on overall IPC (instructions executed per clock). Haswell is also more aggressive on the speculative memory access side.

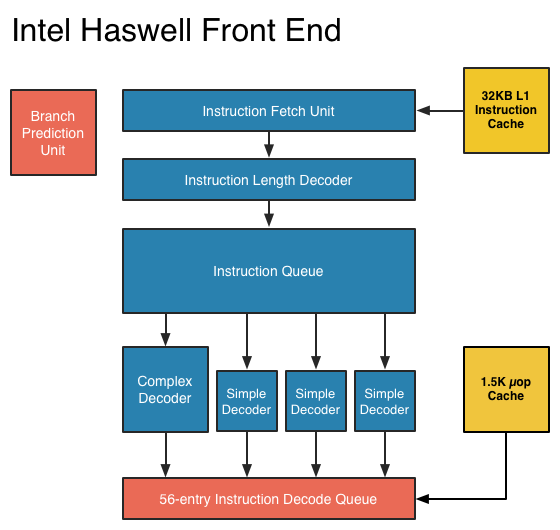

The image below is a crude representation I put together of the Haswell front end compared to the two previous tocks. If you click the buttons below you'll toggle between Haswell, Sandy Bridge and Nehalem diagrams, with major changes highlighted.

In short, there aren't many major, high-level changes to see here. Instructions are fetched at the top, sent through a bunch of steps before getting to the decoders where they're converted from macro-ops (x86 instructions) to an internally understood format known to Intel as micro-ops (or µops). The instruction fetcher can grab 4 - 5 x86 instructions at a time, and the decoders can output up to 4 micro-ops per clock.

Sandy Bridge introduced the 1.5K µop cache that caches decoded micro-ops. When future instruction fetch requests are made, if the instructions are contained within the µop cache everything north of the cache is powered down and the instructions are serviced from the µop cache. The decode stages are very power hungry so being able to skip them is a boon to power efficiency. There are also performance benefits as well. A hit in the µop cache reduces the effective integer pipeline to 14 stages, the same length as it was in Conroe in 2006. Haswell retains all of these benefits. Even the µop cache size remains unchanged at 1.5K micro-ops (approximately 6KB in size).

Although it's noted above as a new/changed block, the updated instruction decode queue (aka allocation queue) was actually one of the changes made to improve single threaded performance in Ivy Bridge.

The instruction decode queue (where instructions go after they've been decoded) is no longer statically partitioned between the two threads that each core can service.

The big changes in Haswell are at the back end of the pipeline, in the execution engine.

245 Comments

View All Comments

Magik_Breezy - Sunday, October 14, 2012 - link

Probably real customer support without paying an extra $200Spunjji - Thursday, October 18, 2012 - link

Yawn.Spunjji - Thursday, October 18, 2012 - link

The bit that aggravates me the most is that even with this lavishing of review pages, the actual comparison of Apple products to competitors tends to lack (particularly with the Macbook article). This is understandable under some circumstances (iPhone battery life - new test, small selection of data points) but not for others.Arbee - Friday, October 5, 2012 - link

I'm not really seeing any of that. AT's Android and Windows Phone reviews are just as in-depth and complementary where due as their Apple ones. AFAIK both Anand's and Brian's daily-driver phones aren't iPhones, even. They care about the tech, not who it comes from. It just happens that Apple is often the original source of new and interesting things in that space. At this exact moment they're the only people shipping something new and interesting. When the Nokia 920 launches, I'm confident Anand and Brian will be ready with a 15+ page review and discussion of anything novel on the podcast, and when Winter CES brings us Tegra 4 and other Android news, I expect to see eye-glazing levels of detail here at AT.(As an aside, I smiled at how closely DPReview's discussion of the alleged "purple haze" problem tracked Brian's rant on the podcast - clearly both writers know what they're talking about, which can be a rare quantity in tech journalism).

VivekGowri - Saturday, October 6, 2012 - link

I think Anand's daily driver is an iPhone, but he frequently carries the latest Android/WP device on the side. Brian and myself end up daily driving like a half dozen phones a month, depending on what shows up at our doorstep.Zink - Saturday, October 6, 2012 - link

"iPad 3 form factor" was used because all of the other tablets have 25Wh batteries and draw about 5W max. The A5X iPad and it's giant 42.5Wh battery on the other hand can put out over 10W of heat which is the power envelope where Intel might target a Haswell SOC.amdwilliam1985 - Monday, October 8, 2012 - link

I totally agree with you on the Apple part. That's the biggest pullback on reading Anand writings. Too much Apple praising.I used to be an Apple fan, but recently they're becoming the biggest jerks in the technology industry. The human/ethical part of in me hates them so much, that I won't buy anything that has a Apple logo on it.

I gave away my iPad 2, switched to Samsung Galaxy S phones, and using my HP windows 7 laptop over the 2011 MBA.

-say NO to bully, say NO to Apple.

xaml - Thursday, May 23, 2013 - link

Number of problems solved with this approach: NO.dartox - Tuesday, November 27, 2012 - link

Probably because most people know about how large an iPad is - if he said "tablet" form factor that's ambigious.. and if he said "Motorola XOOM" form factor not as many people are familiar with the size.Paer0 - Friday, October 5, 2012 - link

Yes... Macs are well engineered and deliver a solid performance across board.