Intel's Ivy Bridge Architecture Exposed

by Anand Lal Shimpi on September 17, 2011 2:00 AM EST- Posted in

- CPUs

- Intel

- Ivy Bridge

- IDF 2011

- Trade Shows

Power Efficiency Improvements

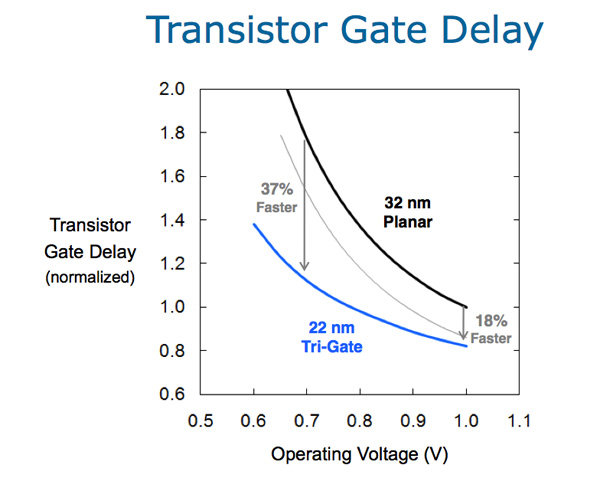

When Intel introduced its 22nm tri-gate transistors Intel claimed that it could see an 18% increase in performance at 1V compared to its 32nm process. At the same switching speed however, Intel's 22nm transistors can run at 75 - 80% of the voltage of their 32nm counterparts. Ivy Bridge's process alone should account for some pretty significant power savings. In addition to process however, there are a few architectural changes in IVB that will reduce power consumption.

Lower System Agent Voltages

Sandy Bridge introduced the System Agent, a name that used to refer to the uncore of a processor but now refers to the display output, memory controller, DMI and PCI Express interfaces. As of Sandy Bridge, the L3 cache was no longer included in the uncore and thus it wasn't a part of the System Agent.

The System Agent operates on a separate voltage plane than the rest of the chip. On Ivy Bridge Intel now offers even lower System Agent voltage options for the lower voltage SKUs, which in turn helps power optimize those SKUs.

More Accurate Voltage Characterization

Today Intel defines three different voltages for every Sandy Bridge CPU: LFM, nominal and turbo. LFM is the lowest frequency the CPU can run at (e.g. completely idle), nominal is the frequency it is specified to run at (e.g. 3.3GHz for a 2500K) and turbo is the highest available turbo frequency (e.g. 3.7GHz for a 2500K). Intel determines the lowest voltage possible for each one of those frequencies. Sandy Bridge obviously runs at more than just three frequencies, there are many more intermediate frequencies that it may run at depending on the current workload. The voltages at those intermediate frequencies are interpolated from the three points that I mentioned above.

With Ivy Bridge, Intel characterizes even more points along the frequency curve. Intel didn't reveal exactly how many points but it's more than three. A curve is then fit to the frequency/voltage data and depending on IVB's operating frequency a more accurate voltage point is calculated. The result from all of this seemingly simple work is a reduction in core voltage at these intermediate frequencies. Voltage changes have a cubic affect on power, so even a small reduction here can have a tangible impact. One of the points that wasn't previously characterized was max thread turbo. Ivy Bridge should be more power efficient in cases where you have all cores active.

Power Aware Interrupt Routing

This next feature is pretty neat. Ivy Bridge has logic to properly route interrupt requests to cores that are already awake vs. those that are asleep in their lowest power states. Obviously this approach can save a lot of power, however it may rob those active cores of some performance. IVB will allow prioritizing performance as well. Interrupt handling can thus be handled similarly to how it is today, or optimally for power savings.

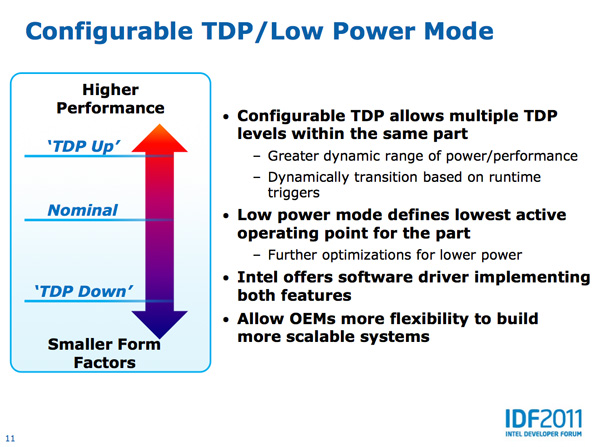

Configurable TDP

I already wrote about what this is but if you missed our Pipeline post on it I'll briefly recap. All CPUs ship with a rated thermal design point (TDP) that tells OEMs what sort of cooling the chip requires. Traditionally that TDP value remained static and the CPU could do whatever it wanted but exceed that value. Ivy Bridge introduces configurable TDP that allows the platform to increase the CPU's TDP if given additional cooling, or decrease the TDP to fit into a smaller form factor.

The cTDP up mode is obviously for docked notebooks. You can imagine an Ivy Bridge notebook with an optional dock that could enhance the cooling capabilities of the machine. When undocked the notebook's processor would operate at a max TDP of 17W, for example, but toss it in a dock with additional cooling and the TDP would jump up to 33W. It's up to the OEMs to decide how they want to take advantage of this feature. It could be something as simple as a mobile dock with more fans, or something as complex as a modular water cooling solution with a bigger radiator in the dock. I haven't seen any concepts of systems that take advantage of Ivy Bridge's cTDP up support, but that's the theory.

What about cTDP down? Take the same 17W Ivy Bridge CPU from above but now drop the TDP to 13W, which in turn limits clock speed and voltage. Why would you want to do this? From the OEM perspective, Intel's TDP choices may seem arbitrary. Downwards configurable TDP allows OEMs to get a lower power configuration without forcing Intel to create a new SKU. OEMs can do this today through undervolting/underclocking of their own, but the cTDP down spec will at least give OEMs a guarantee of performance/power.

Configurable TDP obviously only applies to mobile Ivy Bridge. In particular the ultra low voltage and extreme edition parts will support cTDP. The cTDP values are listed in the table below:

| Ivy Bridge Configurable TDP | |||||

| cTDP Down | Nominal | cTDP Up | |||

| Ivy Bridge ULV | 13W | 17W | 33W | ||

| Ivy Bridge XE | 45W | 55W | 65W | ||

The most interesting are the 17W ULV Ivy Bridge parts as far as I'm concerned. Today you do sacrifice clock speed to get into the form factor of a MacBook Air. A clever OEM armed with Ivy Bridge might be able to deliver a cooling dock that would give you the best of both worlds: an ultra portable chassis on the go, and higher clock speeds while docked.

97 Comments

View All Comments

Hrel - Thursday, September 22, 2011 - link

1: I said comparable, not competitive.2: I don't care about price. I make enough it doesn't matter. I just care about performance. At the same time, I don't waste money, so I don't buy Extreme Editions either. I buy whatever CPU has the best performance around 200 bucks.

Point: At this point if AMD is even close (within 15%) I'm switching.

mino - Monday, September 26, 2011 - link

If price does not matter, the you shall not bother about desktop stuff and go directly fro 2P workstations with ECC.Just a thought.

JKflipflop98 - Monday, October 24, 2011 - link

Hind sight is 20/20 now.Zoomer - Saturday, September 17, 2011 - link

That stuff can, and imo should, be implemented in the filesystem.Cr0nJ0b - Saturday, September 17, 2011 - link

I'm wondering they wounldn't just got with all USB 3.0 ports since they are backward compatible with other UBS forms. Maybe a licensing cost issue?Zoomer - Saturday, September 17, 2011 - link

Intel's platform is really a mess and a hodgepodge nowadays. Pity.ggathagan - Saturday, September 17, 2011 - link

There aren't enough PCIe lanes to allow for that kind of bandwidth.DanNeely - Sunday, September 18, 2011 - link

Along with the fact that USB3 controllers are larger and need more pins on the chip to connect. They're the same reasons that AMD only has a 4 USB3 ports on its most recent southbridges.marcusj0015 - Saturday, September 17, 2011 - link

Intel Invented USB...so no there are no licensing costs that i can think of.

Aone - Sunday, September 18, 2011 - link

Is Ivy's Quick Sync in the same power gated domain together with IGP as it happens in SB or Quick Sync and IGP can be switched on/off independently?