Intel Enterprise and Corporate Roadmap - Q3'05 Update

by Jarred Walton on September 12, 2005 12:00 AM EST- Posted in

- CPUs

Enterprise Server Roadmap

The last sector is one that few people will actually encounter, but we always find the Itanium roadmaps to be interesting. Intel has repeatedly stated that the desktop sector isn't really ready for 64-bit processors and OSes, and we have to say that they're right. XP-64 is available, but we can't actually recommend anyone switch to it just yet. Driver support is lacking, and performance isn't any better for most applications. Intel is also wrong, of course: we need 64-bit consumer processors before we'll get 64-bit consumer OSes and applications. The 32-bit 386 was launched years before we ever saw a proper 32-bit OS, for example. Intel wanted the 64-bit consumer world to come from the 64-bit server world, but that has changed and IA64 may now be stuck as an enterprise-only platform.Talk of multiple cores on future processors does give IA64 a chance, though. For instance, we could always see IA64 show up as a secondary core, and over time it might move to play a more central role. That may or may not happen, but regardless of what the desktop enthusiasts might think of Itanium, Intel continues to update the processor line. In case this wasn't already made clear, all of the Itanium chips support 64-bit applications, but they do not support x86-64 applications - at least not natively. Itanium 2 doesn't support x86 code natively either, but runs it through a combination of software emulation and hardware features. The inability to run x86 code with high performance has been a drawback of the IA64 platform since its inception, but the market for Itanium generally isn't too concerned about x86 compatibility.

|

| Click to enlarge |

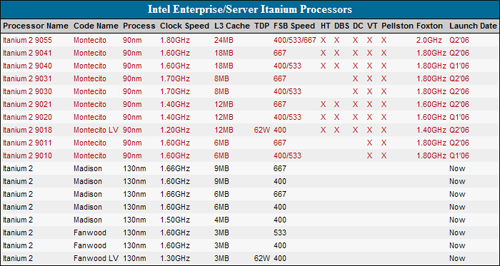

Like the server and workstation parts, Intel has also announced a change in name for the Itanium parts. Future Itanium 2 chips will join the model number club, with the 9000 series currently used for the Montecito-based Itanium 2 chips. Ranging from 9010 up through the 9055, the planned Itanium 2 parts cover a large range of cache sizes, features, clock speeds, and performance. At the low end, the 9010 and 9011 are single core versions of Montecito, with cache sizes and bus speeds that should help them take over the place of last generation's Madison 6MB parts. The model numbers are meant to reflect increasing features and overall performance for the platform, so even though the 9010/9011 are clocked higher than some of the other Montecito chips, the lack of dual cores and the limited L3 cache gives them a lower model number. The dual core additions and other technology in Montecito will have a dramatic impact on computational power, with Intel stating up to a 2.5X increase in computational power relative to Madison-9M. It's not clear whether that's in regards to the 9040 chip or the 9055, though - we would guess they're giving the best case scenario with the 9055.

Some of the other interesting aspects of the Itanium lineup are the bus speeds. With the later model Madison cores supporting up to 667FSB, it's a little odd to see the new cores continuing to support 400 and 533 FSB speeds. The lower speeds may simply be for compatibility with current generation Itanium motherboards. The lack of certain features is also a bit odd. DBS is the Itanium equivalent of Intel Speedstep technology from the desktop and mobile sector. We're not sure why the 9030/9031 and 9010/9011 chips do not include this feature. HyperThreading is also disabled on the same processors, so it may simply be a case of reduced features for a reduced price.

Other features are included on all of the Montecito cores. Pellston is a useful addition, as it allows the processor to detect L3 cache errors and dynamically disable faulty cache lines without requiring a reboot or any administrative intervention. That should certainly increase yields, as the large L3 cache comprises the majority of the die space. While the loss of usable cache might seem like a bad thing, Intel has stated that they will replace processors that develop more than 90 bad cache lines. Even with the smallest 6MB cache chips, that's still less than 0.1% of the total L3 cache. The Vitualization Technology is also present in all the new cores, giving hardware support for certain features that allow concurrently running OSes to be used. Finally, we have the Foxton technology with the listed clock speeds. Foxton allows the processors to run at higher speeds under certain load conditions when the core temperature is below a threshold. Basically, think of it as mild overclocking for the enterprise sector. Most of the chips only support a 200MHz "overclocked" speed, but that's still an 11 to 17% overclock. (The 9030/9031 only sport a 100MHz speed increase - a 6% increase.) The only thing we don't know is how often the higher clock speed can actually be reached. We've seen automatic overclocking tools from others that in practice rarely managed more than a 1% average speed increase.

Montecito is the first Itanium design to switch to 90nm process technology. The switch has allowed Intel to dramatically increase the amount of L3 cache available on the top models. If the Pentium 6xx line's 2MB of cache seems like a lot - there's a law of diminishing returns in respect to cache sizes - the up to 24MB of L3 cache probably seems like hubris. However, increasing cache sizes can help enterprise class servers quite a bit. These systems might have as much as 16 or even 64 GB of RAM, so a paltry 2MB cache can in fact be inadequate for large data sets. Transistor count for the 955 chip is a whopping 1.7 billion transistors - over seven times the size of Smithfield and Presler! What's really amazing is that this is done on a 90nm process. With mainstream chips scaling to 230 million transistors and more on the 65nm process, we have to wonder where Intel will take the Itanium line when they transition it to the new process. Anyone need an Itanium 2 with 48MB of L3 cache? It might be in the woodworks if the blooming L3 sizes of Montecito are any indicator of future trends. Like it or not, you still have to at least respect the ability of any company that can manage to create such a massive processor as the Itanium.

21 Comments

View All Comments

yorthen - Monday, September 12, 2005 - link

Yes, I've heard a lot about VT and AMT but never found any good explanation of how it actually works. I understand that using VT will enable Xen to run unmodified OSes, but what is it that VT does that a normal processor can not, and how does it compare to AMD's virtualisation-technology?And what about AMT, which is supposed to provide OS-independent management capabilities, what kind of operations does it allow?