AMD 3rd Gen EPYC Milan Review: A Peak vs Per Core Performance Balance

by Dr. Ian Cutress & Andrei Frumusanu on March 15, 2021 11:00 AM ESTDisclaimer June 25th: The benchmark figures in this review have been superseded by our second follow-up Milan review article, where we observe improved performance figures on a production platform compared to AMD’s reference system in this piece.

Compiling LLVM, NAMD Performance

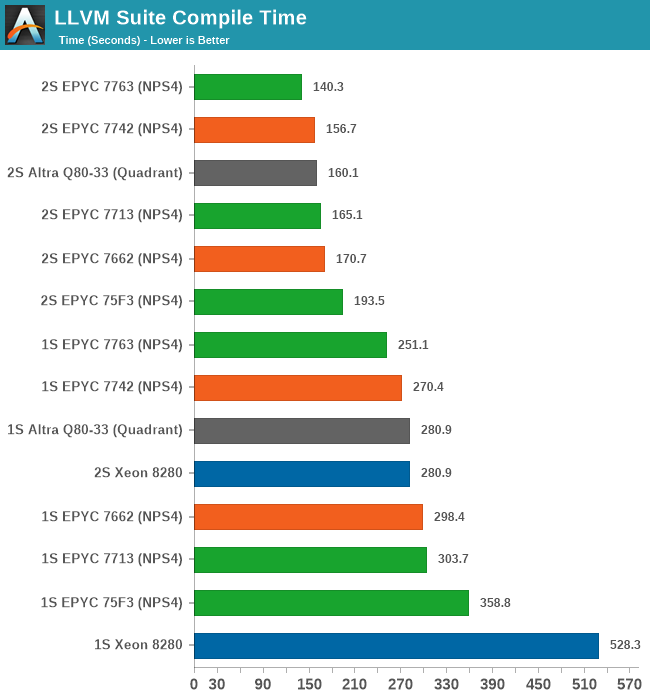

As we’re trying to rebuild our server test suite piece by piece – and there’s still a lot of work go ahead to get a good representative “real world” set of workloads, one more highly desired benchmark amongst readers was a more realistic compilation suite. Chrome and LLVM codebases being the most requested, I landed on LLVM as it’s fairly easy to set up and straightforward.

git clone https://github.com/llvm/llvm-project.gitcd llvm-projectgit checkout release/11.xmkdir ./buildcd ..mkdir llvm-project-tmpfssudo mount -t tmpfs -o size=10G,mode=1777 tmpfs ./llvm-project-tmpfscp -r llvm-project/* llvm-project-tmpfscd ./llvm-project-tmpfs/buildcmake -G Ninja \ -DLLVM_ENABLE_PROJECTS="clang;libcxx;libcxxabi;lldb;compiler-rt;lld" \ -DCMAKE_BUILD_TYPE=Release ../llvmtime cmake --build .We’re using the LLVM 11.0.0 release as the build target version, and we’re compiling Clang, libc++abi, LLDB, Compiler-RT and LLD using GCC 10.2 (self-compiled). To avoid any concerns about I/O we’re building things on a ramdisk. We’re measuring the actual build time and don’t include the configuration phase as usually in the real world that doesn’t happen repeatedly.

For the new Milan chips, the results are a bit mixed. The higher-power 7763 takes a lead with a +10.5% improvement over the 7742, however the 7713 doesn’t manage to keep up with that predecessor.

The 1S vs 2S scores are interesting as the 2S figures showcase the new Milan chips in a better light due to the higher single-threaded performance of the Zen3 cores. The compilation here also has linking phases which are single-thread performance bottle-necked. This results in scenarios such as the 7713 losing to the 7662 in 1S comparisons, however winning out against the same chip in the 2S comparison, as it’s able to make that advantage count for more.

It’s also great to see the 75F3 keep up with the 64-core counterparts at around 72% of the top-SKU performance.

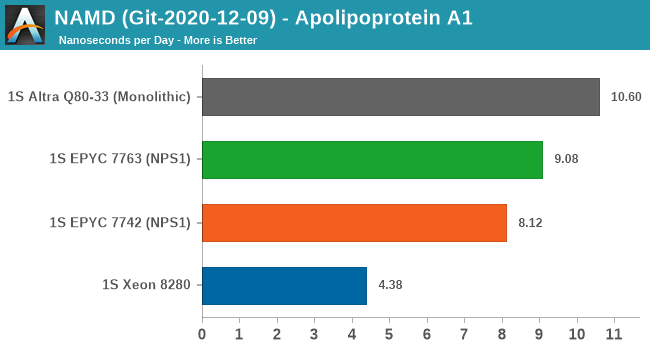

Finally, in NAMD, this is more of a core-local compute workload. We see the 7763 outperform the 7742 by +11.8%, however the Milan chip is still outperformed by the higher core compute capacity of the 80-core Altra chip.

Generally, I have my reservations about NAMD as a benchmark due to its multicore vs MPI variants and scaling anomalies, on top of the whole topic of the benchmark having a completely different algorithm for AVX512 processors.

120 Comments

View All Comments

eva02langley - Monday, March 15, 2021 - link

You probably looking at the blue lines (Intel)... just saying...Targon - Monday, March 15, 2021 - link

Compared to what? Core count not increasing, but Zen3 is still a big improvement when it comes to IPC compared to Zen2.mode_13h - Monday, March 15, 2021 - link

We can hope that they find some microcode fixes to improve power allocation, and maybe a mid-cycle refresh with an updated I/O die.Spunjji - Friday, March 19, 2021 - link

How surprising, an Intel fanboy is unimpressed.Wilco1 - Sunday, March 21, 2021 - link

It's actually an impressive improvement. However Milan is getting power and memory bandwidth limited. It will take a new process and DDR5 to achieve significantly more performance.ballsystemlord - Monday, March 15, 2021 - link

Spelling and grammar errors:"As the first generation Naples was launched, it offered impressive some performance numbers."

Rearange words:

"As the first generation Naples was launched, it offered some impressive performance numbers."

"All of these processors can be use in dual socket configurations."

"used" not "use":

"All of these processors can be used in dual socket configurations."

"... I see these to chips as the better apples-to-apples generational comparison, ..."

"two" not "to":

"... I see these two chips as the better apples-to-apples generational comparison, ..."

"There is always room for improvement, but if AMD equip themselves with a good IO update next generation,..."

Missing "s":

"There is always room for improvement, but if AMD equips themselves with a good IO update next generation,..."

eva02langley - Monday, March 15, 2021 - link

If business don't buy EPYC by then, than they deserve all the issues coming with Intel CPUs.Otritus - Monday, March 15, 2021 - link

Milan's IO die really seems to be the Achilles heel of these CPUs. Perhaps AMD should have segregated the line up into superior memory performance and features Milan IO die and superior compute performance (but inferior features) Rome IO die.Targon - Monday, March 15, 2021 - link

The Zen4 generation will make the move to DDR5 memory, so new memory controller, socket, and other aspects. Also, as time goes on, the contracts with Global Foundries for how much they make for AMD will expire. As it stands now, the use of Global is entirely to fulfill the contracts and avoid paying any early termination fees.Calin - Tuesday, March 16, 2021 - link

TSMC still can not make enough chiplets (I think its production is sold until 2023).Using Global Foundry IO dies means AMD can make one 8+1 instead of 8 processors (or 4+1 instead of 4).