Intel's 925X & LGA-775: Are Prescott 3.6 and PCI Express Graphics any Faster?

by Anand Lal Shimpi on June 21, 2004 12:05 PM EST- Posted in

- CPUs

PCI Express Graphics

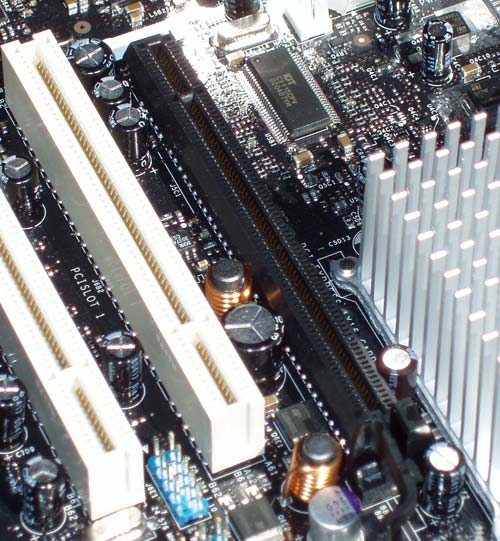

When the first 440LX motherboards hit the streets with AGP support, it was so exciting to finally have a new slot on motherboards that had been littered with PCI and ISA slots for so long. The excitement of having that new slot is once again duplicated with the new PCI Express x16 slots that have found their way onto 925X and 915 boards. So, what is the big deal behind PCI Express as a graphics bus?For starters, AGP/PCI are parallel and PCI Express is serial. What this means is that rather than sending multiple bits at a time, PCI Express only sends one bit per clock in each direction. Mildly confusing is the fact that multiple PCI Express lanes can be connected to one device (giving us PCI Express x4, x8, x16 and so on). Why is an array of serial interfaces different than a parallel interface? We're glad that you asked.

Signaling is generally more difficult using a parallel communication protocol. One of the problems is making sure that all the data being sent in parallel makes it to its destination in a timely fashion (along with all the signaling and control flow data that are included with each block of data sent). This makes circuit board layout a little tricky sometimes, and forces us to keep signaling over cables to relatively short distances using equal length lines (e.g. an IDE cable). The fact that so much care needs to be taken about getting all the bits to their destination intact and together also limits signaling speed. Standard 32bit PCI speed is 33MHz. DDR memory is connected to the rest of the system in parallel and runs at a few hundred MHz. On the other hand, one PCI Express lane is designed to scale well beyond 2GHz.

The downside of this enhanced speed and bandwidth is bus utilization. Obviously, if we are sending data serially, we are only sending one bit every clock cycle. This is 32 times less data per clock cycle than the current PCI bus. Add on to that, the fact that all low level signaling and control information need to come over the same single line (well, PCIe actually uses a differential signal - two lines for one bit - but who's counting). On top of that, serial communications don't really react well to long strings of ones or long strings of zeros, so extra signaling overhead is implemented to handle those situations better. Parallel signaling has its share of problems, but a serial bus will always have lower utilization. Even in cases where a serial bus has a bandwidth advantage over a parallel bus, latency may still be higher with the serial bus.

Fortunately, PCI Express is a very nice improvement over the current PCI bus. It's point to point, so we don't need to deal with bus arbitration; its serial, so it will be easy to route on a motherboard (with just four data wires for PCI Express x1) and will scale up in speed more easily. It's also backwards compatible with PCI from the software's perspective (which means developers will have an easier time porting their software).

Unfortunately, it will be harder for users to "feel" the advantages of PCI Express over PCI, especially while the transition is going on and motherboards will be supporting "legacy" PCI slots and busses, and companies will have to find the sweet spot between their PCI and PCI Express (or AGP and PCI Express) based cards. Software won't immediately take advantage of the added bandwidth because it is common practice (and simply common sense) to develop for the widest audience and highest level of compatibility when dealing with any type of computing.

Even after game developers make the most of PCI Express x16 in its current form, end users won't see that much benefit - there's a reason that high end GPUs have huge numbers of internal registers and a 35GB/s connection to hundreds of megs of local GDDR3. By the time games come out that would even think of using 4GB/s up from and 4GB/s down to main memory, we'll have even more massive amounts of still faster RAM strapped on to graphics boards. The bottom line is that the real benefit will present itself to applications that require communication with the rest of the system, like video streaming and editing, or offloading some other type of work from the CPU onto the graphics card.

39 Comments

View All Comments

Pete - Monday, June 21, 2004 - link

*Sweet.I'm thinking those 6800U benches are probably input errors on AT's part, as most other sites show:

1) scores nowhere near that high, especially at that res, &

2) A64s outperforming P4s.

You may be using a very GPU-limited, or at least not-CPU-limited demo, though.

Pete - Monday, June 21, 2004 - link

Swet, fancy Moses! Anand, can you explain the ginormous "vanilla" Far Cry gains by the 6800U? Was IQ the same as the 61.11s (still "point-filtery" in some places compared to ATi) with such prodigious (70%!) gains?justly - Monday, June 21, 2004 - link

AnandI don’t care if that info is strait from Intel or not, it is plain wrong, and I think you are wrong for not questioning this and more so by putting it in print.

Conduction is increased with pressure (be it heat or electrical) but for downward force to affect electrical contact/conduction of a CPU in a socket the pins would have to make contact at their tip. A ZIF socket does not do this, it makes contact on the side of the pins when a sliding plate forces the pin against a contact. If contact was made at the tip of the pins then the CPU would not lay flat against the top of the socket when inserted. This would also prevent aftermarket adapters like this one from powerleap http://www.powerleap.com/PL-iP4.html from being used between the CPU and the socket because it would prevent the pins from contacting.

Once the CPU is inserted into the socket and the lever is locked down the CPU is locked flat against the socket so even if downward pressure was applied it would only help with heat transfer.

Runamile - Monday, June 21, 2004 - link

I agree with #4. The ZIF socket takes care of all contact needed. And as #15 said, there is a sideways force that makes contact with the pins. Ever seen that Tom's Hardware video with the PIII and P4 running w/o a heatsink, albeit very slowly due to freak overheating? They did 'need' the extreame downwards force. Thats all for heat transfer. Period.All in all, very enlightening article. Basicly shows that the entire 925X/LGA-775/Prescott/DDR2/PCI-X release is a mediocre waste of our money. At least for the time being.

paulvds - Monday, June 21, 2004 - link

478 pin electrical contact is by a pinchingsideway force on the pins produced by the ZIF

lever, top down force is totaly irrelevant!

How could you gobble-up that marketing nonsense ?

You advise 'business users' to chose AMD...

Also total nonsense, any entry level value processor will do, they don't need teraMips...

You should go write poetry or novells...

danidentity - Monday, June 21, 2004 - link

Great article Anand...Do you have any info on the supposed Intel-imposed 10% overclocking limit described in Tom's Hardware Guide's LGA775 article here?

http://www.tomshardware.com/motherboard/20040619/s...

retrospooty - Monday, June 21, 2004 - link

Nice article...It just basically proves what we have all suspected all along. DDR2, PCI express, and socket 775 dont offer any compelling reason to upgrade (for now anyhow).

Of course in the future (maybe 2005 if we're lucky), when graphics cards can utilize the extra bandwidth of PCI express it will be faster than AGP 8x.

Of course in the future (maybe 2005 if we're lucky), when DDR2 800 mhz is standard, it will be faster than low latency DDR400

Of course in the future (even if hell freezes over) the message is clear socket 775 has failed :D

LOL !

T8000 - Monday, June 21, 2004 - link

I think the pins in the LGA775 socket are a lot longer then the CPU needs.So adding some kind of non conductive shim around the pins could make this socket a lot more reliable.

It could be as simple as a thin plastic plate with 775 holes in it, that could be inserted before the CPU, leaving just enough pin length to mount the CPU, without the risk of bending those pins.

Anand Lal Shimpi - Monday, June 21, 2004 - link

phobsThanks for the heads up, we added the last two pages of benchmarks after the fact and I forgot to remove that line :)

Take care,

Anand

Anand Lal Shimpi - Monday, June 21, 2004 - link

justlyThat information is straight from Intel - the force of the heatsink was used to maximize heat transfer, but not that much force is necessary to maximize heat transfer. The rest of the force is needed to ensure that there is good contact between the pins and their contacts.

Take care,

Anand