The AMD Ryzen Threadripper 1950X and 1920X Review: CPUs on Steroids

by Ian Cutress on August 10, 2017 9:00 AM ESTFeeding the Beast

When frequency was all that mattered for CPUs, the main problem became efficiency, thermal performance, and yields: the higher the frequency was pushed, the more voltage needed, the further outside the peak efficiency window the CPU was, and the more power it consumed per unit work. For the CPU that was to sit at the top of the product stack as the performance halo part, it didn’t particularly matter – until the chip hit 90C+ on a regular basis.

Now with the Core Wars, the challenges are different. When there was only one core, making data available to that core through caches and DRAM was a relatively easy task. With 6, 8, 10, 12 and 16 cores, a major bottleneck suddenly becomes the ability to make sure each core has enough data to work continuously, rather than waiting at idle for data to get through. This is not an easy task: each processor now needs a fast way of communicating to each other core, and to the main memory. This is known within the industry as feeding the beast.

Top Trumps: 60 PCIe Lanes vs 44 PCIe lanes

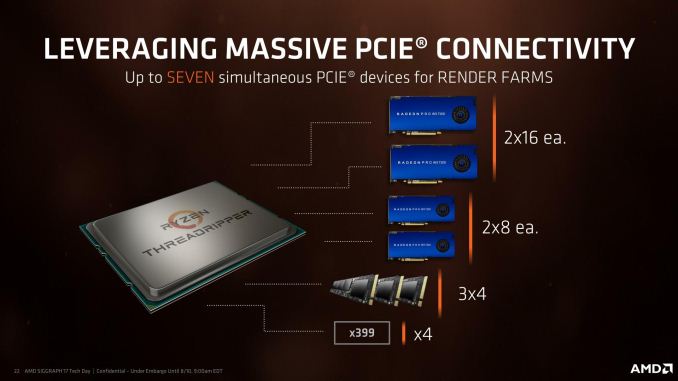

After playing the underdog for so long, AMD has been pushing the specifications of its new processors as one of the big selling points (among others). Whereas Ryzen 7 only had 16 PCIe lanes, competing in part against CPUs from Intel that had 28/44 PCIe lanes, Threadripper will have access to 60 lanes for PCIe add-in cards. In some places this might be referred to as 64 lanes, however four of those lanes are reserved for the X399 chipset. At $799 and $999, this competes against the 44 PCIe lanes on Intel’s Core i9-7900X at $999.

The goal of having so many PCIe lanes is to support the sort of market these processors are addressing: high-performance prosumers. These are users that run multiple GPUs, multiple PCIe storage devices, need high-end networking, high-end storage, and as many other features as you can fit through PCIe. The end result is that we are likely to see motherboards earmark 32 or 48 of these lanes for PCIe slots (x16/x16, x8/x8/x8/x8, x16/x16/x16, x16/x8/x16/x8), followed by a two or three for PCIe 3.0 x4 storage via U.2 drives or M.2 drives, then faster Ethernet (5 Gbit, 10 Gbit). AMD allows each of the PCIe root complexes on the CPU, which are x16 each, to be bifurcated down to x1 as needed, for a maximum of 7 devices. The 4 PCIe lanes going to the chipset will also support several PCIe 3.0 and PCIe 2.0 lanes for SATA or USB controllers.

Intel’s strategy is different, allowing 44 lanes into x16/x16/x8 (40 lanes) or x16/x8/x16/x8 (40 lanes) or x16/x16 to x8/x8/x8x8 (32 lanes) with 4-12 lanes left over for PCIe storage or faster Ethernet controllers or Thunderbolt 3. The Skylake-X chipset then has an additional 24 PCIe lanes for SATA controllers, gigabit Ethernet controllers, SATA controllers and USB controllers.

Top Trumps: DRAM and ECC

One of Intel’s common product segmentations is that if a customer wants a high core count processor with ECC memory, they have to buy a Xeon. Typically Xeons will support a fixed memory speed depending on the number of channels populated (1 DIMM per channel at DDR4-2666, 2 DIMMs per channel at DDR4-2400), as well as ECC and RDIMM technologies. However, the consumer HEDT platforms for Broadwell-E and Skylake-X will not support these and use UDIMM Non-ECC only.

AMD is supporting ECC on their Threadripper processors, giving customers sixteen cores with ECC. However, these have to be UDIMMs only, but do support DRAM overclocking in order to boost the speed of the internal Infinity Fabric. AMD has officially stated that the Threadripper CPUs can support up to 1 TB of DRAM, although on close inspection it requires 128GB UDIMMs, which max out at 16GB currently. Intel currently lists a 128GB limit for Skylake-X, based on 16GB UDIMMs.

Both processors run quad-channel memory at DDR4-2666 (1DPC) and DDR4-2400 (2DPC).

Top Trumps: Cache

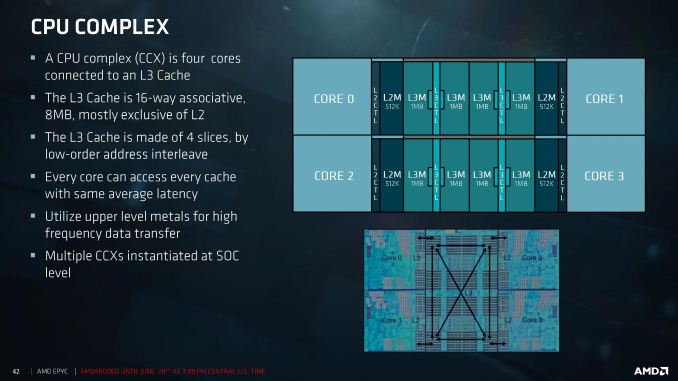

Both AMD and Intel use private L2 caches for each core, then have a victim L3 cache before leading to main memory. A victim cache is a cache that obtains data when it is evicted from the cache underneath it, and cannot pre-fetch data. But the size of those caches and how AMD/Intel has the cores interact with them is different.

AMD uses 512 KB of L2 cache per core, leading to an 8 MB of L3 victim cache per core complex of four cores. In a 16-core Threadripper, there are four core complexes, leading to a total of 32 MB of L3 cache, however each core can only access the data found in its local L3. In order to access the L3 of a different complex, this requires additional time and snooping. As a result there can be different latencies based on where the data is in other L3 caches compared to a local cache.

Intel’s Skylake-X uses 1MB of L2 cache per core, leading to a higher hit-rate in the L2, and uses 1.375MB of L3 victim cache per core. This L3 cache has associated tags and the mesh topology used to communicate between the cores means that like AMD there is still time and latency associated with snooping other caches, however the latency is somewhat homogenized by the design. Nonetheless, this is different to the Broadwell-E cache structure, that had 256 KB of L2 and 2.5 MB of L3 per core, both inclusive caches.

347 Comments

View All Comments

Ian Cutress - Thursday, August 10, 2017 - link

Still a WIP, was hoping to have it finished, but will probably early next week.BOBOSTRUMF - Thursday, August 10, 2017 - link

Good review but I see a lot of testes optimized for 2-4 cores. Also I want a test with gaming, rendering and compression (or other many intensive tasks) at the same time, this will clearly differentiate this beast from other 4-6 cores CPU's;Unfortunately for Intel, his greed really shows now. Although core still has about 5-10% more IPC compared to Ryzen, the power consumption per core is about 5-15% higher (al lower frequency) and with 10-18 cores this really shows. They had a very competitive tick-tock strategy when they had absolutely no competition and now after more than three years they are still stuck in 14nm. If they were smarter and created by now just one fab on 8 or 10 nm for the CPU's with many cores things were more simple for them today. In 8 nm, skylake x would had allowed 18 cores on 3.2-3.6Ghz, and not 2.6 as they are doing now.

So they save 3-4 billions dollars not building a 8nm fab but will lose more than this when enthusiast marked will side with AMD.

Please be smarter in future Intel, Samsung and TSMC already have 8 nm FABS while you...

looncraz - Thursday, August 10, 2017 - link

Page 2: "Whereas Ryzen 7 only had 16 PCIe lanes"Ryzen 7 has 32 pci-e 3.0 lanes on die, one 8 lane controller disabled, leaving 24 lanes enabled. Four are then reserved for the chipset, leaving 20 PCI-e lanes usable for direct connectivity.

Ian Cutress - Thursday, August 10, 2017 - link

Of which only 16 are reserved for GPUs. Which is how PCIe lanes from CPUs have been characterized for decades.bongey - Thursday, August 10, 2017 - link

From the site that tried to tell you a pentium 4 was a better cpu than a athlon 64.amdwilliam1985 - Monday, August 14, 2017 - link

pentium 4 is better than athlon 64 as a space heater ;)brucek2 - Thursday, August 10, 2017 - link

re: page 1's "AMD recommends liquid cooling at a bare minimum" - if liquid cooling is the "bare minimum", what cooling is considered "pretty good"? Are we all supposed to be readying liquid nitrogen setups?Hurr Durr - Friday, August 11, 2017 - link

Look at the TDPs across the boeard. Of course we are!Gavin Bonshor - Thursday, August 10, 2017 - link

Great review as always :) - So it's effectively a great all-around CPU for streaming, gaming, and rendering in programs which utilises more than 8 cores...I think that's win, especially with ECC memory supportpeevee - Thursday, August 10, 2017 - link

Why do you need ECC at home?