AMD Zen Microarchitecture: Dual Schedulers, Micro-Op Cache and Memory Hierarchy Revealed

by Ian Cutress on August 18, 2016 9:00 AM ESTDeciphering the New Cache Hierarchy

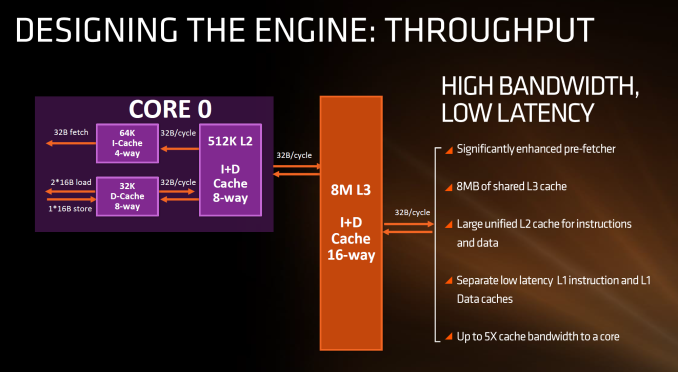

The cache hierarchy is a significant deviation from recent previous AMD designs, and most likely to its advantage. The L1 data cache is both double in size and increased in associativity compared to Bulldozer, as well as being write-back rather than write-through. It also uses an asymmetric load/store implementation, identifying that loads happen more often than stores in the critical paths of most work flows. The instruction cache is no longer shared between two cores as well as doubling in associativity, which should decrease the proportion of cache misses. AMD states that both the L1-D and L1-I are low latency, with details to come.

The L2 cache sits at half a megabyte per core with 8-way associativity, which is double that of Intel’s Skylake which has 256 KB/core and is only 4-way. On the other hand, Intel’s L3/LLC on their high-end Skylake SKUs is at 2 MB/core or 8 MB/CPU, whereas Zen will feature 1 MB/core and both are at 16-way associativity.

Edit 7:18am: Actually, the slide above is being slightly evasive in its description. It doesn't say how many cores the L3 cache is stretched over, or if there is a common LLC between all cores in the chip. However, we have recieved information from a source (which can't be confirmed via public AMD documents) that states that Zen will feature two sets of 8MB L3 cache between two groups of four cores each, giving 16 MB of L3 total. This would means 2 MB/core, but it also implies that there is no last-level unified cache in silicon across all cores, which Intel has. The reasons behind something like this is typically to do with modularity, and being able to scale a core design from low core counts to high core counts. But it would still leave a Zen core with the same L3 cache per core as Intel.

| Cache Levels | ||||

| Bulldozer FX-8150 |

Zen | Broadwell-E i7-6950X |

Skylake i7-6700K |

|

| L1 Instruction | 64 KB 2-way per module |

64 KB 4-way | 32 KB 8-way | 32 KB 8-way |

| L1 Data | 16 KB 4-way Write Through |

32 KB 8-way Write Back |

32 KB 8-way Write-Back |

32 KB 8-way Write-Back |

| L2 | 2 MB 16-way per module |

512 KB 8-way | 256 KB 8-way | 256 KB 4-way |

| L3 | 1 MB/core 64-way |

1 or 2 MB/core ? 16-way |

2.5 MB/core 16/20-way |

2 MB/core 16-way |

What this means, between the L2 and the L3, is that AMD is putting more lower level cache nearer the core than Intel, and as it is low level it becomes separate to each core which can potentially improve single thread performance. The downside of bigger and lower (but separate) caches is how each of the cores will perform snoop in each other’s large caches to ensure clean data is being passed around and that old data in L3 is not out-of-date. AMD’s big headline number overall is that Zen will offer up to 5x cache bandwidth to a core over previous designs.

216 Comments

View All Comments

pikunsia - Friday, August 19, 2016 - link

Yeah, but let's recall also Intel used AMD64 architecture (since the Opterons).atomsymbol - Monday, August 22, 2016 - link

It is true there's no significant difference between ZEN and Skylake.bobhumplick - Thursday, August 30, 2018 - link

of course they copied intel. its just a dual socket system shrunk to fit on a single die. and thats exactlyw hat they should have done. its exactly what intel should have done when they made the p4. they should have copied themselves. you dont try to push a new arch like p4 or fx when another desing is so dominate. you have to make the cpu fit the software not the other way around. also intel learned that lesson again with epyc (well i guess at the same time as the p4 thing). you have to have something that will run todays software, if you can add functionality to become the new standard in the future then great but it must fit todays software first and if the compeitions cpu fits todays software better then they will set the trends not youMichael Bay - Thursday, August 18, 2016 - link

WHENCygni - Thursday, August 18, 2016 - link

READMichael Bay - Friday, August 19, 2016 - link

I WANT DATESTheinsanegamerN - Friday, August 19, 2016 - link

BETTER LOSE WEIGHTMichael Bay - Saturday, August 20, 2016 - link

YOU GOT MEKaboose - Thursday, August 18, 2016 - link

"It’s worth nothing that AMD said"3rd to last paragraph on the final page, should probably read

"it's worth NOTING that AMD said".

Ian Cutress - Thursday, August 18, 2016 - link

Ha! That's 2am brain drain for you. Fixed :)