AMD Zen Microarchitecture: Dual Schedulers, Micro-Op Cache and Memory Hierarchy Revealed

by Ian Cutress on August 18, 2016 9:00 AM ESTDeciphering the New Cache Hierarchy

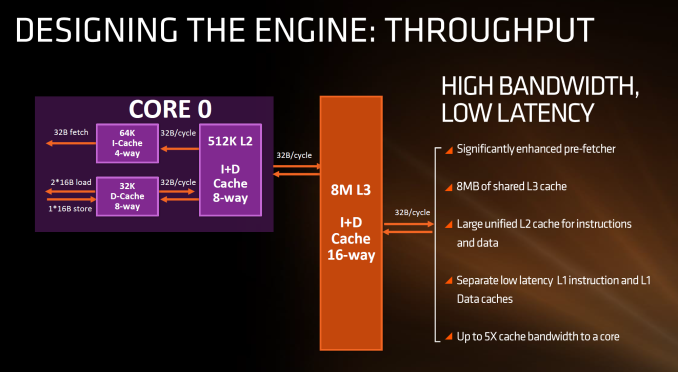

The cache hierarchy is a significant deviation from recent previous AMD designs, and most likely to its advantage. The L1 data cache is both double in size and increased in associativity compared to Bulldozer, as well as being write-back rather than write-through. It also uses an asymmetric load/store implementation, identifying that loads happen more often than stores in the critical paths of most work flows. The instruction cache is no longer shared between two cores as well as doubling in associativity, which should decrease the proportion of cache misses. AMD states that both the L1-D and L1-I are low latency, with details to come.

The L2 cache sits at half a megabyte per core with 8-way associativity, which is double that of Intel’s Skylake which has 256 KB/core and is only 4-way. On the other hand, Intel’s L3/LLC on their high-end Skylake SKUs is at 2 MB/core or 8 MB/CPU, whereas Zen will feature 1 MB/core and both are at 16-way associativity.

Edit 7:18am: Actually, the slide above is being slightly evasive in its description. It doesn't say how many cores the L3 cache is stretched over, or if there is a common LLC between all cores in the chip. However, we have recieved information from a source (which can't be confirmed via public AMD documents) that states that Zen will feature two sets of 8MB L3 cache between two groups of four cores each, giving 16 MB of L3 total. This would means 2 MB/core, but it also implies that there is no last-level unified cache in silicon across all cores, which Intel has. The reasons behind something like this is typically to do with modularity, and being able to scale a core design from low core counts to high core counts. But it would still leave a Zen core with the same L3 cache per core as Intel.

| Cache Levels | ||||

| Bulldozer FX-8150 |

Zen | Broadwell-E i7-6950X |

Skylake i7-6700K |

|

| L1 Instruction | 64 KB 2-way per module |

64 KB 4-way | 32 KB 8-way | 32 KB 8-way |

| L1 Data | 16 KB 4-way Write Through |

32 KB 8-way Write Back |

32 KB 8-way Write-Back |

32 KB 8-way Write-Back |

| L2 | 2 MB 16-way per module |

512 KB 8-way | 256 KB 8-way | 256 KB 4-way |

| L3 | 1 MB/core 64-way |

1 or 2 MB/core ? 16-way |

2.5 MB/core 16/20-way |

2 MB/core 16-way |

What this means, between the L2 and the L3, is that AMD is putting more lower level cache nearer the core than Intel, and as it is low level it becomes separate to each core which can potentially improve single thread performance. The downside of bigger and lower (but separate) caches is how each of the cores will perform snoop in each other’s large caches to ensure clean data is being passed around and that old data in L3 is not out-of-date. AMD’s big headline number overall is that Zen will offer up to 5x cache bandwidth to a core over previous designs.

216 Comments

View All Comments

breweyez - Friday, August 19, 2016 - link

You sure sound like an intel fanboysmilingcrow - Friday, August 19, 2016 - link

Recognising and acknowledging that AMD's CPUs were in the doldrums for 10 long years doesn't make you an Intel fanboy but a realist. Ignoring that inconvenient truth does though make you an AMD fanboy.Come on Zen although the amount of crap that the fanboys on both sides will spout when it is released will be immense. I will keep off the forums.

jjj - Friday, August 19, 2016 - link

There are no volumes above 350$, anything above that might as well not exist. Zen more or less needs to compete with Skylake while offering 2x the cores. If they have some higher clocks SKU above 350$, that could work but people need to be able to afford Zen,otherwise what's the point. Zen shouldn't be a huge die so AMD should be able to offer reasonable prices. Ofc there is no need to offer 8 cores high clocks at 200$ ,that's too far.BMNify - Friday, August 19, 2016 - link

if AMD cant get far better throughput than skylake with twice the zen cores , then they have no right to stay in business after all these missteps and the clammer of Jim Keller PR a DEC engineer who helped design the Alpha 21164 and 21264 processors then how can you ever expect to get a UHD1 rec.2020 capable CPU/GPU by even 2020.smilingcrow - Friday, August 19, 2016 - link

A lot of people are hoping that will be their strategy but it depends also on yields and final clock speeds.If they have low yields for the high clock speed parts they might well push that as an FX part and price it at $500 or more. It would still be a good halo product.

Also if they have a really good 8 core at $350 or under it will impact how much they can ask for the higher volume quad core parts.

If they sell too cheap they might have trouble matching the demand.

It's quite a juggling act to balance all that.

azazel1024 - Friday, August 19, 2016 - link

It sounds very good in fact. My biggest thing is overall system cost. Next is performance and finally noise and power consumption. Sure, I've love what a 10 core Core processor can level, but I don't really need it. I can get by with my Ivy Bridge i5-3570, but if I am going to upgrade, I'd like it to be for a nice boost in performance. Compared to my Ivy Bridge, I could be okay with a very small loss in single threaded performance, but I'd like a big gain in multithreaded performance. That to me says that Zen needs to bring, compared to my i5-3570, at least 90% single thread performance and at least 70-80% of the per core performance under multithreaded workloads. Then deliver it with roughly a $400 overall platform cost (between an "entry" mid-grade board and the CPU, ignoring RAM costs). Do that and they have a buyer from me. Don't and I'll probably look at the lowest level Hexacore Skylake-E processor once they come out next year.Basically I need 8 core Zen to be at least a little faster, averaged out, than current 6 core Broadwell-E, yet come in somewhat under the price of 6 core Broadwell-E. That would be enough extra performance to justify an upgrade from my current system early next year.

AndrewJacksonZA - Thursday, August 18, 2016 - link

I am disappointed that they are only releasing Zen in 2017 as I really am looking to upgrade my PC towards the end of the year. But hey, what's another few months, I guess? *siiiiiiiiiiiiiiigh*AndrewJacksonZA - Thursday, August 18, 2016 - link

Aaargh! Where's the edit button please guys????Just to be clear, I'm not waiting /to buy Zen/, I'm waiting for it to come out so that proper, independent tests can show what CPU would be better suited to my pocket and my needs.

melgross - Thursday, August 18, 2016 - link

As always, I've hopes that this will be what AMD says it will, but little confidence that it will.silverblue - Thursday, August 18, 2016 - link

The micro ops cache is a bit of a surprise; I believe the Steamroller preview mentioned that particular design was getting such a cache. Perhaps it didn't in the end.