ARM Unveils Next Generation Bifrost GPU Architecture & Mali-G71: The New High-End Mali

by Ryan Smith on May 30, 2016 7:00 AM ESTThe Bifrost Core: Decoupled

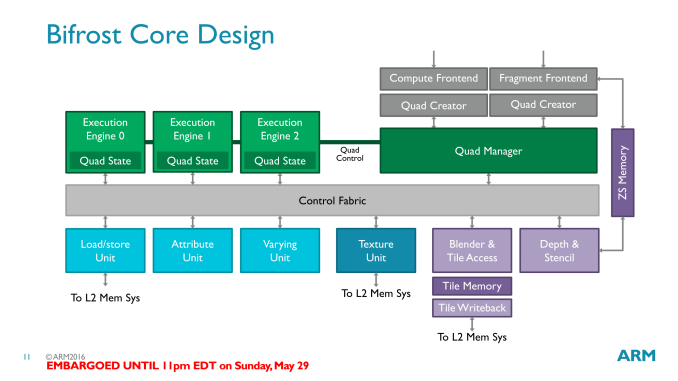

Finally moving up to the 500ft view, we have the logical design of a single Bifrost core. Augmenting the changes we’ve discussed so far at the quad/execution engine level, ARM has made a number of changes to how the rest of the architecture works, and how all of this fits together as a whole.

First and foremost, a single Bifrost core contains 3 quad execution engines. This means that a single core is at any time executing up to 12 FMAs, spread over the aforementioned 3 quads. These quads are in turn fed by the core’s thread management frontend (now called a Quad Manager), which combined with the other frontends issues work to all of the functional units throughout the core.

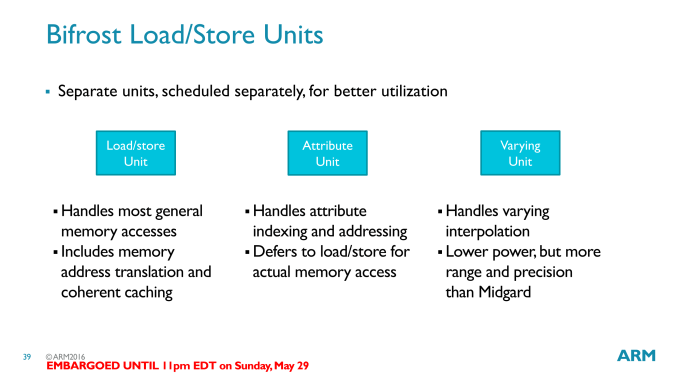

As we’ve now seen the quad execution engines, insightful readers might have noticed that the execution engines are surprisingly sparse. They contain ALUs, register files, and little else. In most other architectures – including Midgard – there are more functional units organized within the execution engines, and this is not the case for Bifrost. Instead the load/store unit, texture unit, and other units have been evicted from the execution engines and placed as separate units along the control fabric.

Along with the shift from ILP to TLP, this is one of the more significant changes in Bifrost as compared to Midgard. Not unlike the TLP shift then, much of this change is driven by resource utilization. These units aren’t used as frequently as the ALUs, and this is especially the case as shader programs grow in length. As a result rather than placing this hardware within the execution engines and likely having it underutilized, ARM has moved them to separate units that are shared by the whole core.

The one risk here is now that there’s contention for these resources, but in practice it should not be much of an issue. Comparatively speaking, this is relatively similar to NVIDIA’s SMs, where multiple blocks of ALUs share load/store and texture units. Meanwhile this should also simplify core design a bit; only a handful of units have L2 cache data paths, and all of those units are now outside of execution engines.

Overall these separated units are not significantly different from their Midgard counterparts, and the big change here is merely their divorce from the execution engines. The texture unit, for example, still offers the same basic feature sets and throughput as Midgard’s, according to ARM.

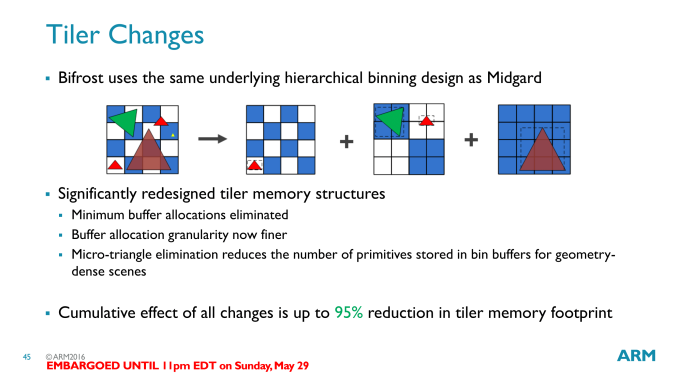

Meanwhile something that has seen a significant overhaul compared to Midgard is ARM’s geometry subsystem. Bifrost still uses hierarchical tiling to bin geometry into tiles to work on it. However ARM has gone through quite a bit of effort here to reduce the memory usage of the tiler, as high resolution screens and higher geometry complexity was pushing up the memory usage of the tiler, and ultimately hurting performance and power efficiency.

Bifrost implements a much finer grained memory allocation system, one that also does away entirely with minimum allocation requirements. This keeps memory consumption down by reducing the amount of overhead from otherwise oversized buffers.

But perhaps more significant is that ARM has implemented a micro-triangle discard accelerator into Bifrost. By eliminating sub-pixel triangles that can’t be seen early on, ARM no longer needs to store those tringles in the tiler, further reducing memory needs. Overall, ARM is reporting that Bifrost’s tiler changes are reducing tiler memory consumption by up to 95%.

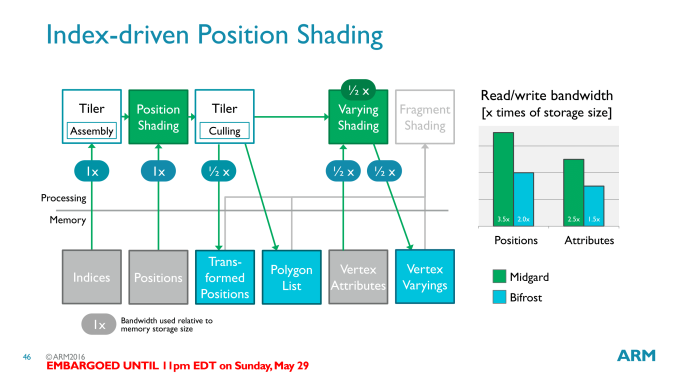

Along similar lines, ARM has also targeted vertex shading memory consumption for optimization. New to Bifrost is a feature ARM is calling Index-Driven Position Shading, which takes advantage of some of the aforementioned tiler changes to reduce the amount of memory bandwidth consumed there. ARM’s estimates put the total bandwidth savings for position shading at around 40%, given that only certain steps of the process can be optimized.

Finally, at the opposite end of the rendering pipeline we have Bifrost’s ROPs, or as ARM labels them, the blending unit and the depth & stencil unit. While these units take a similar direction as the texture unit – there are no major overhauls here – ARM has confirmed that Bifrost’s blending unit does offer some new functionality not found in Midgard’s. Bifrost’s blender can now blend FP16 targets, whereas Midgard was limited to integer targets. The inclusion of floating point blends not only saves ARM a conversion – Midgard would have to covert FP16s to integer RGBA – but the native FP16 blend means that precision/quality should be improved as well.

FP16 blends have a throughput of 1 pixel/clock, just like integer blends, so these are full speed. On that note, Bifrost’s ROP hardware does scale with the core count, so virtually every aspect of the architecture will scale up with larger configurations. Given what Mali-G71 can scale to, this means that the current Bifrost implementation can go up to 32px/clock.

57 Comments

View All Comments

Andrei Frumusanu - Monday, May 30, 2016 - link

> it's cheaper this way than buying license to modify these cores (and you have to add R&D costs of modifying uarch).There is no such license. ARM does not allow vendors to modify the licensed micro-architectures, even on the newly announced license it's ARM themselves which do the modifications, not giving vendors access to change the RTL.

http://www.anandtech.com/show/10366/arm-built-on-c...

Tabalan - Monday, May 30, 2016 - link

I meant architecture license, custom design cores. My bad, used wrong phrase, thanks for pointing that out.Shadow7037932 - Monday, May 30, 2016 - link

Samsung sells the Exynos, but vendors are unlikely to jump ship from Qualcomm because the OEMs already know the Qualcomm stuff well.FullmetalTitan - Monday, May 30, 2016 - link

Also a bit of global supply economics in play there. Samsung uses Exynos chips in their flagship phones in the Asian market and sometimes select parts of the European market, but typically they buy from Qualcomm for the NA market and majority of Europe due to marketing, existing penetration, etc. It also helps that Samsung currently is a fabricator of the newest Snapdragon SoCs in both Korea and the U.S. and that affords them prime pricing.They would be slapping the right hand with the left by getting too deep into the R&D and fighting for market share with Exynos. It would be taking revenue from their foundry business to try to grow their design business, and margins in mobile logic are pretty slim these days.

Howard72 - Monday, May 30, 2016 - link

Mali G71 parallel architecture is now consider as RISC SIMD?Howard72 - Monday, May 30, 2016 - link

*considerdOEMG - Monday, May 30, 2016 - link

I hope they also push this to the low-end, at least for the sake of API parity (Vulkan! Vulkan! Vulkan!) among a wide range of devices.LeptonX - Monday, May 30, 2016 - link

"In just six years, the number of GPU vendors with a major presence in high-end Android phones has been whittled down to only two: the vertically integrated Qualcomm, and the IP-licensing ARM."What about PowerVR? Why did you omit them? Aren't they still a major player with GPUs that are at the top both in terms of overall performance and energy-efficiency?

Ariknowsbest - Monday, May 30, 2016 - link

I would consider PowerVR as a major player, after several generations i find them to be very balanced and powerful.But they have lost marketshare to ARM.

So far only bought products with PowerVR and Adreno and a couple Tegras.

Colin1497 - Monday, May 30, 2016 - link

I think the "android" statement is the qualifier. PowerVR is obviously big with Apple as a customer. In the non-Apple space I guess they're more limited? MediaTek uses them?