The Intel Optane Memory (SSD) Preview: 32GB of Kaby Lake Caching

by Billy Tallis on April 24, 2017 12:00 PM EST- Posted in

- SSDs

- Storage

- Intel

- PCIe SSD

- SSD Caching

- M.2

- NVMe

- 3D XPoint

- Optane

- Optane Memory

Mixed Read/Write Performance

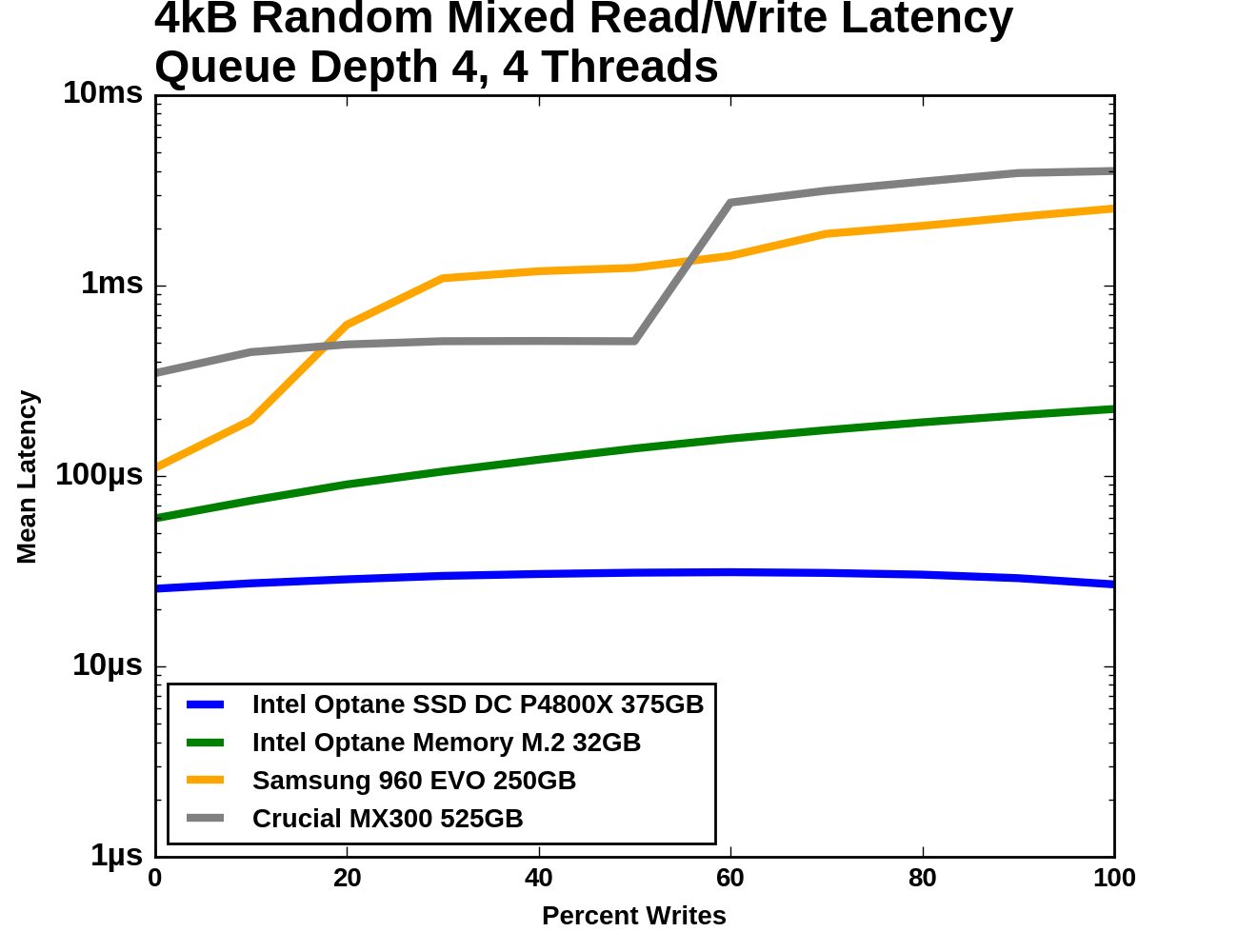

Workloads consisting of a mix of reads and writes can be particularly challenging for flash based SSDs. When a write operation interrupts a string of reads, it will block access to at least one flash chip for a period of time that is substantially longer than a read operation takes. This hurts the latency of any read operations that were waiting on that chip, and with enough write operations throughput can be severely impacted. If the write command triggers an erase operation on one or more flash chips, the traffic jam is many times worse.

The occasional read interrupting a string of write commands doesn't necessarily cause much of a backlog, because writes are usually buffered by the controller anyways. But depending on how much unwritten data the controller is willing to buffer and for how long, a burst of reads could force the drive to begin flushing outstanding writes before they've all been coalesced into optimal sized writes.

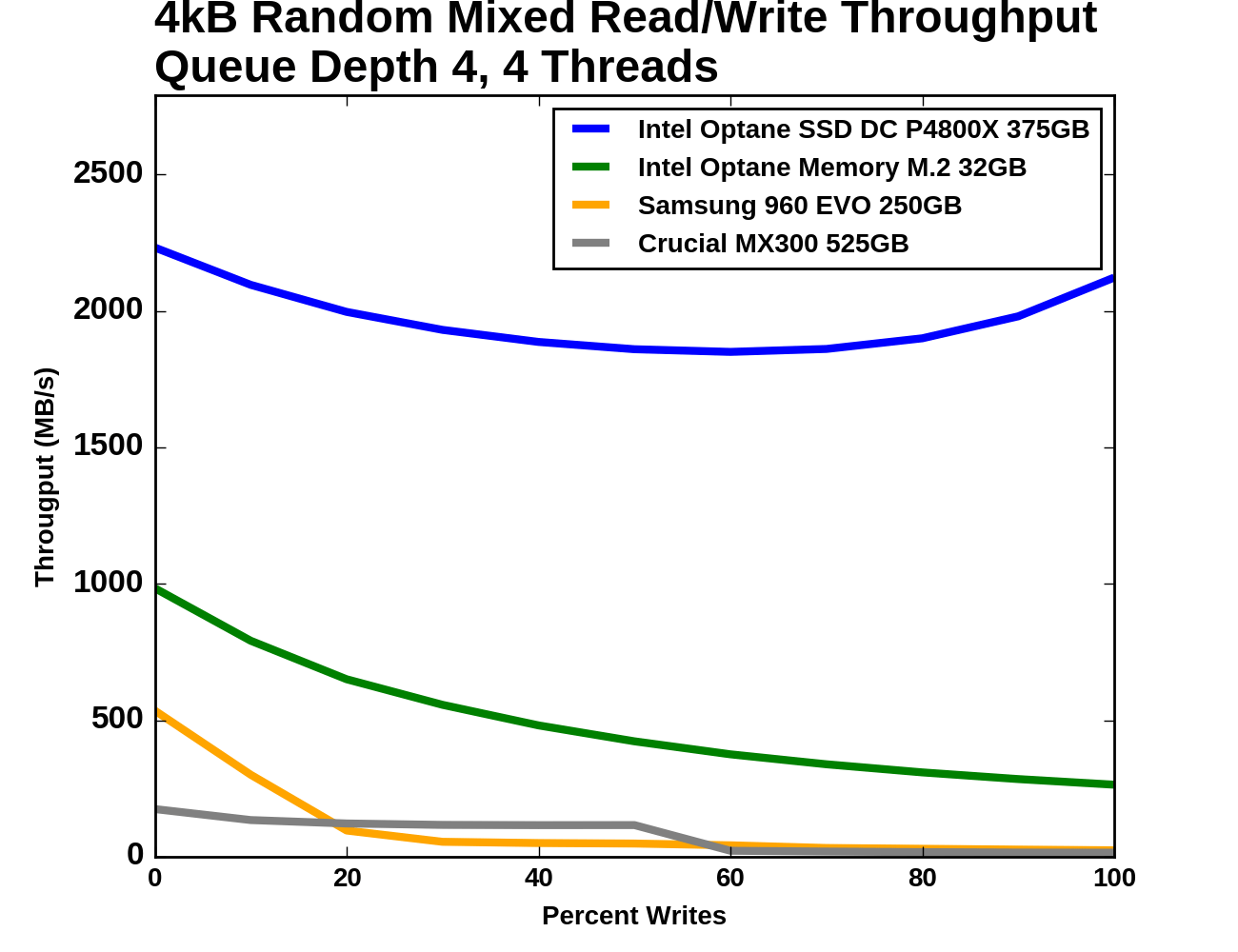

This mixed workload test is an extension of what Intel describes in their specifications for the Optane SSD DC P4800X. A total queue depth of 16 is achieved using four worker threads, each performing a mix of random reads and random writes. Instead of just testing a 70% read mixture, the full range from pure reads to pure writes is tested at 10% increments. These tests were conducted on the Optane Memory as a standalone SSD, not in any caching configuration. Client and consumer workloads do consist of a mix of reads and writes, but never at queue depths this high; this test is included primarily for comparison between the two Optane devices.

|

|||||||||

| Vertical Axis units: | IOPS | MB/s | |||||||

At the beginning of the test where the workload is purely random reads, the four drives almost form a geometric progression: the Optane Memory is a little under half as fast as the P4800X and a little under twice as fast as the Samsung 960 EVO, and the MX300 is about a third as fast as the 960 EVO. As the proportion of writes increases, the flash SSDs lose throughput quickly. The Optane Memory declines across the entire test but gradually, ending up at a random write speed around one fourth of its random read speed. The P4800X has enough random write throughput to rebound during the final phases of the test, ending up with a random write throughput almost as high as the random read throughput.

|

|||||||||

| Mean | Median | 99th Percentile | 99.999th Percentile | ||||||

The flash SSDs actually manage to deliver better median latency than the Optane Memory through a portion of the test, after they've shed most of their throughput. For the 99th and 99.999th percentile latencies, the flash SSDs perform much worse once writes are added to the mix, ending up almost 100 times slower than the Optane Memory.

Idle Power Consumption

There are two main ways that a NVMe SSD can save power when idle. The first is through suspending the PCIe link through the Active State Power Management (ASPM) mechanism, analogous to the SATA Link Power Management mechanism. Both define two power saving modes: an intermediate power saving mode with strict wake-up latency requirements (eg. 10µs for SATA "Partial" state) and a deeper state with looser wake-up requirements (eg. 10ms for SATA "Slumber" state). SATA Link Power Management is supported by almost all SSDs and host systems, though it is commonly off by default for desktops. PCIe ASPM support on the other hand is a minefield and it is common to encounter devices that do not implement it or implement it incorrectly, especially among desktops. Forcing PCIe ASPM on for a system that defaults to disabling it may lead to the system locking up.

The NVMe standard also defines a drive power management mechanism that is separate from PCIe link power management. The SSD can define up to 32 different power states and inform the host of the time taken to enter and exit these states. Some of these power states can be operational states where the drive continues to perform I/O with a restricted power budget, while others are non-operational idle states. The host system can either directly set these power states, or it can declare rules for which power states the drive may autonomously transition to after being idle for different lengths of time. NVMe power management including Autonomous Power State Transition (APST) fortunately does not depend on motherboard support the way PCIe ASPM does, so it should eventually reach the same widespread availability that SATA Link Power Management enjoys.

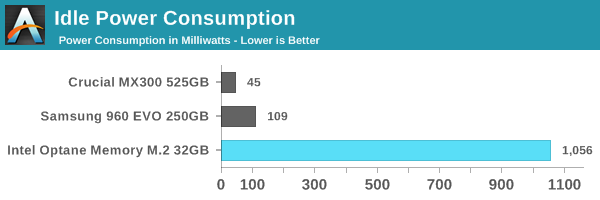

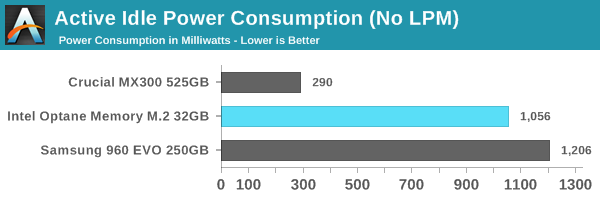

We report two idle power values for each drive: an active idle measurement taken with none of the above power management states engaged, and an idle power measurement with either SATA LPM Slumber state or the lowest-power NVMe non-operational power state, if supported. These tests were conducted on the Optane Memory as a standalone SSD, not in any caching configuration.

With no support for NVMe idle power states, the Optane Memory draws the rated 1W at idle while the SATA and flash-based NVMe drives drop to low power states with a tenth of the power draw or less. Even without using low power states, the Crucial MX300 uses a fraction of the power, and the Samsung 960 EVO uses only 150mW more to keep twice as many PCIe lanes connected.

The Optane Memory is a tough sell for anyone concerned with power consumption. In a typical desktop it won't be enough to worry about, but Intel definitely needs to add proper power management to the next iteration of this product.

110 Comments

View All Comments

ddriver - Wednesday, April 26, 2017 - link

It is only natural to have negative sentiments about greedy, lousy corporations because of what they do. It is nothing personal though, I do it because I am a conscious human being. Not cattle. You can throw crapple and moogle into the mix. There is no single good reason to be fond of any corporation. The bigger they are the more damage they do to humanity and the planet as a whole.In other news, water is wet!

eddman - Wednesday, April 26, 2017 - link

You are not fooling anyone.eddman - Wednesday, April 26, 2017 - link

...and you are so blind by your hatred that you dismiss every single thing that these companies do. You are not rational in the slightest but do like to boast about how great you are.Reflex - Tuesday, April 25, 2017 - link

Nailed it eddman. Because it does not personally solve ddriver's problems, or because it comes from the wrong brand, its an epic disaster. The funny thing here is I agree this is not a revolution, at least not yet, but the incessant bashing and inability to acknowledge that it has its uses and those use cases are likely to only grow demonstrates the bias involved.Reflex - Tuesday, April 25, 2017 - link

To the insinuation that Optane may somehow be relabeled SLC NAND, I went and did a little research/consultation. All NAND requires writing to blocks, Optane can support bit level writes (expected in DIMM configurations), which is a major advantage over NAND and not technically possible with NAND. It was also pointed out that if Optane was simply disguised SLC, despite the technical impossibility, it would mean that Intel had engaged in financial fraud by materially misrepresenting its technology, capabilities and long-term expectations to investors.Thanks to Joel Hruska for looking into it for me.

More info here: https://arstechnica.com/gadgets/2017/04/intel-opta...

More from Joel here: https://www.extremetech.com/author/jhruska

Reflex - Monday, April 24, 2017 - link

OMG it's the fastest product on the market in its class but because I choose to interpret the early marketing as applying to the first gen product it totally sucks! I refuse to benefit from drastically better performance because Intel *dared* to speak to its potential performance and didn't deliver that in the first product!In fact, I am so enraged I'm ripping out all my existing SSD's and replacing them with Quantum Bigfoot drives in protest.

Drumsticks - Monday, April 24, 2017 - link

It's probably because Intel dared to do something innovative again, and we can't possibly give credit where it's due, can we? If it was Samsung, I bet it would just be Samsung being Samsung. Slap the blue name on top, and it's cool to criticize whatever you can, even in the face of hard numbers. Make sure you also include an edgy name like "Hypetane" to really drive your point home.Reflex - Monday, April 24, 2017 - link

To be fair if it were Samsung we'd get a lecture on the oppression of North Korea mixed in there somewhere along with a conspiracy theory about the south being a puppet state not permitted to succeed in the face of America.jabbadap - Monday, April 24, 2017 - link

Well I don't want to degrade intel's efforts on this. But it's intel/micron co-operation who have engineered this and I would even guess a bit further that science behind this is more micron tech than intels.Drumsticks - Monday, April 24, 2017 - link

That's fair, and Micron definitely deserves credit as well. I'm sure they'll get their own when QuantX comes out, hopefully sometime this year. I suspect that the R&D was split very evenly, though; Intel has always been good at doing things "well" in the fab; Micron had excelled at doing them "cheaply" which is one reason the venture was reasonably successful. Plus, I feel it would be hard to collaborate on R&D together for 10 years and successfully say "we did this together" to the public, if one side (Micron or Intel) did most of the work. I guess we'll never know, though.