Hot Chips 2021 Keynote Live Blog: Designing Chips with AI, Synopsys

by Dr. Ian Cutress on August 23, 2021 3:20 PM EST

03:26PM EDT - a few minute until the Synopsys keynote starts

03:28PM EDT - Today's Keynote Speaker is CEO Aart de Geus about Machine Learning in EDA tools

03:28PM EDT - Here's a preview

03:28PM EDT - https://www.anandtech.com/show/16784/using-ai-to-build-processors-google-was-just-the-start-says-synopsys

03:32PM EDT - 'If you know chips, you know Synopsys'

03:33PM EDT - At the center of every advance in EDA since

03:33PM EDT - Undergrad in Switzerland

03:34PM EDT - Being able to see the world in different perspectives

03:34PM EDT - Hot Chips is where you find the best architects

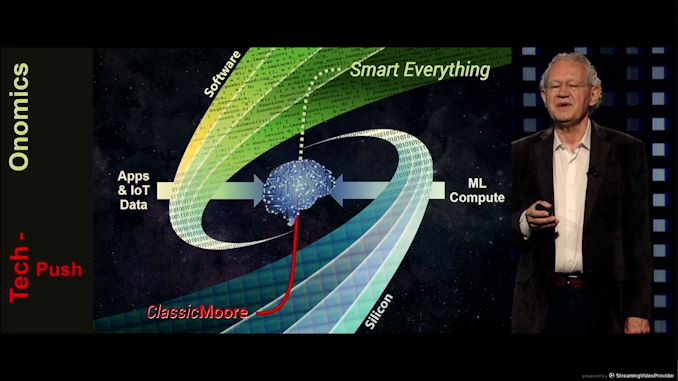

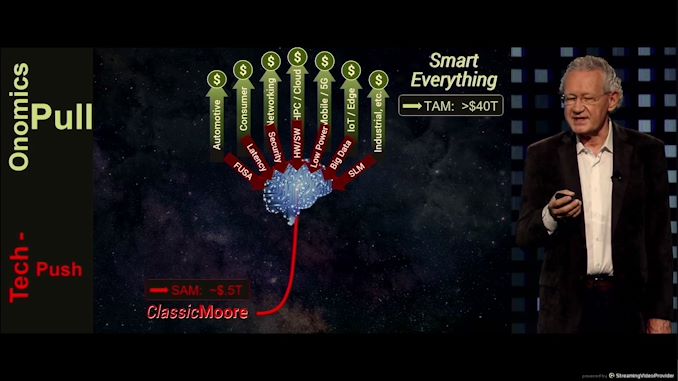

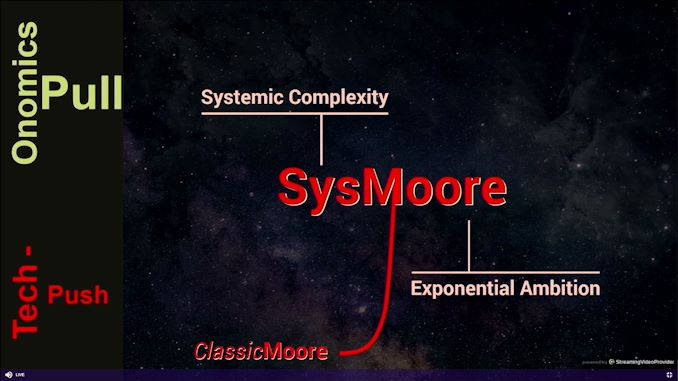

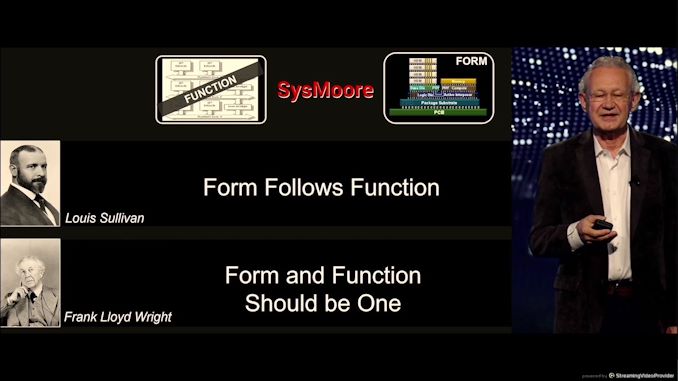

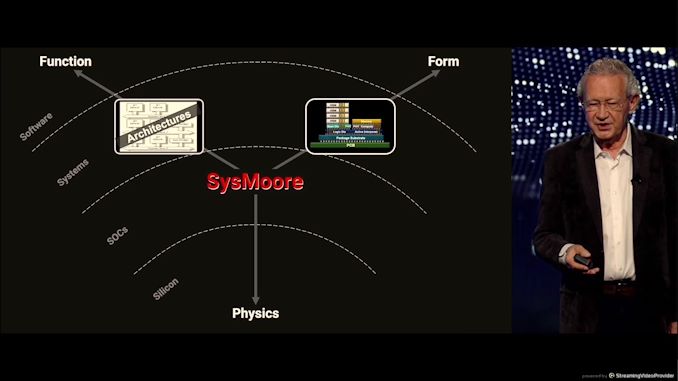

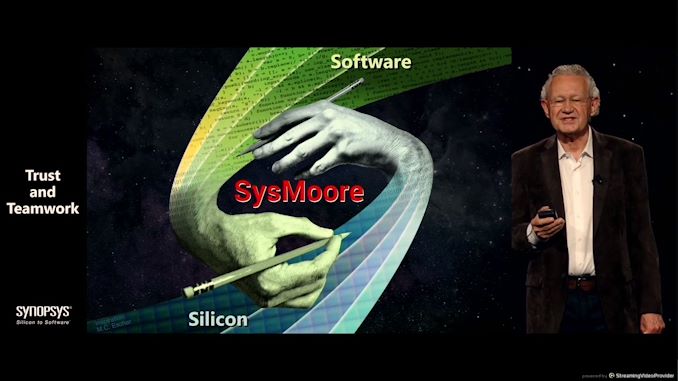

03:35PM EDT - New SysMoore Era

03:35PM EDT - The mission for the next 20 years - architecting intellegence

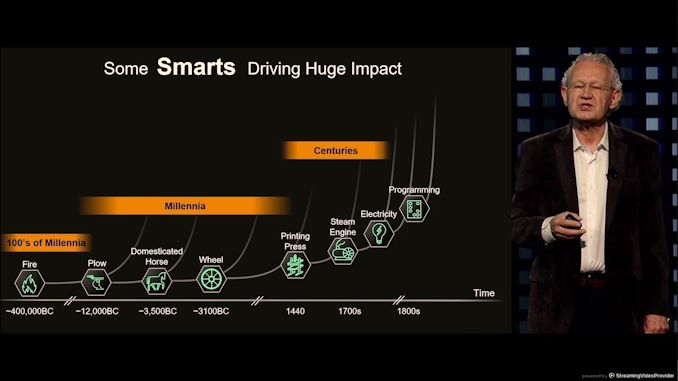

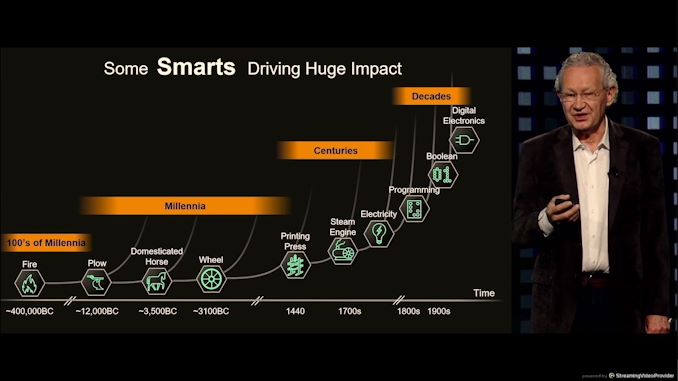

03:35PM EDT - Architecting of smarts

03:35PM EDT - Smart drive impactg

03:36PM EDT - Smart Everything

03:36PM EDT - Ideas and engineering -duct tape and WD40

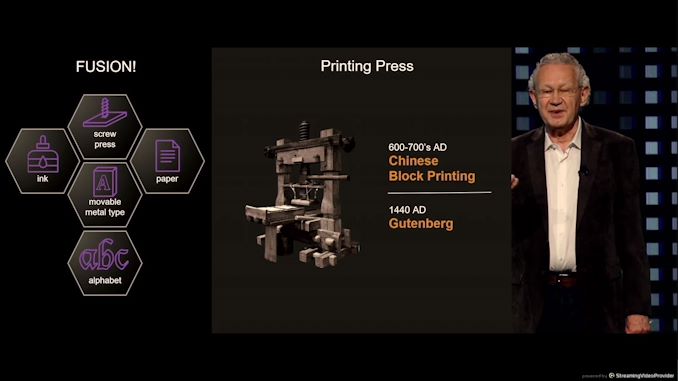

03:37PM EDT - Impact of printing press - 20m books after printed press was 'redescovered'

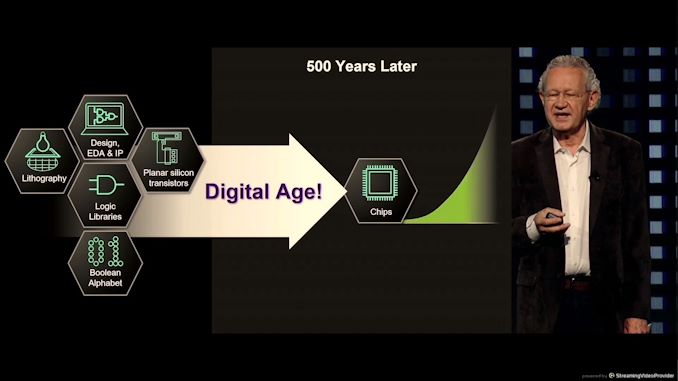

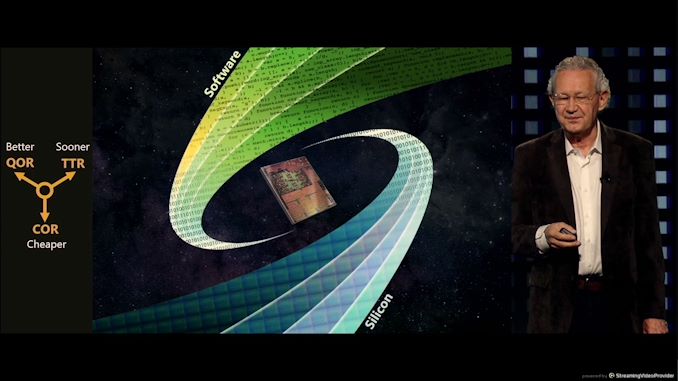

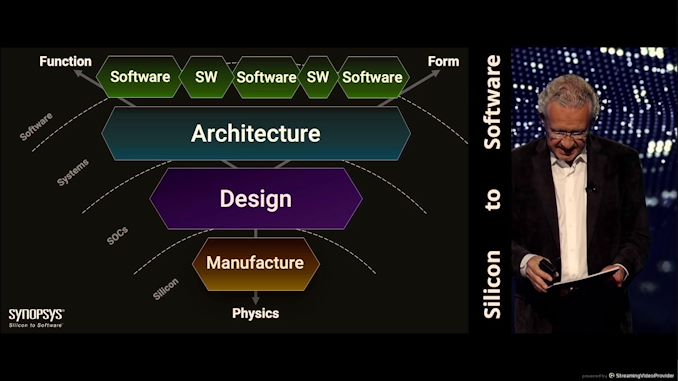

03:38PM EDT - Software and Silicon

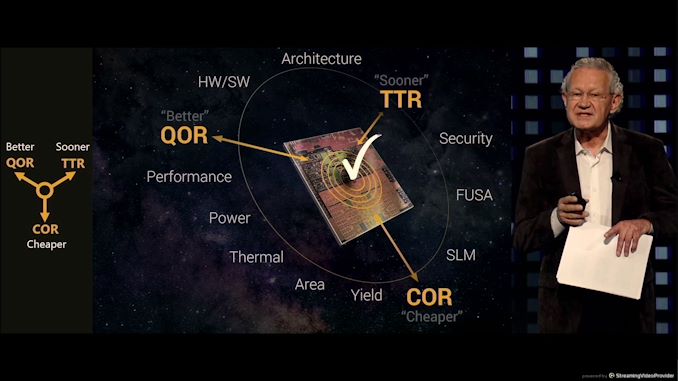

03:39PM EDT - Add in Thermal effects

03:39PM EDT - Solving systemic issues, security, silicon life cycle, functionality

03:39PM EDT - balancing all the requirements

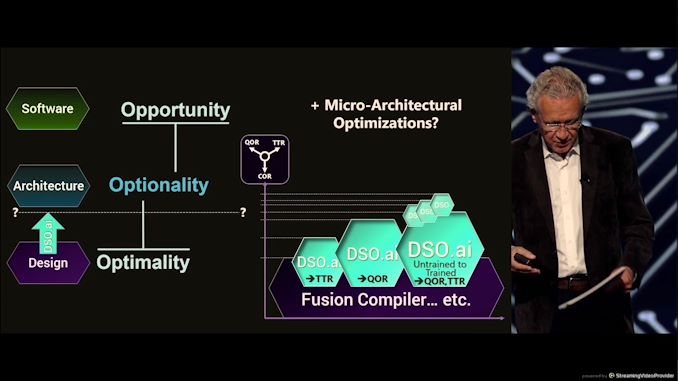

03:39PM EDT - Applying the vision with optionality in the middle

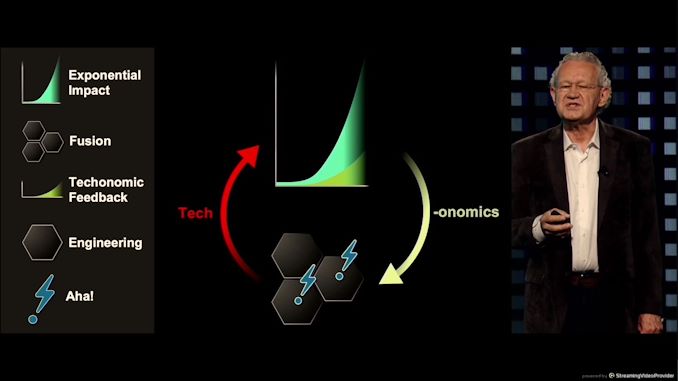

03:39PM EDT - Techonomics

03:40PM EDT - ML algorithms need to be computing in time

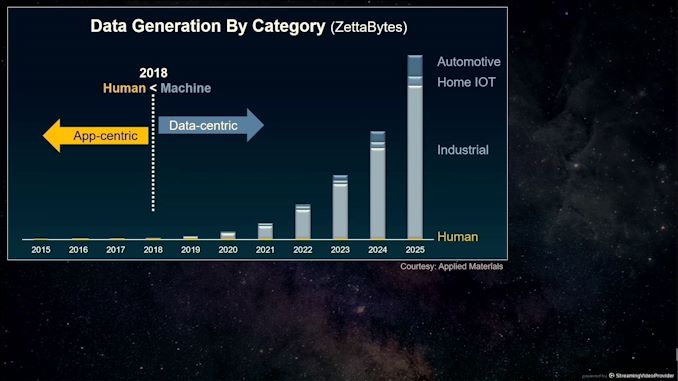

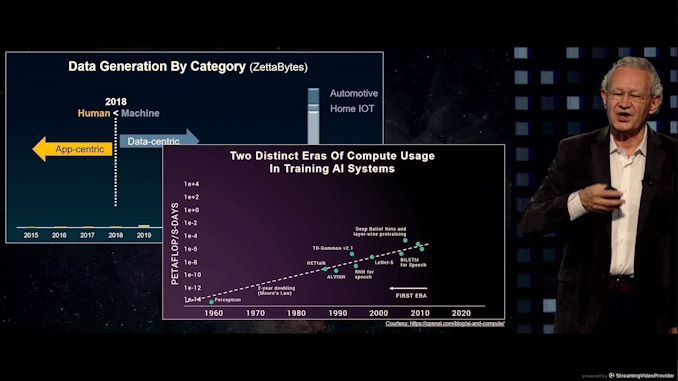

03:40PM EDT - Growth in the amount of data

03:40PM EDT - 'Can we do that AI thing'

03:41PM EDT - Data generated by humans is minmal

03:41PM EDT - compared what's generated by machines

03:42PM EDT - Using AI to be more effective with system requests and requirements

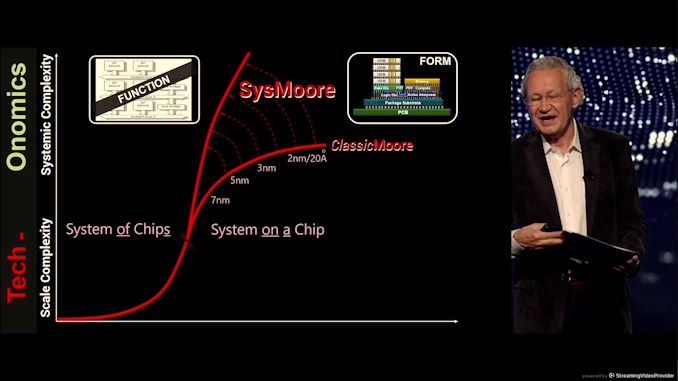

03:42PM EDT - Systemic Complexity vs Exponential Ambition = Sysmoore

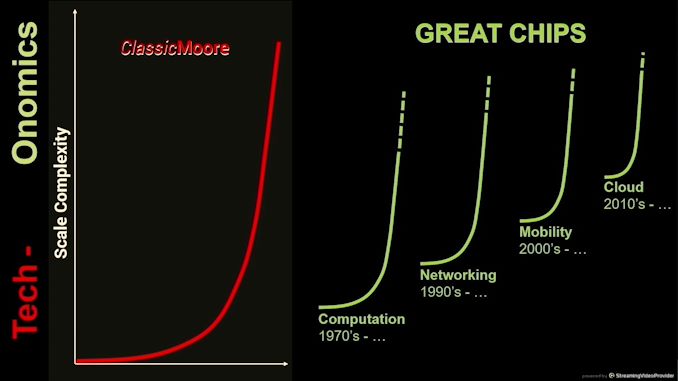

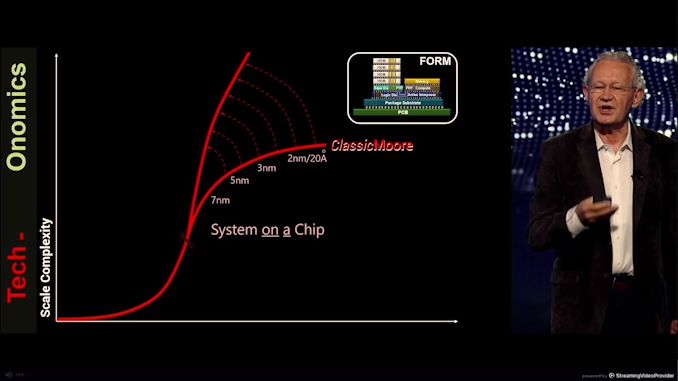

03:43PM EDT - Systemic complexity vs scale complexity - we've solved scale complexity

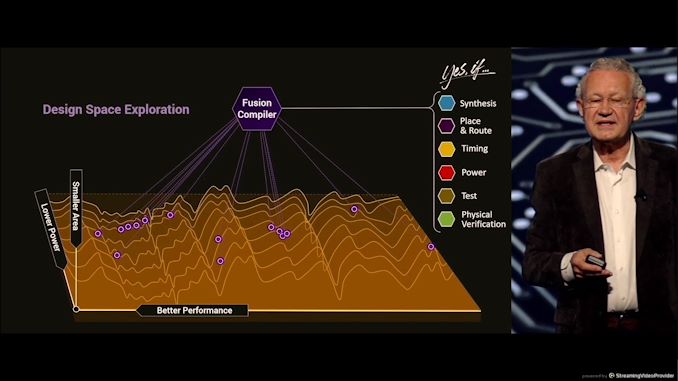

03:44PM EDT - replacing no because with yes if

03:44PM EDT - Moore's Law doesn't always mean smaller devices

03:45PM EDT - Angrsrom has the word Angst in it!

03:45PM EDT - A booster pack to Moore's Law

03:45PM EDT - System of Chips

03:45PM EDT - AI is driving a rethink in architectures

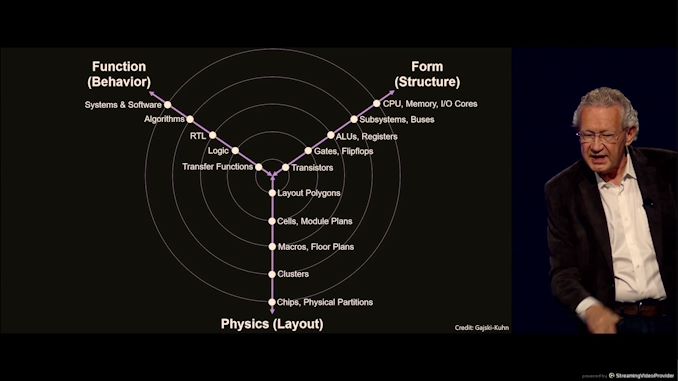

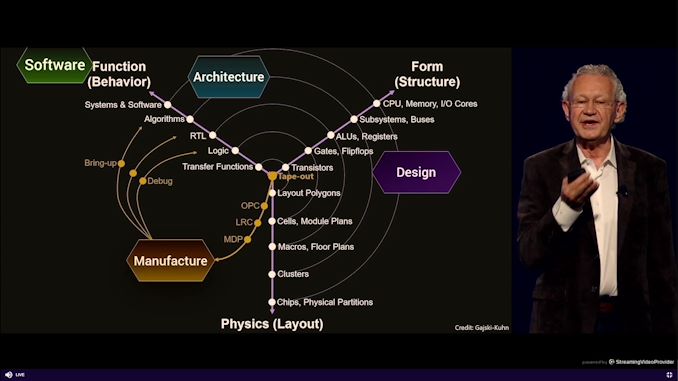

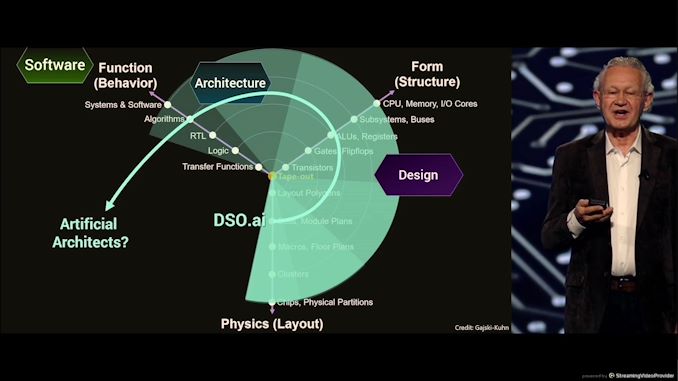

03:45PM EDT - Function and form

03:46PM EDT - Form must follow function

03:48PM EDT - Sorry the animations here keep overwriting each other

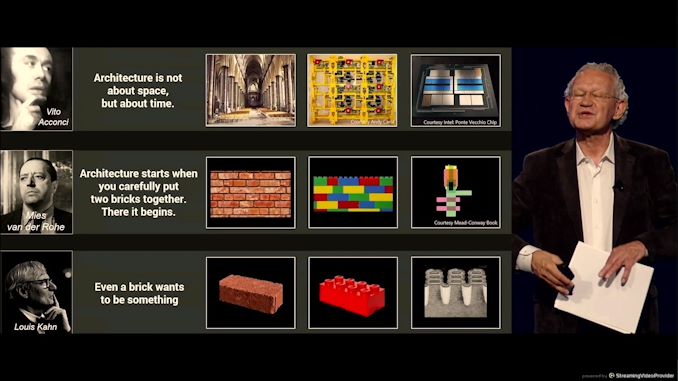

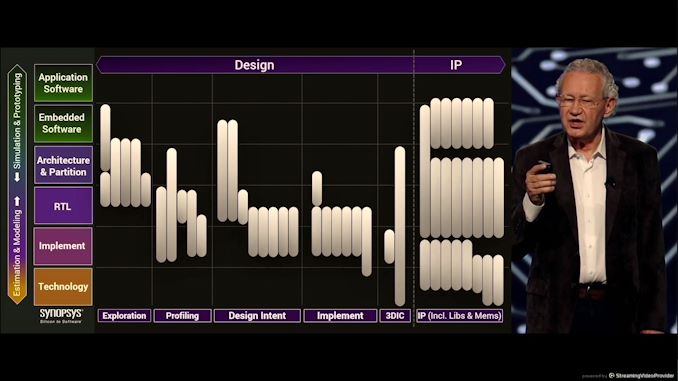

03:48PM EDT - Talking about architecture and development

03:49PM EDT - blocks vs construction vs time - all about the next level of abstraction

03:49PM EDT - Levels of abstraction

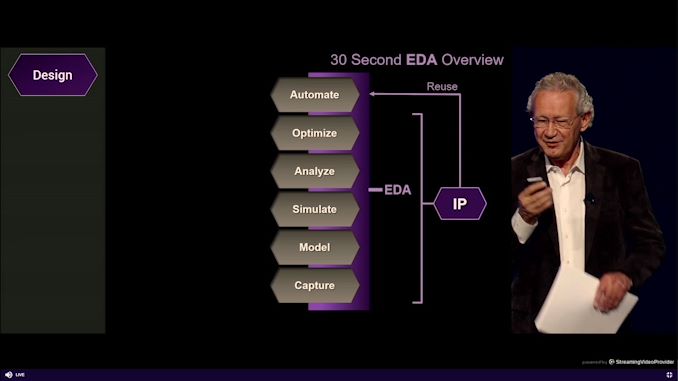

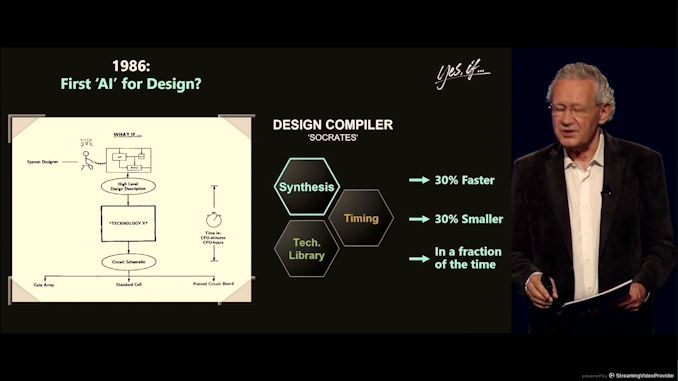

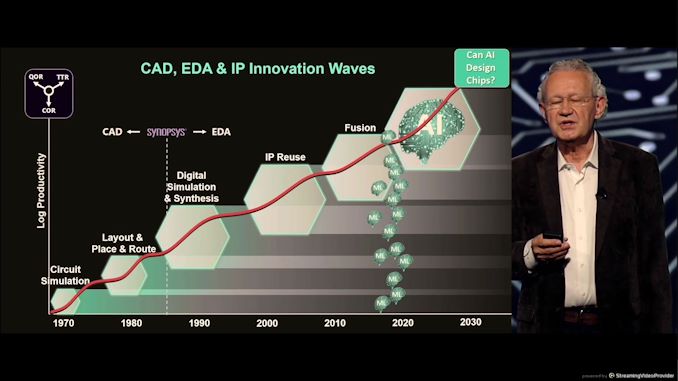

03:51PM EDT - Now time for EDA

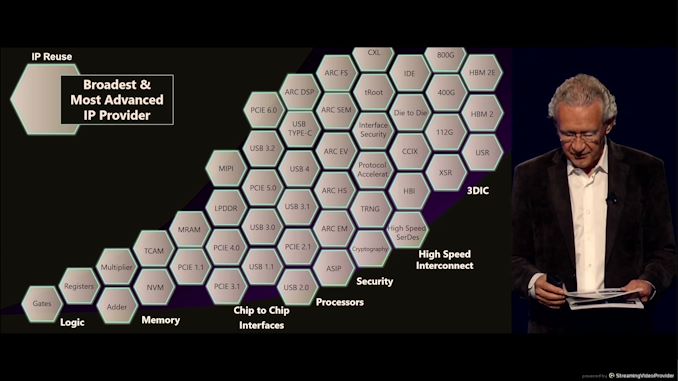

03:51PM EDT - IP reuse

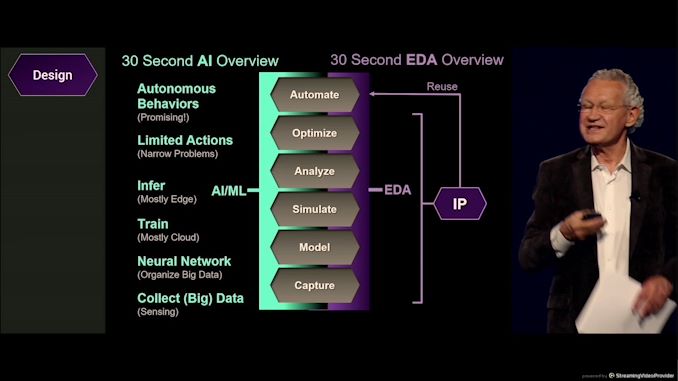

03:51PM EDT - Integrating ML into EDA

03:52PM EDT - Now for circuit simulation

03:54PM EDT - Developing AI for EDA

03:54PM EDT - Using AI to do more

03:54PM EDT - AI enables better automation - EDA already has lots of automation

03:54PM EDT - Arm enabled IP reuse

03:55PM EDT - looking hardware at latency and capacity of communication

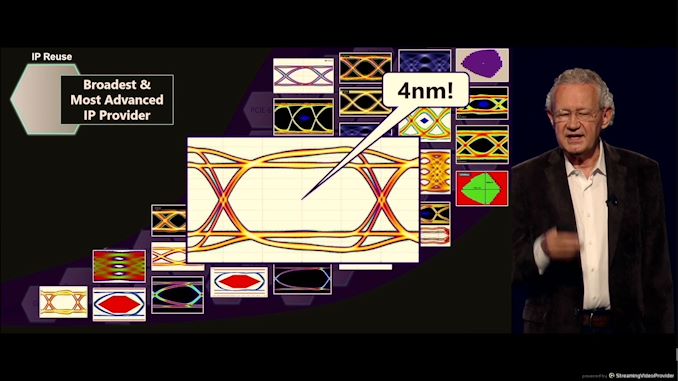

03:55PM EDT - 4nm in production today

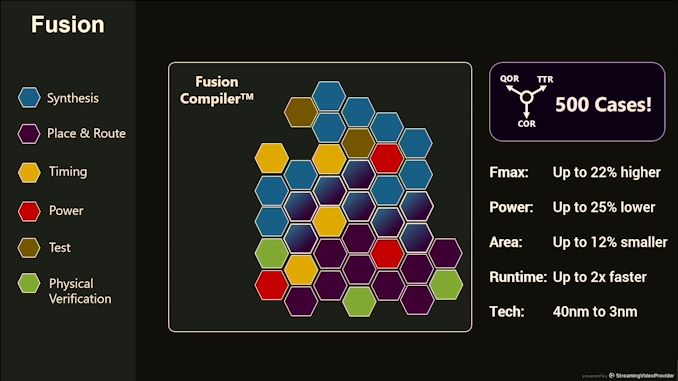

03:56PM EDT - Fusion compiler - 500 cases

03:56PM EDT - Everyone of Synopsys tools has some form of machine learning

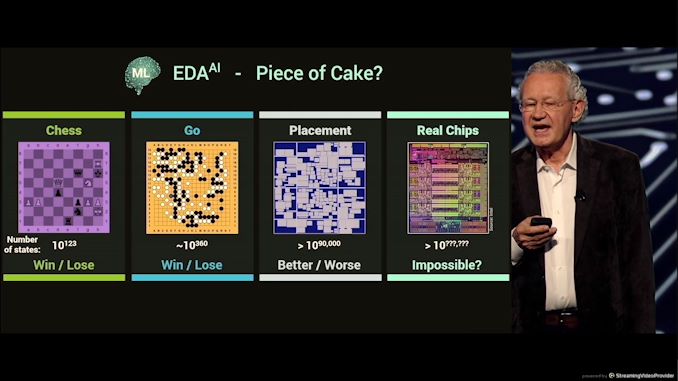

03:57PM EDT - Can you enable ML on design flow

03:57PM EDT - Using you enable autonomous design? YES

03:58PM EDT - But it gets harder with AI

03:58PM EDT - Moving form win/lose to better/worse

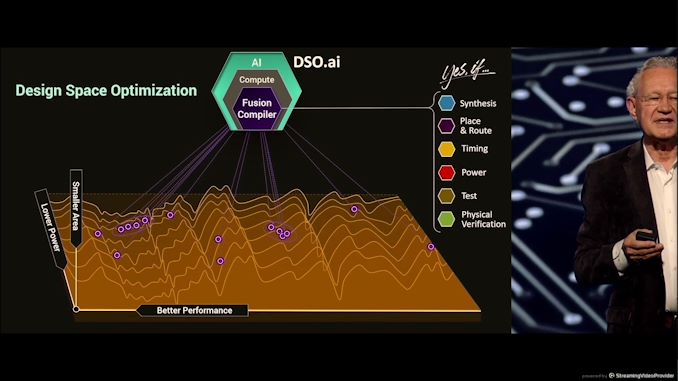

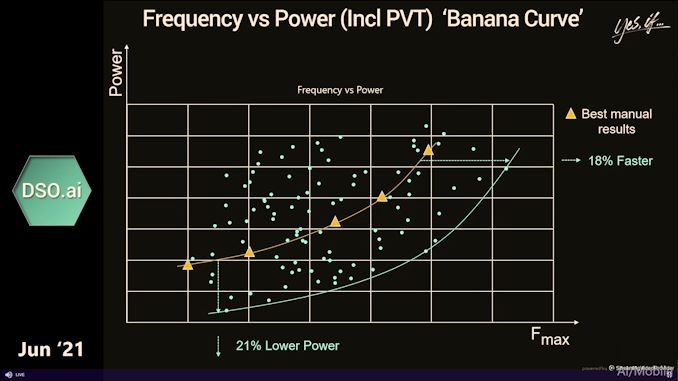

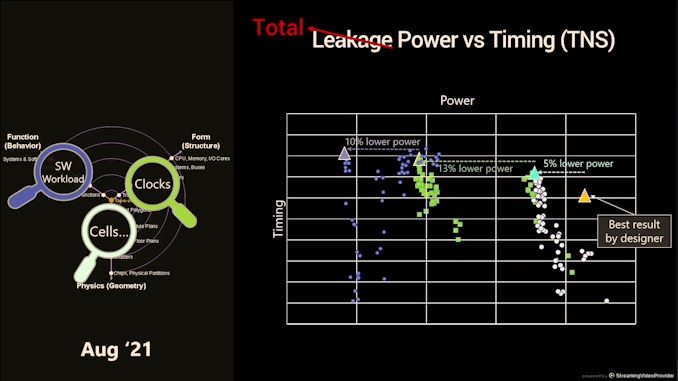

04:00PM EDT - Design Space Optimization, not just exploration

04:00PM EDT - using everything they've learned in the past

04:00PM EDT - results from real designs

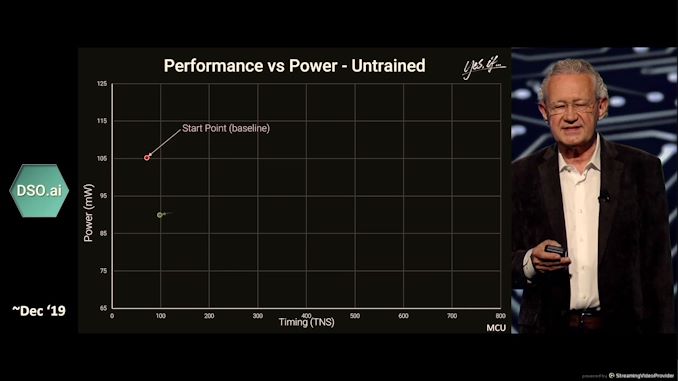

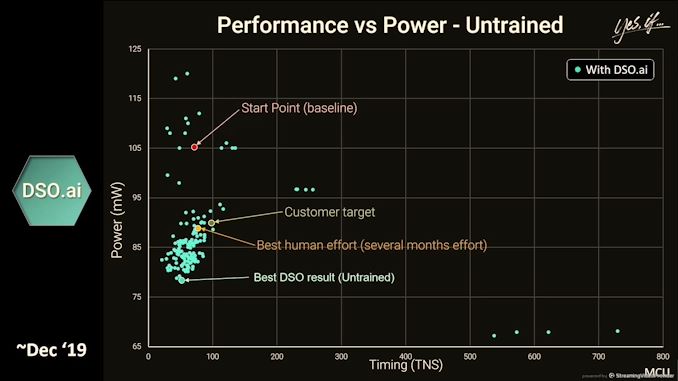

04:00PM EDT - This is in december 19

04:01PM EDT - Best result is well above any human design

04:01PM EDT - Tested 10-100x more than a human design team

04:02PM EDT - This is untrained

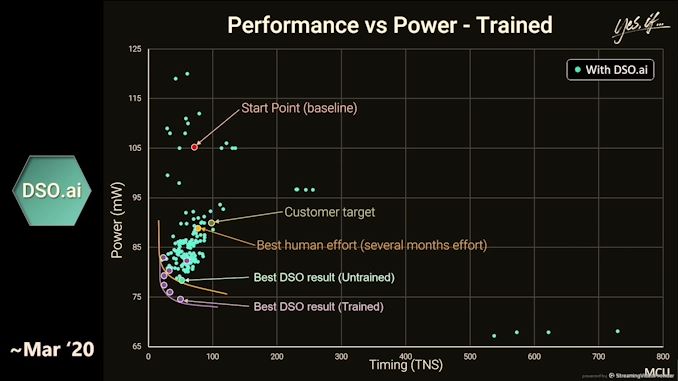

04:02PM EDT - Using a trained version

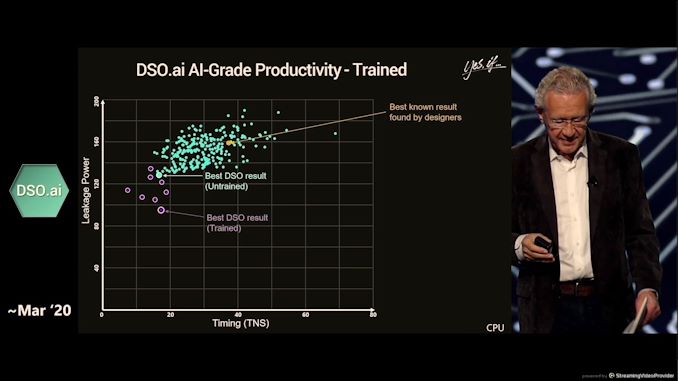

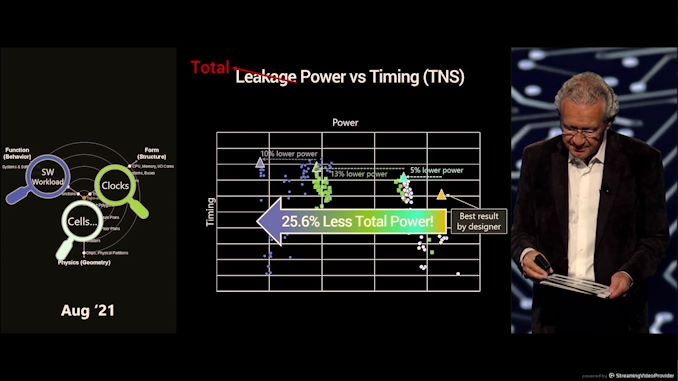

04:03PM EDT - Here's another example of a customer result

04:04PM EDT - Single engineer vs a team

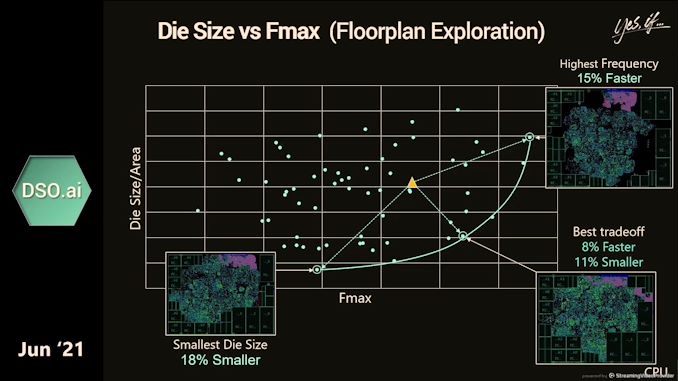

04:04PM EDT - A third example

04:05PM EDT - Learning from final results

04:07PM EDT - Free t-shirt on the QR code

04:07PM EDT - with the diagram in

04:07PM EDT - Using DSO.ai at the microarchitecture level

04:08PM EDT - Can you get AI to make microarch adjustments?

04:08PM EDT - Architecture searches

04:08PM EDT - with cells

04:09PM EDT - Using AI to optimize for a software workload

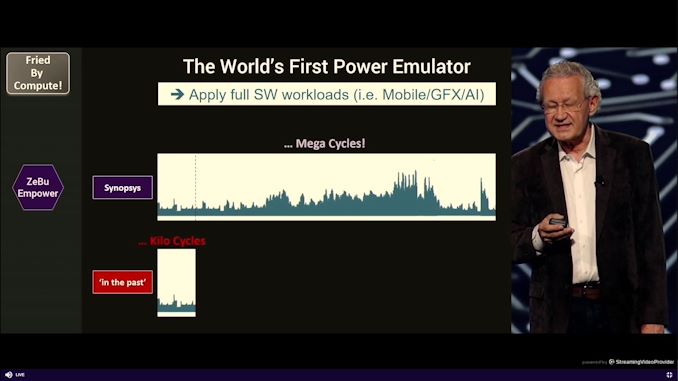

04:10PM EDT - Software design might blow out a physical design e.g. dynamic power peaks

04:11PM EDT - SW power emulators

04:11PM EDT - Simulate millions of cycles of software on a design

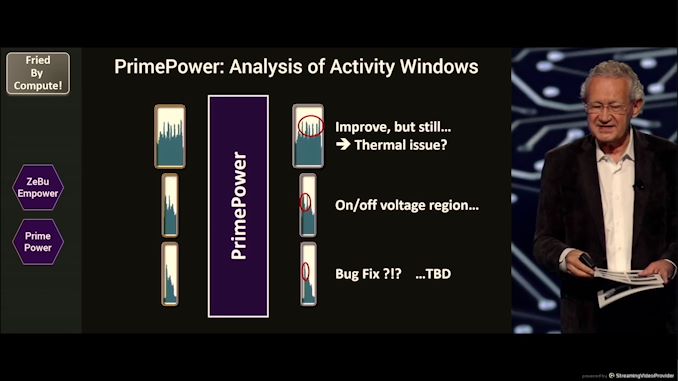

04:12PM EDT - Analyze software power hotspots

04:12PM EDT - Using AI to optimize for thermal issues, switching, or errata

04:13PM EDT - Everything in the chain matters

04:14PM EDT - 25% better power by simulating software workload

04:14PM EDT - optimization in design by analyzing software

04:16PM EDT - Now going back to buildings

04:17PM EDT - Beauty in chip design

04:18PM EDT - Understanding what to right to do something

04:18PM EDT - all about trust and teamwork

04:19PM EDT - Using EDA to develop chips to run better EDA tools to design better chips

04:19PM EDT - One of the greatest chips Aart has ever seen

04:20PM EDT - Great engineers are great artists

04:20PM EDT - 'Be catalysts of the impossible'

04:21PM EDT - Q&A Time

04:24PM EDT - Q: Can ML help with Spec compliance with IP blocks? A: Yes, depends on the model. Coverage is a function of how many errors you can detect. knowing your test structures, learn from patterns to how to stimulate your devices. Intersection of verification and optimization

04:24PM EDT - Q: How long does DSO take to converge / resources are needed in the examples? A: It's a function of the size of the complexity. 20 cores ran from days to a week

04:25PM EDT - Q: What does DSO need through input? A: RTL, areas of focus, every variable you need

04:27PM EDT - Q: Will constaints become suggestions? A: Yes in that direction - you will learn where to trust where making something less fixed will end with a better result.

04:28PM EDT - Q: What ML tools did Synopsys use. A: Secret sauce!

04:30PM EDT - Q: Do we need new description languages aside from RTL? A: Yes, but you're the pro! Whenever you can optimize the lower steps, it moves you up the stack is architect - in you can enrich the language on the optionality, this is how you will never be happy but you will make it better

04:32PM EDT - That's a wrap

0 Comments

View All Comments