GIGABYTE Z97X-UD5H Review: Choose Your Storage Option

by Ian Cutress on May 14, 2014 9:00 AM EST- Posted in

- Motherboards

- Intel

- Gigabyte

- Z97

System Benchmarks

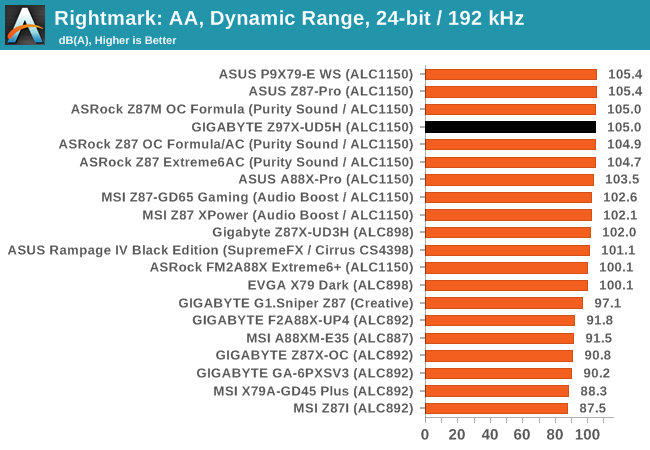

Rightmark Audio Analyzer 6.2.5

The premise behind Rightmark:AA is to test the input and output of the audio system to determine noise levels, range, harmonic distortion, stereo crosstalk and so forth. Rightmark:AA should indicate how well the sound system is built and isolated from electrical interference (either internally or externally). For this test we connect the Line Out to the Line In using a short six inch 3.5mm to 3.5mm high-quality jack, turn the OS speaker volume to 100%, and run the Rightmark default test suite at 192 kHz, 24-bit. The OS is tuned to 192 kHz/24-bit input and output, and the Line-In volume is adjusted until we have the best RMAA value in the mini-pretest. We look specifically at the Dynamic Range of the audio codec used on board, as well as the Total Harmonic Distortion + Noise.

Dynamic Range of the Z97X-UD5H

While the dynamic range of the UD5H was good, the THD+N was low - this is indicative of a driver issue we encountered. Not unique to the UD5H, but the disk drivers we were provided causes a lot of distortion at 100% speaker volume. On other motherboards with the same codec, an audio driver update fixed the issue, and we assume it will be similar for the UD5H.

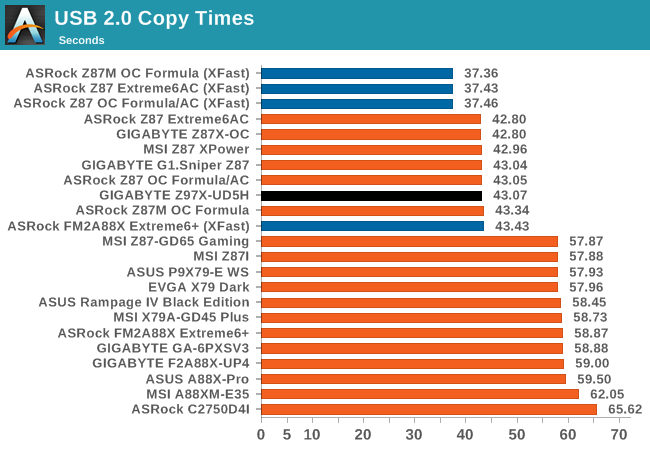

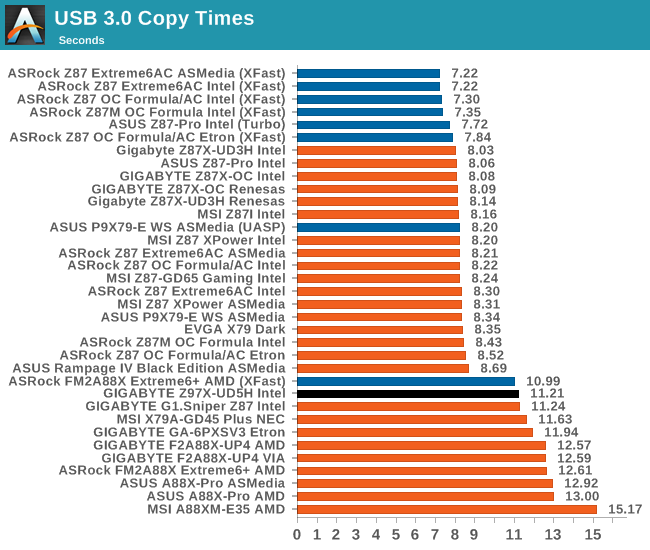

USB Backup

For this benchmark, we run CrystalDiskMark to determine the ideal sequential read and write speeds for the USB port using our 240 GB OCZ Vertex3 SSD with a SATA 6 Gbps to USB 3.0 converter. Then we transfer a set size of files from the SSD to the USB drive using DiskBench, which monitors the time taken to transfer. The files transferred are a 1.52 GB set of 2867 files across 320 folders – 95% of these files are small typical website files, and the rest (90% of the size) are the videos used in the WinRAR test. In an update to pre-Z87 testing, we also run MaxCPU to load up one of the threads during the test which improves general performance up to 15% by causing all the internal pathways to run at full speed.

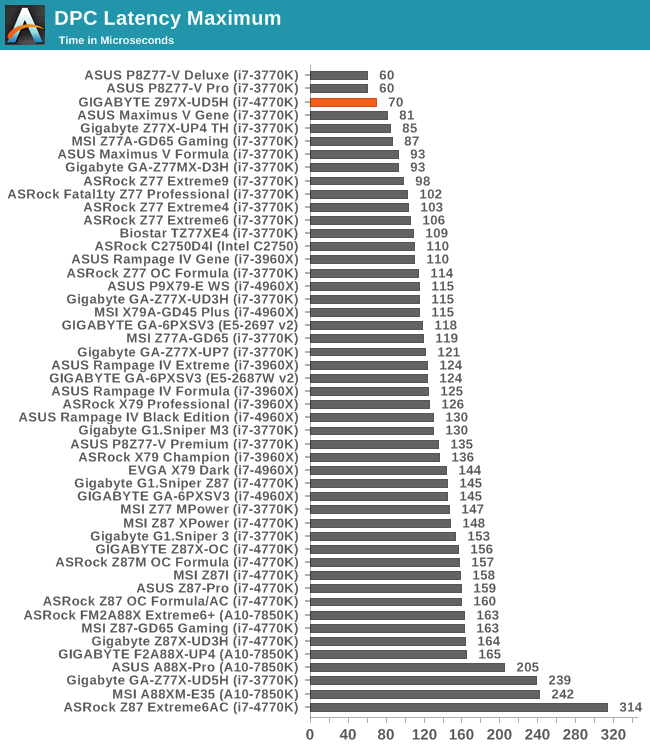

DPC Latency

Deferred Procedure Call latency is a way in which Windows handles interrupt servicing. In order to wait for a processor to acknowledge the request, the system will queue all interrupt requests by priority. Critical interrupts will be handled as soon as possible, whereas lesser priority requests, such as audio, will be further down the line. So if the audio device requires data, it will have to wait until the request is processed before the buffer is filled. If the device drivers of higher priority components in a system are poorly implemented, this can cause delays in request scheduling and process time, resulting in an empty audio buffer – this leads to characteristic audible pauses, pops and clicks. Having a bigger buffer and correctly implemented system drivers obviously helps in this regard. The DPC latency checker measures how much time is processing DPCs from driver invocation – the lower the value will result in better audio transfer at smaller buffer sizes. Results are measured in microseconds and taken as the peak latency while cycling through a series of short HD videos - less than 500 microseconds usually gets the green light, but the lower the better.

Hurrah, it looks like the DPC Latency issues around Z87 are gone! With Z87, every motherboard we tested was >140 microseconds on DPC Latency, but it looks like Z97 is going straight to the top of our testing. Other motherboards we are currently testing show similar results at the top end of our results.

53 Comments

View All Comments

The_Assimilator - Thursday, May 15, 2014 - link

A: By that argument every chipset ever made should still support ISA.B: The Flex IO diagram on this very page specifically states "Total of 14 USB2 ports". I'm reading that as being a constant entirely independent of the number of USB 3.0 ports, but if you have any literature to contradict that, I'd be appreciative if you could link it.

repoman27 - Thursday, May 15, 2014 - link

Not sure I follow your logic. USB is probably the most used feature of a modern chipset (I suppose SATA probably gives it a run for its money though). Take a look at any USB 3.0 connector and you'll find 5 contacts which correspond to the SuperSpeed transmit and receive signaling pairs and ground, and then 4 more that carry the USB 2.0 signal and Vbus. This is how USB 3.0 achieves SuperSpeed while maintaining backwards compatibility, and the signals all need to come from somewhere.Intel hasn't posted datasheets for the 9 series chipsets yet, but there really isn't a heck of a lot of difference between them and the 8 series (in fact they're all currently listed in ARK under the "Products (Formerly Lynx Point)" heading). In the 8 series datasheet [ http://www.intel.com/content/dam/www/public/us/en/... ], however, Intel states: "xHCI USB controller provides support for up to 14 USB ports, of which six can be configured as SuperSpeed USB 3.0 ports." Intel also includes this additional note: "Some USB 3.0 motherboard down devices do not require support for USB 2.0 speed and it is possible to route only the SuperSpeed signals, as allowed by the USB 3.0 specification. In this special case, USB 2.0 and USB 3.0 signals will not need to be paired together, thereby allowing support for more than 14 USB connections."

Interestingly, although the PCH package only provides connections for 14 USB 2.0 signals, those signals can come from either the newer xHCI or the two legacy EHCI controllers which are still present on the chip.

DanNeely - Thursday, May 15, 2014 - link

Am I correctly understanding that as saying that by routing the signals separately you could create a USB3 only port that's not back compatible with USB 1/2?repoman27 - Thursday, May 15, 2014 - link

You're not allowed to do that according to the USB 3.0 Specification, but let's say you had an on board card reader that had a SuperSpeed USB interface, then you wouldn't necessarily be required to route a USB 2.0 signal to it as well and could use that signal for something else instead.repoman27 - Thursday, May 15, 2014 - link

If all the high speed signaling ports were Flex I/O ports, everyone who purchased a PC or motherboard based on that platform would be paying for an insanely large PCIe 2.0 switch with 18 downstream lanes/ports, an 18-port xHCI, and an 18-port SATA 6Gb/s controller plus 18 separate muxes to steer the desired signals to each port. I'm sure Intel would be happy to sell all that to the OEMs instead of just letting them use discrete controllers, but I seriously doubt it would end up lowering the BOM cost any. Flex I/O is just a way to keep the PCH package size down by steering features to a reduced number of balls. I'd rather be able to actually utilize all of the controllers I'm paying for.Not all of the chipsets offer 14 USB ports, and not all of the available USB ports are necessarily routed to external connectors or headers on the logic board. Some of them are used to connect devices on the motherboard itself or other embedded features. Also, since this many ports have been available since the 5 Series, Intel can't exactly regress the feature set while AMD is still offering 14 USB ports.

KAlmquist - Thursday, May 15, 2014 - link

With the current "Flex IO" design, Intel implemented 20 high speed controllers (8 PCIe, 6 SATA, and 6 USB 3.0), but only provided pinouts for 18 of them, meaning that two controllers sit unused. To provide full I/O flexibility, Intel would have to implement 54 controllers (18 of each type), 36 of which would be unused. It sounds like a waste of silicon to me.gloinsir - Wednesday, May 14, 2014 - link

The Rear IO abuses a Renesas USB 3.0 hub to one USB 3.0 port into four, bringing the total number of USB 3.0 ports the motherboard can handle to eight.Oh the poor Renasus abuse.

celestialgrave - Wednesday, May 14, 2014 - link

I guess I don't really see the need for wifi built into my desktop motherboard. I'd rather have the dual NICs. But I guess I can see the advantage when it comes to building a computer for mom or grandma.Ian Cutress - Wednesday, May 14, 2014 - link

If you have a family, more often than not there is a central WiFi router in the house connecting to everyone. If the house/flat isn't all layed out in RJ-45, then if everyone has a computer it has to get the WiFi signal for connections. For example, I have my NAS connected via ethernet to the router, but the three systems in my office are all connected via WiFi, as well as the HTPC in the front room.plopke - Wednesday, May 14, 2014 - link

I am still confused about what PCI-Express and M.2 supposed to be in the end for like a regular consumer? One time i read M.2 stuff and pice express will use the same protocl then other times i read articles like this that they wont work together , etcAny change anyone has some googlde docs spreadsheet that show a table like

connecter type motherboard | protocol | protocol max speed | connecter type SSD | speed SSD | max theorictal performance | compatible