Intel’s Silvermont Architecture Revealed: Getting Serious About Mobile

by Anand Lal Shimpi on May 6, 2013 1:00 PM EST- Posted in

- CPUs

- Intel

- Silvermont

- SoCs

ISA

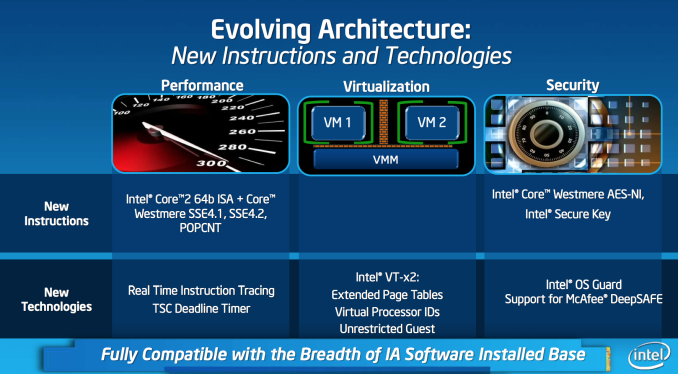

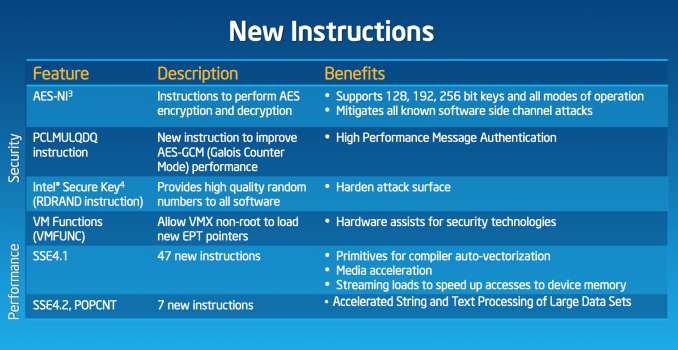

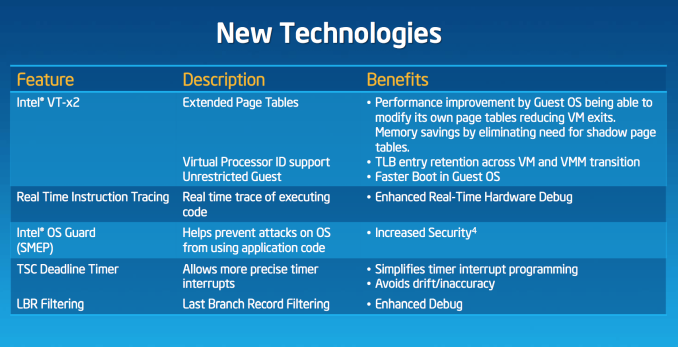

The original Atom processor enabled support for Merom/Conroe-class x86 instructions, it lacked SSE4 support due to die/power constraints; that was at 45nm, at 22nm there’s room for improvement. Silvermont brings ISA compatibility up to Westmere levels (Intel’s 2010 Core microprocessor architecture). There’s now support for SSE4.1, SSE4.2, POPCNT and AES-NI.

Silvermont is 64-bit capable, although it is up to Intel to enable 64-bit support on various SKUs similar to what we’ve seen with Atom thus far.

IPC and Frequency

The combination of everything Intel is doing on the IPC front give it, according to Intel, roughly the same single threaded performance as ARM’s Cortex A15. We’ve already established that the Cortex A15 is quite good, but here’s where Silvermont has a chance to pull ahead. We already established that Intel’s 22nm process can give it anywhere from a 18 - 37% performance uplift at the same power consumption. IPC scaling gives Silvermont stable footing, but the ability to run at considerably higher frequencies without drawing more power is what puts it over the top.

Intel isn’t talking about frequencies at this point, but I’ve heard numbers around 2 - 2.4GHz thrown around a lot. Compared to the 1.6 - 2GHz range we currently have with Bonnell based silicon, you can see how the performance story gets serious quickly. Intel is talking about a 50% improvement in IPC at the core, combine that with a 30% improvement in frequency without any power impact and you’re now at 83% better performance potentially with no power penalty. There are other advantages at the SoC level that once factored in drive things even further.

Real Turbo Modes & Power Management

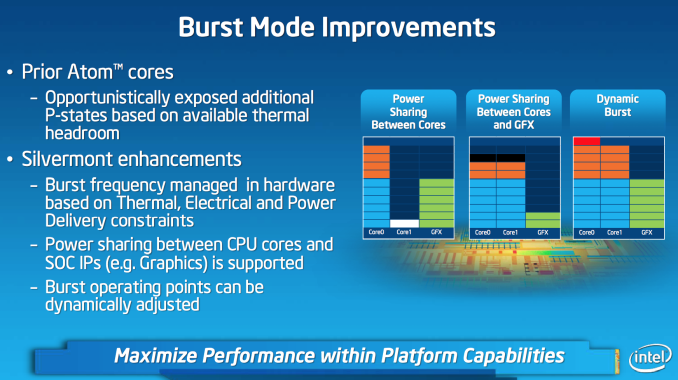

Previous Atom based mobile SoCs had a very crude version of Intel’s Turbo Boost. The CPU would expose all of its available P-states to the OS and as it became thermally limited, Intel would clamp the max P-state it would expose to the OS. Everything was OS-driven and previous designs weren’t able to capitalize on unused thermal budget elsewhere in the SoC to drive up frequency in active parts of chip. This lack of flexibility even impacted the SoC at the CPU core level. When running a single threaded app, Medfield/Clover Trail/et al couldn’t take thermal budget freed up by the idle core and use it to drive the frequency of the active core. Previous Atom implementations were basically somewhere in the pre-Nehalem era of thermal/boost management. From what I’ve seen, this is also how a lot of the present day ARM architectures work as well. At best, they vary what operating states they expose to the OS and clamp max frequency depending on thermals. To the best of my knowledge, none of the SoC vendors today actively implement modern big-core-Intel-like frequency management. Silvermont fixes this.

Silvermont, like Nehalem and the architectures that followed, gets its own power control unit that monitors thermals and handles dynamic allocation of power budget to various blocks within the SoC. If I understand this correctly, Silvermont should expose a maximum base frequency to the OS but depending on instruction mix and available TDP it can turbo up beyond that maximum frequency as long as it doesn’t exceed TDP. Like Sandy Bridge, Silvermont will even be able to exceed TDP for a short period of time if the package temperature is low enough to allow it. Finally, Silvermont’s turbo can also work across IP blocks: power budget allocated to the GPU can be transferred to the CPU cores (and vice versa).

By big-core standards (especially compared to Haswell), Silvermont’s turbo isn’t all that impressive but compared to how things are currently handled in the mobile space this should be a huge step forward.

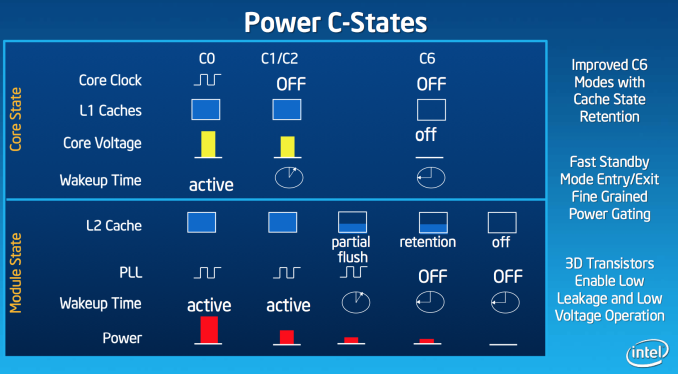

On the power management side, getting in and out of C6 should be a bit quicker. There's also a new C6 mode with cache state retention.

174 Comments

View All Comments

PolarisOrbit - Monday, May 6, 2013 - link

Re: FSBIntel tried to get rid of the FSB several years ago, but it was seen as anti-competitive because they simultaneously locked out 3rd parties like Nvidia Ion. One lawsuit later, Intel was bound to keep the FSB in their low power architectures until 2013 for 3rd party support. Basically Intel wasn't playing fair and Nvidia burned their ship.

DanNeely - Tuesday, May 7, 2013 - link

There was no usable FSB in anything beyond the first series of atom chips. The rest still had it within the die to connect the CPU with the internal northbridge; but the only external interface it offered was 4 PCIe2(?) lanes. ION2 connected to them; not to FSB.Kevin G - Tuesday, May 7, 2013 - link

Actually Intel is to keep PCI-e on their chips until 2016 by that anti-trust suit. This allows 3rd part IP, like nVidia's ION, to work with Intel's SoC designs.tipoo - Monday, May 6, 2013 - link

This makes me wonder if companies that make in-house SoCs (I guess Apple in specific, since Samsung also sells them to others while Apple just does it for themselves) will ever switch mobile devices to Intel if they just can't match the performance per watt of this and future Atom cores.tipoo - Monday, May 6, 2013 - link

Also won't the much anticipated SGX 600 series/Rogue be out by around then? That's the GPU that's supposed to take these mobile SoCs to the 200Gflop territory which the 360/PS3 GPUs are around.xTRICKYxx - Tuesday, May 7, 2013 - link

I would think Apple would (or any company) would want all of their software running on the same architecture/platform if they could.R0H1T - Tuesday, May 7, 2013 - link

And kill what a billion or so iDevices sold with incompatibility ? Me thinks you dunno what you're talking about !CajunArson - Monday, May 6, 2013 - link

Did somebody pay you to post that reply? Because if so, they aren't getting their money's worth.Silvermont Atoms are targeted at smartphones in 2-core configurations and tablets in the 4-core Baytrail configurations. Their power consumption is in a completely different league than even the low-end Temash parts. Let me reiterate: a Temash with a 4 watt TDP is going to have substantially higher real-world power consumption than even a beefy Baytrail and will likely only compete with the microserver Atom parts where Intel intentionally targets a higher power envelope.

I'm sure you can't wait to post benchmarks of a Kabini netbook with a higher power draw than Haswell managing to beat a smartphone Atom as proof that AMD has "won" something, but for those of us on planet earth, these Silvermont parts are very interesting and we appreciate hard technical information on the architecture.

nunomoreira10 - Tuesday, May 7, 2013 - link

Jaguar will be available on fanless designs wille haswell wont, you cant realy compare them.The facto is intel still doesn't hás a good enougf CPU for a good experiency on a legacy windows 8 fanless design, there is this big hole in the market that AMD is trying to seek.

raghu78 - Monday, May 6, 2013 - link

Intel silvermont is the start of the Intelization of the mobile world. within the next 2 - 3 years Intel should have bagged Apple , Google or Samsung. with the world's best manufacturing process which is atleast 2 - 3 years ahead of other foundries and Intel's relentless tick - tock chip development cadence the ARM crowd is going to be beaten to a pulp. Qualcomm might survive the Intel juggernaut but Nvidia will not.