The AMD Zen and Ryzen 7 Review: A Deep Dive on 1800X, 1700X and 1700

by Ian Cutress on March 2, 2017 9:00 AM ESTThe Core Complex, Caches, and Fabric

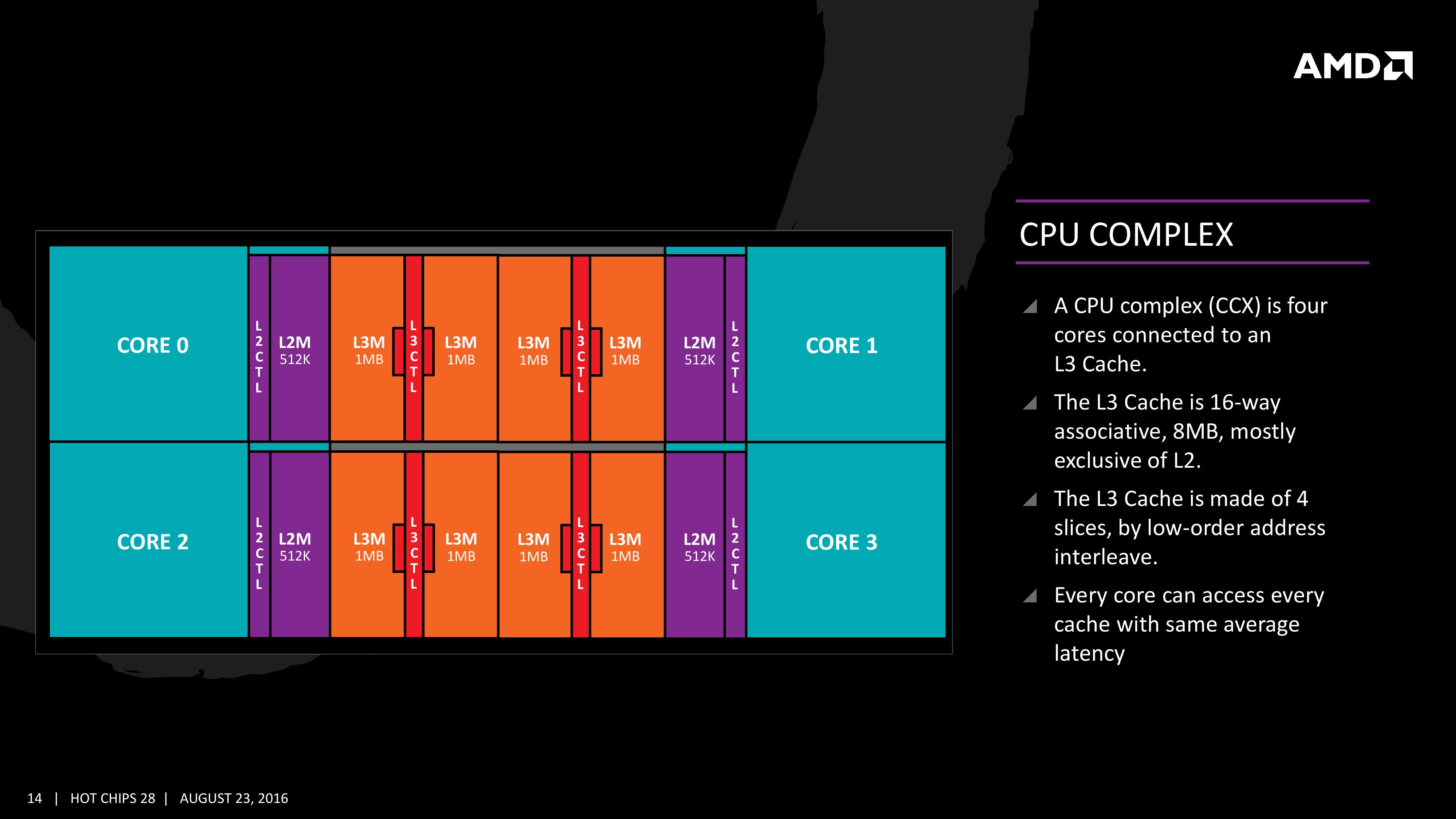

Many core designs often start with an initial low-core-count building block that is repeated across a coherent fabric to generate a large number of cores and the large die. In this case, AMD is using a CPU Complex (CCX) as that building block which consists of four cores and the associated caches.

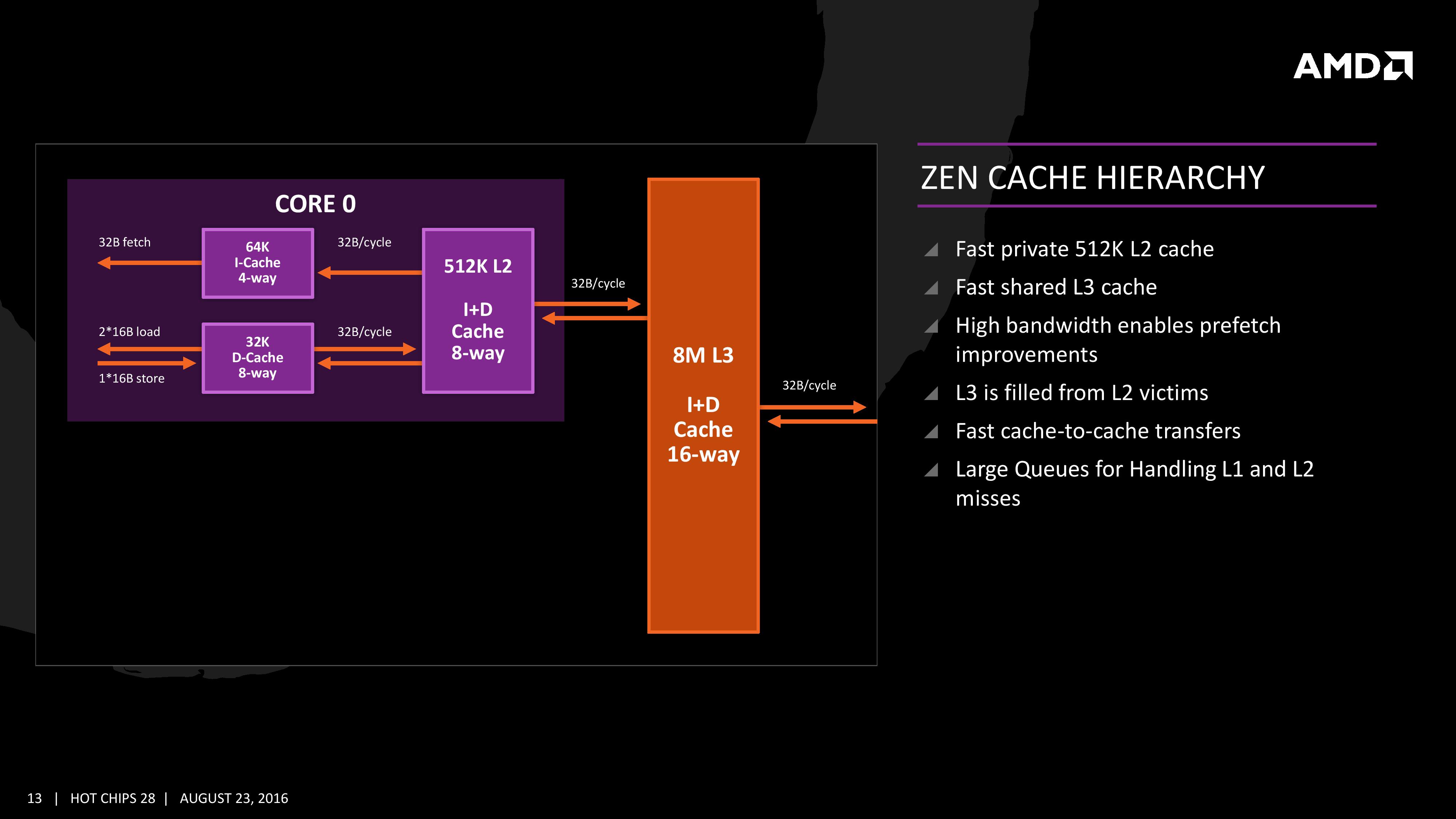

Each core will have direct access to its private L2 cache, and the 8 MB of L3 cache is, despite being split into blocks per core, accessible by every core on the CCX with ‘an average latency’ also L3 hits nearer to the core will have a lower latency due to the low-order address interleave method of address generation.

The L3 cache is actually a victim cache, taking data from L1 and L2 evictions rather than collecting data from prefetch/demand instructions. Victim caches tend to be less effective than inclusive caches, however Zen counters this by having a sufficiency large L2 to compensate. The use of a victim cache means that it does not have to hold L2 data inside, effectively increasing its potential capacity with less data redundancy.

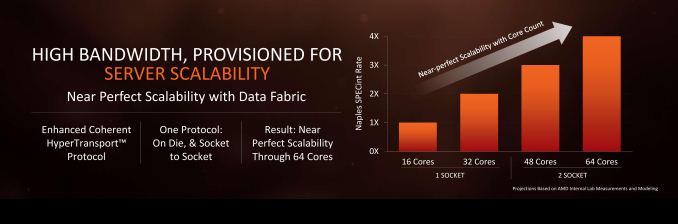

It is worth noting that a single CCX has 8 MB of cache, and as a result the 8-core Zen being displayed by AMD at the current events involves two CPU Complexes. This affords a total of 16 MB of L3 cache, albeit in two distinct parts. This means that the true LLC for the entire chip is actually DRAM, although AMD states that the two CCXes can communicate with each other through the custom fabric which connects both the complexes, the memory controller, the IO, the PCIe lanes etc.

The cache representation shows L1 and L2 being local to each the core, followed by 8MB of L3 split over several cores. AMD states that the L1 and L2 bandwidth is nearly double that of Excavator, with L3 now up to 5x for bandwidth, and that this bandwidth will help drive the improvements made on the prefetch side. AMD also states that there are large queues in play for L1/L2 cache misses.

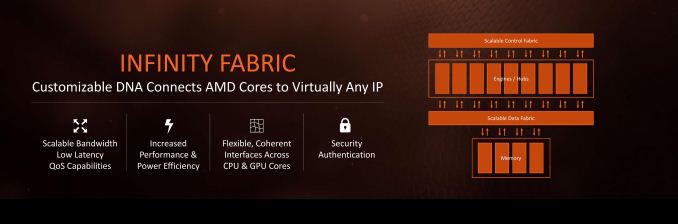

One interesting story is going to be how AMD’s coherent fabric works. For those that follow mobile phone SoCs, we know fabrics and interconnects such as CCI-400 or the CCN family are optimized to take advantage of core clusters along with the rest of the chip. A number of people have speculated that the fabric used in AMD’s new design is based on HyperTransport, however AMD has confirmed that they are using a superset HyperTransport here for Zen, and that the Infinity fabric design is meant to be high bandwidth, low latency, and be in both Zen and Vega as well as future products. Almost similar to the CPU/GPU roadmaps, the Fabric has its own as well.

Ultimately the new fabric involves a series of control and data passing structures, with the data passing enabling third-party IP in custom designs, a high-performance common bus for large multi-unit (CPU/GPU) structures, and socket to socket communication. The control elements are an extension of power management, enabling parts of the fabric to duty cycle when not in use, security by way of memory management and detection, and test/initialization for activities such as data prefetch.

574 Comments

View All Comments

ABR - Sunday, March 5, 2017 - link

Are there any examples of games at 1080p where this actually matters? (I.e., not a drop from 132 to 108 fps, but from 65 to 53 or 42 to 34?)ABR - Monday, March 6, 2017 - link

I mean at 1080p. (Edit, edit...)0ldman79 - Monday, March 6, 2017 - link

That's my thought as well.Seriously, it isn't like we're talking unplayable, it is still ridiculous gaming levels. It is almost guaranteed to be a scheduler problem in Windows judging by the performance deficit compared to other applications. If it isn't, it is still running very, very well.

Hell, I can play practically anything I can think of on my FX 6300, I don't really *need* a better CPU right now, I'm just really, really tempted and looking for excuses (I can't encode at the same speed in software as my Nvidia encoder, damn, I need to upgrade...)

Outlander_04 - Monday, March 6, 2017 - link

Do you think anyone building a computer with a $500 US chip is going to just be spending $120 on a 1080p monitor?More likely they will be building it for higher resolutions

Notmyusualid - Tuesday, March 7, 2017 - link

I've seen it happen...mdriftmeyer - Tuesday, March 7, 2017 - link

Who gives a crap if you've seen it happen. Your experience is an anomaly relative to the totality of statistical data.Notmyusualid - Wednesday, March 8, 2017 - link

Or somebody was just happy with their existing screen?I can actually point to two friends with 1080 screens, both lovely water cooled rigs, one is determined to keep his high-freq 1080 screen, and the other one just doesn't care. So facts is facts son.

I guess it is YOU that gives that crap afterall.

Zaggulor - Thursday, March 9, 2017 - link

Statistical data suggests that people don't actually often get a new display when they change a GPU and quite often that same display will be moved to a new rig too.Average upgrade times for components are:

CPU: ~4.5 years

GPU: ~2.5 years

Display: ~7 years

These days you can also use any unused GPU resources for downsampling even if your CPU can't push any more frames. Both GPU vendors have build in support for it (VSR/DSR).

hyno111 - Wednesday, March 8, 2017 - link

Or a $200 1080p/144Hz/Freesync monitor.Marburg U - Sunday, March 5, 2017 - link

I guess it's time to retire my Core 2 Quad.