Facebook's "Open Compute" Server tested

by Johan De Gelas on November 3, 2011 12:00 AM ESTPower Supply Efficiency Visualized

I graduated as an electromechanical engineer, but 17 years of IT jobs and research have helped me forget a lot about electricity and electronics. However, I have the advantage of running the Sizing Servers Lab (at the university college of West-flanders, Howest) and thus the privilege of working with some very talented people. Tijl Deneut told me he would be able to visualize the efficiency of the power supply. So with the advanced Racktivity PDU, he managed to produce a time graphic that shows how close the current sine wave remains to to the voltage sine wave. If the two are perfectly in phase, the power quality or power factor is 100%.

In your own home, this power factor is less important. However, large installations such as a data centers have to pay extra for bad power factors as a low power factor causes the electrical system to draw more current for the same amount of work being done, and more current results in higher heat losses.

Data centers have large power factor correctors, electronic systems with large capacitors that improve the PF but also consume energy. A bad PF can increase the Power Usage Effectiveness (PUE) of the data center, and this PUE has become an extremely important "benchmark" for data centers. The less these systems have to work the better, so the PF of a server PSU should be as close to 1 as possible.

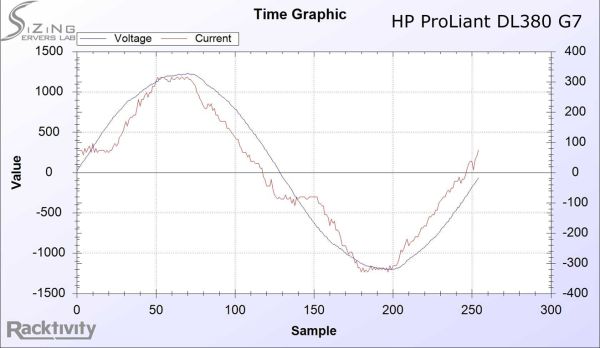

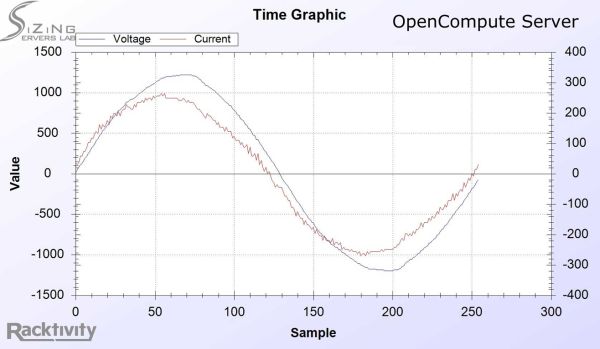

We started by measuring while the server is close to idle, which is a pretty bad scenario for the PF. First let's look at the sine waves of the HP DL380 G7:

That's not bad at all, but next let's look at the sine waves of the AC that enters the Open Compute server

The current sine wave is not only closer to the voltage sine wave, it is also much closer to the ideal form of an AC sine wave, which makes energy delivery more efficient. It is one of the first indications that the Facebook engineers did their homework very well.

67 Comments

View All Comments

JohanAnandtech - Thursday, November 3, 2011 - link

It is an ATI ES 1000, that is a server/thin client chip. That chip is only 2D. I can not find the power specs, but considering that the chip does not even need a heatsink, I think this chip consumes maybe 1W in idle.mczak - Thursday, November 3, 2011 - link

ES 1000 is almost the same as radeon 7000/ve (no that's not HD 7000...) (some time in the past you could even force 3d in linux with the open-source driver though it usually did not work). The chip also has dedicated ram chip (though only 16bit wide memory interface) and I'm not sure how good the powersaving methods of it are (probably not downclocking but supporting clock gating) - not sure if it fits into 1W at idle (but certainly shouldn't be much more).JohanAnandtech - Thursday, November 3, 2011 - link

I can not find any good tech resources on the chip, but I can imagine that AMD/ATI have shrunk the chip since it's appearance in 2005. If not, and the chip does consume quite a bit, it is a bit disappointing that server vendors still use it as the videochip is used very rarely. You don't need a videochip for RDP for example.mczak - Thursday, November 3, 2011 - link

I think the possibility of this chip being shrunk since 2005 is 0%. The other question is if it was shrunk from rv100 or if it's actually the same - even if it was shrunk it probably was a well mature process like 130nm in 2005 otherwise it's 180nm.At 130nm (estimated below 20 million transistors) the die size would be very small already and probably wouldn't get any smaller due to i/o anyway. Most of the power draw might be due to i/o too so shrink wouldn't help there neither. It is possible though it's really below 1W (when idle).

Taft12 - Thursday, November 3, 2011 - link

A shrink WOULD allow production of many more units on each wafer. Since almost every server shipped needs an ES1000 chip, demand is consistently on the order of millions per year.mczak - Thursday, November 3, 2011 - link

There's a limit how much i/o you can have for a given die size (actually the limiting factor is not area but circumference so making it rectangular sort of helps). i/o pads apparently don't shrink well hence if your chip has to have some size because you've got too many i/o pads a shrink will do nothing but make it more expensive (since smaller process nodes are generally more expensive per area).Being i/o bound is quite possible for some chips though I don't know if this one really is - it's got at least display outputs, 16bit memory interface, 32bit pci interface and the required power/ground pads at least.

In any case even at 180nm the chip should be below 40mm² already hence the die size cost is probably quite low compared to packaging, cost of memory etc.

Penti - Saturday, November 5, 2011 - link

It's the integrated BMC/ILO solution which also includes a GPU that would use more power then the ES1000 any how. That is also what is lacking in the simple Google / Facebook compute-node setup. They don't need that kind off management and can handle that a node goes offline.haplo602 - Thursday, November 3, 2011 - link

It seems to me that the HP server is doing as well as the Facebook ones. Considering it has more featuers (remote management, integrated graphics) and a "common" PSU.JohanAnandtech - Thursday, November 3, 2011 - link

The HP does well. However, if you don't need integrated graphics and you hardly use the BMC at all, you still end up with a server that wastes power on features you hardly use.twhittet - Thursday, November 3, 2011 - link

I would assume cost is also a major factor. Why pay for so many features you don't need? Manufacturing costs should be lower if they actually build these in bulk.