Intel Announces Skylake-X: Bringing 18-Core HCC Silicon to Consumers for $1999

by Ian Cutress on May 30, 2017 3:03 AM ESTAnnouncement Three: Skylake-X's New L3 Cache Architecture

(AKA I Like Big Cache and I Cannot Lie)

SKU madness aside, there's more to this launch than just the number of cores at what price. Deviating somewhat from their usual pattern, Intel has made some interesting changes to several elements of Skylake-X that are worth discussing. Next is how Intel is implementing the per-core cache.

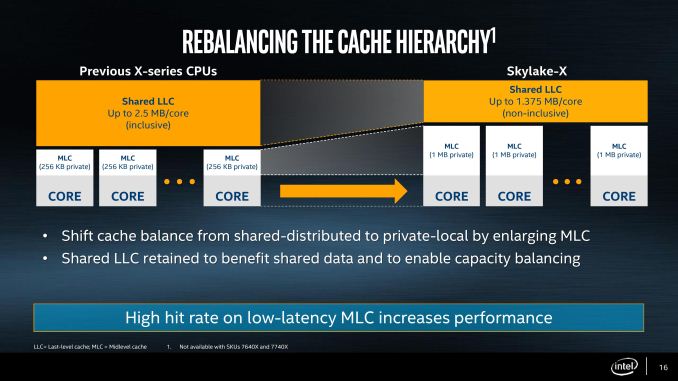

In previous generations of HEDT processors (as well as the Xeon processors), Intel implemented an three stage cache before hitting main memory. The L1 and L2 caches were private to each core and inclusive, while the L3 cache was a last-level cache covering all cores and that also being inclusive. This, at a high level, means that any data in L2 is duplicated in L3, such that if a cache line is evicted into L2 it will still be present in the L3 if it is needed, rather than requiring a trip all the way out to DRAM. The sizes of the memory are important as well: with an inclusive L2 to L3 the L3 cache is usually several multiplies of the L2 in order to store all the L2 data plus some more for an L3. Intel typically had 256 kilobytes of L2 cache per core, and anywhere between 1.5MB to 3.75MB of L3 per core, which gave both caches plenty of room and performance. It is worth noting at this point that L2 cache is closer to the logic of the core, and space is at a premium.

With Skylake-X, this cache arrangement changes. When Skylake-S was originally launched, we noted that the L2 cache had a lower associativity as it allowed for more modularity, and this is that principle in action. Skylake-X processors will have their private L2 cache increased from 256 KB to 1 MB, a four-fold increase. This comes at the expense of the L3 cache, which is reduced from ~2.5MB/core to 1.375MB/core.

With such a large L2 cache, the L2 to L3 connection is no longer inclusive and now ‘non-inclusive’. Intel is using this terminology rather than ‘exclusive’ or ‘fully-exclusive’, as the L3 will still have some of the L3 features that aren’t present in a victim cache, such as prefetching. What this will mean however is more work for snooping, and keeping track of where cache lines are. Cores will snoop other cores’ L2 to find updated data with the DRAM as a backup (which may be out of date). In previous generations the L3 cache was always a backup, but now this changes.

The good element of this design is that a larger L2 will increase the hit-rate and decrease the miss-rate. Depending on the level of associativity (which has not been disclosed yet, at least not in the basic slide decks), a general rule I have heard is that a double of cache size decreases the miss rate by the sqrt(2), and is liable for a 3-5% IPC uplift in a regular workflow. Thus here’s a conundrum for you: if the L2 has a factor 2 better hit rate, leading to an 8-13% IPC increase, it’s not the same performance as Skylake-S. It may be the same microarchitecture outside the caches, but we get a situation where performance will differ.

Fundamental Realisation: Skylake-S IPC and Skylake-X IPC will be different.

This is something that fundamentally requires in-depth testing. Combine this with the change in the L3 cache, and it is hard to predict the outcome without being a silicon design expert. I am not one of those, but it's something I want to look into as we approach the actual Skylake-X launch.

More things to note on the cache structure. There are many ‘ways’ to do it, one of which I imagined initially is a partitioned cache strategy. The cache layout could be the same as previous generations, but partitions of the L3 were designated L2. This makes life difficult, because then you have a partition of the L2 at the same latency of the L3, and that brings a lot of headaches if the L2 latency has a wide variation. This method would be easy for silicon layout, but hard to implement. Looking at the HCC silicon representation in our slide-deck, it’s clear that there is no fundamental L3 covering all the cores – each core has its partition. That being the case, we now have an L2 at approximately the same size as the L3, at least per core. Given these two points, I fully suspect that Intel is running a physical L2 at 1MB, which will give the design the high hit-rate and consistent low-latency it needs. This will be one feather in the cap for Intel.

203 Comments

View All Comments

TEAMSWITCHER - Tuesday, May 30, 2017 - link

The reality is ... that despite having a 14C/28T machine ... you will probably still browse more on your smartphone.Notmyusualid - Wednesday, May 31, 2017 - link

Nope - I despise browsing on my smartphone, but I do use it as a telephone / walkman / GPS mostly, if that is not too unusual? I'm not one of the 'head-down generation', and I'll try not to pick up my phone in restaurants, at meetings, in the pub, or when crossing the road.My 14C/28T is the one usually busy browsing (its just SO smoooth), or when I'm on the road like now - running World Community Grid, mining Ethereum, or just being my UK-based Remote Desktop - so I can deal with bills / deal with Paypal etc - without having to reset my account password everytime as is often required when I login from overseas...

AMD's Threadripper & Intels new offerings are onto something here though - these large core count chips offer the smoothest computing experience you are ever going to find. Complex HTML pages are dealt with ease... installs zip by, archives unpacked so quickly, boot times (save for X99 bios) are nearly instant.

I'll take that 12C/24T from Intel about this time next year.

Kevin G - Tuesday, May 30, 2017 - link

I actually do that for work email. Not because my quad core i7 based laptop is slow. Rather that Outlook wasn't written by programmers but sadists who enjoy mass suffering. Some desktop applications are so flawed going to another tool to save me the pain and hassle is more efficient.Namisecond - Wednesday, May 31, 2017 - link

You need to clean out your mailbox and the Exchange admins need to run maintenance on the databases. When you've got less than a 4GB .ost file, stuff works well. :ptheuglyman0war - Thursday, June 8, 2017 - link

last legs? The desktop market was a multi billion dollar market before internet saturation and it will still be one after all the house wives and kiddies are on phones n consoles. Then it will resemble the HEDT market that use to cater to me and was not second guessed for silly non HEDT ( non workstation concerns ).Good riddance!

eddman - Tuesday, May 30, 2017 - link

Absolutely not interested in these. Do they have any plans to release 6 and 8 core models for socket 1151?extide - Tuesday, May 30, 2017 - link

I think we will see 6 cores on next gen mainstream design which may indeed be 1151 compatible...Teknobug - Tuesday, May 30, 2017 - link

Well so much for having interest in the i9, pricepoint is way out of whack.martinkrol - Tuesday, May 30, 2017 - link

I am thinking the same. Since I do a lot of 3d work I am thinking of upgrading my i7 3930k to a double xeon of that same generation or just slightly newer. It will allow me to use a lot more ram, and get double the threads which will help in multi-tasking. ( working and rendering on the same box for example ). Nowadays an hp z820 goes for fairly cheap and I can outfit that with 256gb ram for around the same price as one of these new top end i9 processors.ltcommanderdata - Tuesday, May 30, 2017 - link

Any word on whether Skylake-X is treated like the rest of Skylake by Microsoft/Intel and has official Windows 7/8.1 support? Or will Broadwell-E remain the fastest/last CPUs that have official multi-boot support for Windows 7/8.1/10?x