The AMD Zen and Ryzen 7 Review: A Deep Dive on 1800X, 1700X and 1700

by Ian Cutress on March 2, 2017 9:00 AM ESTAMD Ryzen 7 Launch Details

The Ryzen family of CPUs is designed to compete, initially, in the performance-mainstream and high-end desktop market. At first will be the launch of Ryzen 7 CPUs, a trio of eight-core, sixteen-thread designs, with Ryzen 5 and Ryzen 3 coming in Q2 and 2H17 respectively. Out of the CPUs we know about, the Ryzen 7 parts, the processors have a TDP of either 65W or 95W, and prices will range from $330 to $500.

| AMD Ryzen 7 SKUs | ||||||

| Cores/ Threads |

Base/ Turbo |

L3 | TDP | Cost | Launch Date | |

| Ryzen 7 1800X | 8/16 | 3.6/4.0 | 16 MB | 95 W | $499 | 3/2/2017 |

| Ryzen 7 1700X | 8/16 | 3.4/3.8 | 16 MB | 95 W | $399 | 3/2/2017 |

| Ryzen 7 1700 | 8/16 | 3.0/3.7 | 16 MB | 65 W | $329 | 3/2/2017 |

All the processors will be using the AM4 socket, with bases frequencies from 3.2 GHz to 3.6 GHz, and turbo frequencies up to 4.0 GHz for the high-end parts. The base design supports 512KB of private L2 cache per core and 2MB of a shared exclusive L3 victim cache.

The CPUs follow a naming scheme which most CPU enthusiasts will be familiar with:

- The high-end parts are ‘Ryzen 7’, which all happen to be eight-core parts and start around $300-$320. With a fully enabled chip, 16MB of L3 cache is available.

- In the mid-range are ‘Ryzen 5’ processors, set to be launched in Q2, which are all eight-core parts under the hood but are either 6-core parts or 4-core parts depending on the model. Leaks would tend to suggest that despite having two cores disabled, the 6-core parts still have access to all the L3 cache.

- At the bottom are ‘Ryzen 3’, due 2H17, all of which are quad core parts but do not have hyperthreading.

- All parts support overclocking.

- Technically all parts support XFR, although only X can overclock with XFR (more on this later)

- It’s worth noting that ‘Ryzen 7 1900X’ is a gap waiting to be filled.

The formal name for these CPUs is ‘Ryzen 7’ followed by the SKU number. Having conversations with AMD, and noting that I suspect these names will colloquially be shortened to R7, R5 and R3 very quickly, we will be following convention and using the formal CPU names.

All these parts come from a single silicon design, with binning to ensure that the quality of each silicon die gets placed in the right bin. It is worth noting AMD’s tactics to launch a handful of SKUs at once follows on from its previous strategy. Part of it is a function of size (AMD by contrast to other players is actually small), and it allows AMD to react to how the market changes, as well as adjust product lines due to factors in the production (such as better semi-con characteristics).

All the CPUs are multiplier unlocked, allowing users to go overclocking when paired with the X370 or B350 chipset. At this point we’re unsure what the upper limit is for the multiplier. We have been told that all CPUs will also support XFR, whereby the CPU automatically adjusts the frequency rather than the OS based on P-states, but the CPUs with ‘X’ in the name allow the CPU to essentially overclock over the turbo frequency. XFR stands for ‘eXtended Frequency Range’, and indicates that the CPU will automatically overclock itself if it has sufficient thermal and power headroom. We’ll mention it later, but XFR works in jumps of 25 MHz by adjusting the multiplier, which also means that the multiplier is adjustable in 0.25x jumps (as they have 100 MHz base frequency). XFR does have an upper limit, which is processor dependent. All CPUs will support 25 MHz jumps though XFR above the P0 state, but only X CPUs will go beyond the turbo frequency.

A side note: As to be expected, XFR only works correctly if the correct setting in the BIOS is enabled. At this point the option seems to be hidden, but if exposed it means it is up to the motherboard manufacturers to enable it by default – so despite it being an AMD feature, it could end up at the whim of the motherboard manufacturers. I suspect we will see some boards with XFR enabled automatically, and some without. We had the same issue on X99 with Turbo Boost 3, and Multi-Core Turbo.

So Why No Ryzen 5 or Ryzen 3?

AMD is remaining relatively quiet on the other Ryzen CPUs. At the Tech Day, we were told about one other CPU: the Ryzen 5 1600X.

| AMD Ryzen SKUs | ||||||

| Cores/ Threads |

Base/ Turbo |

L3 | TDP | Cost | Launch Date | |

| Ryzen 7 1800X | 8/16 | 3.6/4.0 | 16 MB | 95 W | $499 | 3/2/2017 |

| Ryzen 7 1700X | 8/16 | 3.4/3.8 | 16 MB | 95 W | $399 | 3/2/2017 |

| Ryzen 7 1700 | 8/16 | 3.0/3.7 | 16 MB | 65 W | $329 | 3/2/2017 |

| Ryzen 5 1600X | 6/12? | 3.6/4.0 | 16 MB? | ? W | N/A | Q2 2017 |

| Ryzen 3 ? | 4/4? | ? | 8 MB? | ? W | N/A | H2 2017 |

This six-core part will have two CPU cores disabled, though it is unclear if AMD will disable one core per cluster of four (giving a 3+3 arrangement) or if they could disable two from one cluster (giving 2+4). Nonetheless, it maintains the 3.6 GHz base frequency and 4.0 GHz turbo frequency similar to the Ryzen 7 1800X. This puts it square in the firing line of the Core i7-6850K (six core, Broadwell-E) and Core i7-5930K (six core, Haswell-E).

Ryzen 5 is scheduled for ‘Q2’, meaning the second quarter of 2017, or April-to-June inclusive. The big event in that time frame in the PC world is Computex at the beginning of June, which might be an apt time to launch some other products as well. The scale of the Ryzen 5 launch is unknown, and I suspect that if the demand for Ryzen 7 is high then AMD might not have enough CPUs to go around. If enough parts come out of the Fab working well, and Ryzen 7 is still selling strong, then we might have to wait for Ryzen 5. This aids part of AMD’s trickle-out strategy, though based on some of the comments we’re seeing online, Ryzen 5 is also highly anticipated.

The Ryzen 3 family is even more unknown. At this point the leaks suggest that these will be quad core parts without simultaneous multi-threading, however AMD has not released any information as to how they will work. The only thing we know is that AMD is planning a H2'17 launch, meaning the second half of 2017. That’s a very, very wide window, encompassing things like the Server chips launch but also the notebook SoCs. I suspect AMD will be constantly looking at their product lines and sales, determining what opportunities there are for Ryzen 3 CPUs – if they get a full launch or end up a footnote if the rest of the stack performs above expectations. Or Ryzen 3 could end up mobile only, but that’s just a low-chance hypothesis.

I saw Ryzen Pro being in the leaks?

At this time AMD is not announcing any Pro parts, although it was confirmed to be that there are plans to continue the Pro line of CPUs with Ryzen to be launched at a later time. These parts will be similar in practice to previous ‘Pro’ models we saw with Kaveri and Carrizo: designed for the big OEMs as an indication of large-contract support. AMD’s prominent partners for this are HP, Lenovo and Dell. These processors will most likely not be sold to the public, although OEM resellers typically get hold of a few. That means availability at this point is unknown. AMD states that multiplier overclocking is supported on all processors, however at the time of writing we’re unsure if that would naturally include the ‘Pro’ line. My gut instinct says ‘probably’, although the systems these CPUs will go into will likely have overclocking disabled, so it would have to be placed into a consumer motherboard.

A side note on ECC: given the design of Naples and the fact that it should be supporting ECC, this means that the base memory controller in the silicon should be able to support ECC. We know that it is disabled for the consumer parts, but nothing has been said regarding the Pro parts. We can confirm that ECC is enabled on the consumer Ryzen parts.

The Competition

Just after Tech Day, I ran a twitter poll regarding comparisons that my followers were interested in. The poll results were as follows:

So what CPU comparison is more vital for you? (for other suggestions, simply reply)

— Ian Cutress (@IanCutress) February 24, 2017

That’s

- 32% for the Ryzen 7 1800X vs Core i7-7700K,

- 31% for the Ryzen 7 1700 vs Core i7-7700K

- 25% for the Ryzen 7 1800X vs Core i7-6900K

- 11% for the Ryzen 7 1700 vs Core i7-2600K

- Mentions for

- Core i3-7350K numbers,

- Core i5-7600K numbers,

- Ryzen 5 1600X numbers (no can do before R5 launch)

- 1800X vs i7-5960X,

- 1700X vs 7700K,

- 1700X vs 6900K,

- DRAM testing,

- single thread testing,

- Maximum OC on each Ryzen part

- SPEC06 vs A10

- Dual Core Ryzen at 800 MHz vs Core m3 to simulate passive tablets

Naturally AMD has suggested processors which it feels offer direct competition against the various Ryzen CPUs. These are as follows:

| Comparison: Ryzen 7 1800X vs Core i7-6900K | ||

| AMD Ryzen 7 1800X |

Features | Intel Core i7-6900K |

| 8 / 16 | Cores/Threads | 8 / 16 |

| 3.6 / 4.0 GHz | Base/Turbo | 3.2 / 3.7GHz |

| 16 | PCIe 3.0 Lanes | 40 |

| 16 MB | L3 Cache | 20 MB |

| 95 W | TDP | 140 W |

| $499 | Price (MSRP) | $1049 |

At the top end we see the eight-core R7 1800X put directly against a Broadwell-E based eight-core Core i7-6900K. The Ryzen 7 1800X sits at 3.6 GHz base and 4.0 GHz turbo for 95W, while the Core i7-6900X is 3.2G/3.7G for 140W. The i7-6900K has the bigger L3 cache and more PCIe lanes, but costs twice as much ($1049 vs. $499).

| Comparison: Ryzen 7 1700 vs Core i7-7700K | ||

| AMD Ryzen 7 1700 |

Features | Intel Core i7-7700K |

| 8 / 16 | Cores/Threads | 4 / 8 |

| 3.0 / 3.7 GHz | Base/Turbo | 4.2 / 4.5 GHz |

| 16 | PCIe 3.0 Lanes | 16 |

| 16 MB | L3 Cache | 8MB |

| 65 W | TDP | 91 W |

| $329 | Price (MSRP) | $350 |

In the mid-range, the Ryzen 7 1700 is so near in price to the Core i7-7700K that it is hard to miss. The i7-7700K is based on Intel’s latest Kaby Lake microarchitecture, which AMD has already shown is ahead of the game compared to Zen. So while Intel gets a frequency advantage (4.2G/4.5G vs 3.0G/3.7G) and is likely to have a fundamental IPC advantage, the AMD Ryzen 7 1700 comes with eight cores over four, and has 16MB of L3 cache compared to 8MB on Intel. The 1700 and 7700K are similar in price ($330 vs $350) but the 1700 also comes with a new variant of AMD’s high performing Wraith cooler.

| Comparison: Ryzen 5 1600X vs Core i5-7600K | ||

| AMD Ryzen 5 1600X |

Features | Intel Core i5-7600K |

| 6 / 12 | Cores/Threads | 4 / 4 |

| 3.6 / 4.0 GHz | Base/Turbo | 3.8 / 4.2GHz |

| 16 | PCIe 3.0 Lanes | 16 |

| 16 MB? | L3 Cache | 6 MB |

| ? | TDP | 91W |

| ? | Price (MSRP) | $239 |

Because we know some specs already, it’s worth pointing out about the Ryzen 5 1600X. Expected pricing should put it close to the price of the Core i5-7600K, but offering three times as many threads. The Ryzen 5 will be down on frequency, but cache and cores is hard to miss. When we get in the Ryzen 5 samples it is sure to be a major test.

The validity of these comparisons will come down to how well AMD has executed in single core performance, and if having the L3 as an exclusive victim cache actually hampers performance, especially in memory heavy workloads such as compression.

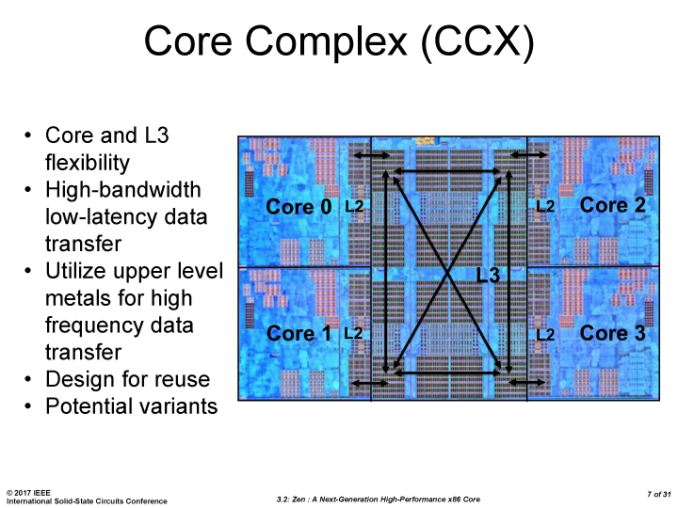

Typically we would expect fewer cores at the same power to be clocked higher as there is TDP to spare. However, these four core designs can differ between two successive chips. The base design of all of these CPUs is a set of eight cores, split into two quad-core ‘Core Complexes’ (known as a CCX). Each CCX has four cores and 8MB of L3 cache, but are still part of the same silicon die and connected by the new Infinity Fabric. For a quad core design, four of those cores (and their L3 caches) are disabled, however it is never guaranteed which ones. Users could end up with 4+0, 1+3 or 2+2 cores active per CCX, which gives a slightly skewed latency response when having to pull memory from other caches. Because the L3 cache is an exclusive victim cache, this won’t happen as often as perhaps an inclusive cache might, but as a result it is expected that the reduce frequency might be to compensate for the different CCX configurations that might exist.

574 Comments

View All Comments

nt300 - Saturday, March 11, 2017 - link

If AMD hadn't gone with GF's 14nm process, ZEN would probably have been delayed. I think as soon as Ryzen Optimizations come out, these chips will further outperform.MongGrel - Thursday, March 9, 2017 - link

For some reason making a casual comment about anything bad about the chip will get you banned at the drop of a hat on the tech forums, and then if you call him out they will ban you more.

https://arstechnica.com/gadgets/2017/03/amds-momen...

MongGrel - Thursday, March 9, 2017 - link

For some reason, MarkFW seems to thinks he is the reincarnation of Kyle Bennet, and whines a lot before retreating to his safe space.nt300 - Saturday, March 11, 2017 - link

I've noticed in the past that AMD has an issue with increasing L3 cache speed and/or Latencies. Hopefully they start tightening the L3 as much as possible. Can Anandtech do a comparison between Ryzen before Optimizations and after Optimizations. Tyalpha754293 - Friday, March 17, 2017 - link

Looks like that for a lot of the compute-intensive benchmarks, the new Ryzen isn't that much better than say a Core i5-7700K.That's quite a bit disappointing.

AMD needs to up their FLOPS/cycle game in order to be able to compete in that space.

Such a pity because the original Opterons were a great value proposition vs. the Intels. Now, it doesn't even come close.

deltaFx2 - Saturday, March 25, 2017 - link

@Ian Cutress: When you do test gaming, if you can, I'd love to have the hypothesis behind the 'generally accepted methodology' tested out. The methodology being, to test it at lowest resolution. The hypothesis is that this stresses the CPU, and that a future, higher performance GPU will be bottlenecked by the slower CPU. Sounds logical, but is it?Here's the thing: Typically, when given more computing resources, people scale up their problem to utilize those resources. In other words, if I give you a more powerful GPU, games will scale up their perf requirements to match it, by doing stuff that were not possible/practical in earlier GPUs. Today's games are far more 'realistic' and are played at much higher resolutions than say 5 years ago. In which case, the GPU is always the limiting factor no matter what (unless one insists on playing 5 year old games on the biggest, baddest GPU). And I fully expect that the games of today are built to max out current GPUs, so hardware lags software.

This has parallels with what happens in HPC: when you get more compute nodes for HPC problems, people scale up the complexity of their simulations rather than running the old, simplified simulations. Amdahl's law is still not a limiting factor for HPC, and we seem to be talking about Exascale machines now. Clearly, there's life in HPC beyond what a myopic view through the Amdahl law lens would indicate.

Just a thought :) Clearly, core count requirements have gone up over the last decade, but is it true that a 4c/8t sandy bridge paired up with Nvidia's latest and greatest is CPU-bottlenecked at likely resolutions?

wavelength - Friday, March 31, 2017 - link

I would love to see Anand test against AdoredTV's most recent findings on Ryzen https://www.youtube.com/watch?v=0tfTZjugDegLawJikal - Friday, April 21, 2017 - link

What I'm surprised to see missing... in virtually all reviews across the web... is any discussion (by a publication or its readers) on the AM4 platform's longevity and upgradability (in addition to its cost, which is readily discussed).Any Intel Platform - is almost guaranteed to not accommodate a new or significantly revised microarchitecture... beyond the mere "tick". In order to enjoy a "tock", one MUST purchase a new motherboard (if historical precedent is maintained).

AMD AM4 Platform - is almost guaranteed to, AT LEAST, accommodate Ryzen "II" and quite possibly Ryzen "III" processors. And, in such cases, only a new processor and BIOS update will be necessary to do so.

This is not an insignificant point of differentiation.

PeterCordes - Monday, June 5, 2017 - link

The uArch comparison table has some errors for the Intel columns. Dispatch/cycle: Skylake can read 6 uops per clock from the uop cache into the issue queue, but the issue stage itself is still only 4 uops wide. You've labelled Even running from the loop buffer (LSD), it can only sustain a throughput of 4 uops per clock, same 4-wide pipeline width it has been since Core2. (pre-Haswell it has to be a mix of ALU and some store or load to sustain that throughput without bottlenecking on the execution ports.) Skylake's improved decode and uop-cache bandwidth lets it refill the uop queue (IDQ) after bubbles in earlier stages, keeping the issue stage fed (since the back-end is often able to actually keep up).Ryzen is 6-wide, but I think I've read that it can only issue 6 uops per clock if some of them are from "double instructions". e.g. 256-bit AVX like VADDPS ymm0, ymm1, ymm2 that decodes to two separate 128-bit uops. Running code with only single-uop instructions, the Ryzen's front-end throughput is 5 uops per clock.

In Intel terminology, "dispatch" is when the scheduler (aka Reservation Station) sends uops to the execution units. The row you've labelled "dispatch / cycle" is clearly the throughput for issuing uops from the front-end into the out-of-order core, though. (Putting them into the ROB and Reservation Station). Some computer-architecture people call that "dispatch", but it's probably not a good idea in an x86 context. (Unless AMD uses that terminology; I'm mostly familiar with Intel).

----

You list the uop queue size at 128 for Skylake. This is bogus. It's always 64 per thread, with or without hyperthreading. Intel has alternated in SnB/IvB/HSW/SKL between this and letting one thread use both queues as a single big queue. HSW/BDW statically partition their 56-entry queue into two 28-entry halves when two threads are active, otherwise it's a 56-entry queue. (Not 64). Agner Fog's microarch pdf and Intel's optmization manual both confirm this (in Section 2.1.1 about Skylake's front-end improvements over previous generations).

Also, the 4-uop per clock issue width is 4 fused-domain uops, so I was able to construct a loop that runs 7 unfused-domain uops per clock (http://www.agner.org/optimize/blog/read.php?i=415#... with 2 micro-fused ALU+load, one micro-fused store, and a dec/branch. AMD doesn't talk about "unfused" uops because it doesn't use a unified scheduler, IIRC, so memory source operands always stay with the ALU uop.

Also, you mentioned it in the text, but the L1d change from write-through to write-back is worth a table row. IIRC, Bulldozer's L1d write-back has a small buffer or something to absorb repeated writes of the same lines, so it's not quite as bad as a classic write-through cache would be for L2 speed/power requirements, but Ryzen is still a big improvement.