Cortex-M7 Launches: Embedded, IoT and Wearables

by Stephen Barrett on September 23, 2014 7:01 PM ESTFinal Words

In the past two days we have seen two announcements targeting IoT and wearable devices from major semiconductor companies. These announcements may seem premature as there hasn’t been a game changing device release like the original iPhone was, but the companies involved are simply doing what they have done before and investing in the future. Much of ARMs work before the ARM11 processor was behind closed doors or simply unnoticed by consumers at large, but it was there. Watching the suppliers evolve to provide suitable products, documentation, and tooling for something new is exciting.

The Coretex-M7 processor pushes the performance of ARMs dedicated MCU line to new levels, helping ARM further consolidate MCUs and DSPs into a single ARM ISA compatible 32-bit CPU. The increased performance and features also allow device makers to rely more on the always on MCU and power up the AP much less often, improving overall power consumption and even enabling devices that were previously impractical.

ARM also invested in improving the interrupt latency of the M7 and provides qualification kits for safety critical standards like ISO 26262 (automotive) and IEC61508. Anyone with experience here knows just how expensive creating these kits can be.

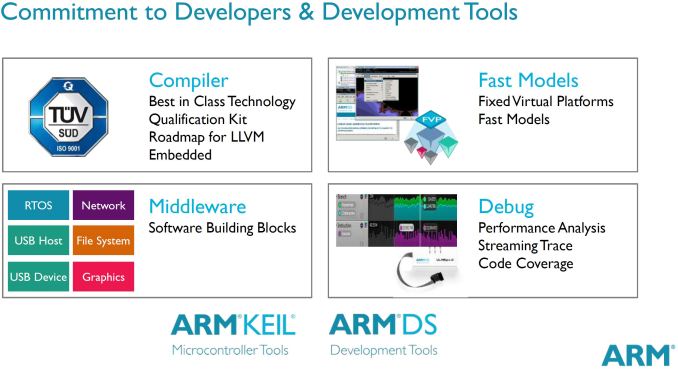

For major MCU SoC vendors like ST, Atmel, NXP, Freescale, TI, and others, the prospect of integrating a CPU core off-the-shelf from ARM means less R&D investment in processor design and documentation with a potentially greater payoff by tapping into the ARM ecosystem. Additionally, rather than hand coding their own development IDEs and compilers, they can serve their users with existing open source alternatives. To consumers, consolidation could bring similarities to the Windows + Intel days when software developers gained immense efficiency.

Many IoT and wearable devices today accomplish their roles using high power A series application processors. This is by design, as the companies providing them simply reused their smartphone processors to get product to market as fast as possible. Designing a heterogeneous system using MCUs and application processors is more complex but the benefits are undeniable. As the IoT and wearable devices mature, we will keep a close eye on the underlying technology of future devices and hope to report some positive changes over the next year.

43 Comments

View All Comments

Wilco1 - Wednesday, September 24, 2014 - link

Embedded (M) was traditionally a micro controller using on-chip flash and SRAM, no MMU, no DSP, no FP support. The R series are higher performance realtime CPUs with TCM, caches, branch prediction and often external DRAM and FP. Now that M also supports DSP, FP, caches, and is becoming high performance, things have become blurred. The ISA differences are now the main distinction, M only supports Thumb-1, Thumb-2 and uses a different interrupt model, while the R architecture is basically A series plus TCM minus MMU. So many TLA's...hammer256 - Wednesday, September 24, 2014 - link

Oh that's right, different interrupt model. M series is generally lower latency because it's directly coupled, if I recall. It's just that this new M7 line blurs that line even further than the M4 did...For TCM, is it generally DRAM integrated on the MCU, or a tight interface between the MCU and the DRAM chips?

Didn't one of samsung's SSDs use a few Cortex-R3 cores for their controller?

Wilco1 - Wednesday, September 24, 2014 - link

3 R4 cores are used in Samsung SSDs.Simply put, TCM is fast on-core instruction/data SRAM, similar to an I- or D-cache. It is fully under user control and thus without the non-deterministic effects of a traditional cache. TCM can be used in addition to a cache. TCM allows high frequencies like a cache, and thus is faster than an external SRAM.

The usage model is that you put all your critical realtime code/data in the instruction/data TCMs and run the rest from flash/DRAM. When an interrupt occurs, you start executing realtime code from the TCM immediately rather than having to wait for cache misses that inevitably occur if you didn't have TCM. So the TCMs are actually necessary for realtime on a fast CPU, having a low interrupt latency alone is not the whole story.

hammer256 - Wednesday, September 24, 2014 - link

Oooh I see. It sounds like TCM is a big distinguishing feature between the M and R series then. So even if performance is equal, R series actually allows for applications with even tighter latency requirements than the M series.Well, learned something new today, thanks!

toyotabedzrock - Wednesday, September 24, 2014 - link

It is not a good idea to put this in a wearable or a car. The lack of an MMU seems tone deaf given the security environment we live in.Wilco1 - Wednesday, September 24, 2014 - link

Most of the M series support an optional MPU for OS task protection. That said, security and MMU are 2 orthogonal things - an MMU doesn't stop exploits as otherwise we wouldn't have any viruses/trojans/rootkits/etc on PCs. For microcontrollers security is easier as there are far fewer possible security breaches, so it's more down to not setting default passwords or using old, already broken encryption algorithms.ah06 - Thursday, September 25, 2014 - link

Which one makes most sense in a wearable? M4, M7, Rx, A7, A53?Wilco1 - Thursday, September 25, 2014 - link

IMHO only M3 or M4 - anything else is way overkill for eg. a watch. You definitely don't want to run anything as big/complex as Linux/Android if you want to provide at least a week of battery life.DIYEyal - Sunday, September 28, 2014 - link

Actually the WeLoop tommy smartwatch has the M0, they claim 3 weeks of battery life with a 110mAh battery.RomanR - Thursday, September 25, 2014 - link

Hi,who can tell me: how many clock cycles will be needed for ten taps 32-bit FIR filter output sample computation ?

1 cycle MAC instruction is O.K. but what about data transfer ?