Intel Broadwell Architecture Preview: A Glimpse into Core M

by Ryan Smith on August 11, 2014 12:01 PM ESTBroadwell CPU Architecture

We’ll kick off our look at Broadwell-Y with Broadwell’s CPU architecture. As this is a preview Intel isn’t telling us a great deal about the CPU at this time, but they have given us limited information about Broadwell’s architectural changes and what to expect for performance as a result.

With Broadwell Intel is at the beginning of the next cycle of their tick-tock cadence. Whereas tock products such as Haswell and Sandy Bridge designed to be the second generation of products to use a process node and as a result are focused on architectural changes, tick products such as Ivy Bridge and now Broadwell are the first generation of products on a new process node and derive much (but not all) of their advantage from manufacturing process improvements. Over the years Intel has wavered on just what a tick should contain – it’s always more than simply porting an architecture to a new process node – but at the end of the day Broadwell is clearly derived from Haswell and will be taking limited liberties in improving CPU performance as a result.

| Intel's Tick-Tock Cadence | |||||

| Microarchitecture | Process Node | Tick or Tock | Release Year | ||

| Conroe/Merom | 65nm | Tock | 2006 | ||

| Penryn | 45nm | Tick | 2007 | ||

| Nehalem | 45nm | Tock | 2008 | ||

| Westmere | 32nm | Tick | 2010 | ||

| Sandy Bridge | 32nm | Tock | 2011 | ||

| Ivy Bridge | 22nm | Tick | 2012 | ||

| Haswell | 22nm | Tock | 2013 | ||

| Broadwell | 14nm | Tick | 2014 | ||

| Skylake | 14nm | Tock | 2015 | ||

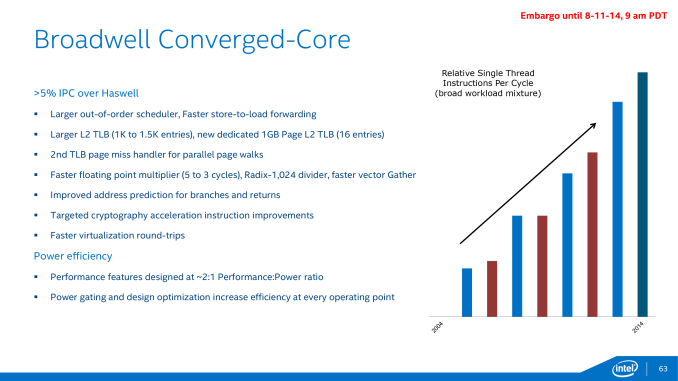

All told, Intel is shooting for a better than 5% IPC improvement over Haswell. This is similar to Ivy Bridge (4%-6%), though at this stage in the game Intel is not talking about expected clockspeeds or the resulting overall performance improvement. Intel has made it clear that they don’t regress on clockspeeds, but beyond that we’ll have to wait for further product details later this year to see how clockspeeds will compare.

To accomplish this IPC increase Intel will be relying on a number of architectural tweaks in Broadwell. Chief among these are bigger schedulers and buffers in order to better feed the CPU cores themselves. Broadwell’s out-of-order scheduling window for example is being increased to allow for more instructions to be reordered, thereby improving IPC. Meanwhile the L2 translation lookaside buffer (TLB) is being increased from 1K to 1.5K entries to reduce address translation misses.

The TLBs are also receiving some broader feature enhancements that should again improve performance. A second miss handler is being added for TLB pages, allowing Broadwell to utilize both handlers at once to walk memory pages in parallel. Otherwise the inclusion of a 1GB page mode should pay off particularly well for servers, granting Broadwell the ability to handle these very large pages on top of its existing 2MB and 4K pages.

Meanwhile, as is often the case Intel is once again iterating on their branch predictor to cut down on missed branches and unnecessary memory operations. Broadwell’s branch predictor will see its address prediction improved for both branches and returns, allowing for more accurate speculation of impending branching operations.

Of course efficiency increases can only take you so far, so along with the above changes Intel is also making some more fundamental improvements to Broadwell’s math performance. Both multiplication and division are receiving a performance boost thanks to performance improvements in their respective hardware. Floating point multiplication is seeing a sizable reduction in instruction latency from 5 cycles to 3 cycles, and meanwhile division performance is being improved by the use of an even larger Radix-1024 (10bit) divider. Even vector operations will see some improvements here, with Broadwell implementing a faster version of the vector Gather instruction.

Finally, while it’s not clear whether these will be part of AES-NI or another instruction subset entirely, Intel is once again targeting cryptography for further improvements. To that end Broadwell will bring with it improvements to multiple cryptography instructions.

Meanwhile it’s interesting to note that in keeping with Intel’s power goals for Broadwell, throughout all of this Intel put strict power efficiency requirements in place for any architecture changes. Whereas Haswell was roughly a 1:1 ratio of performance to power – a 1% increase in performance could cost no more than a 1% increase in power consumption – Broadwell’s architecture improvements were required to be at 2:1. While a 2:1 mandate is not new – Intel had one in place for Nehalem too – at the point even on the best of days meaningful IPC improvements are hard to come by at 1:1, never mind 2:1. The end result no doubt limited what performance optimizations Intel could integrate into Broadwell’s design, but it also functionally reduces power requirements for any given performance level, furthering Intel’s goals in getting Core performance in a mobile device. In the case of Broadwell this means Broadwell’s roughly 5% performance improvement comes at a cost of just a 2.5% increase in immediate power consumption.

With that said, Intel has also continued to make further power optimizations to the entire Broadwell architecture, many of which will be applicable not just to Core M but to all future Broadwell products. Broadwell will see further power gating improvements to better shut off parts of the CPU that are not in use, and more generalized design optimizations have been made to reduce power consumption of various blocks as is appropriate. These optimizations coupled with power efficiency gains from the 14nm process are a big part of the driving force in improving Intel’s power efficiency for Core M.

158 Comments

View All Comments

kyuu - Tuesday, August 12, 2014 - link

Nothing was said about cheap tablets in that quote, so I'm not sure why you're bringing up the price.Not that I disagree with your point. Of course, by continuing to focus on premium priced parts, Intel is never going to gain a profitable foothold in the mobile market. Core M needs to be cheaper, not just lower power, to be interesting. Otherwise there's no reason to care. If you're paying for a $1000 device, why do you want something that's obviously going to be so performance gimped compared to Y-series Broadwells?

Drazick - Tuesday, August 12, 2014 - link

Does "Shared Virtual Memory" means the same as AMD's shared memory configuration?No more need to replicate data for the GPU?

Laststop311 - Tuesday, August 12, 2014 - link

A surface Pro with core-M might be pretty good.Krysto - Tuesday, August 12, 2014 - link

For battery life, maybe. For performance, no.fokka - Tuesday, August 12, 2014 - link

i would like to see ordinary 13" ultrabooks with broadwell-y. don't make it too slim and see what performance and battery life is like with a 4.5w cpu. if performance is high enough for everyday tasks, it would really be nice to have slim notebooks approach 20 hours of battery life in light usage scenarios.but i guess companies will just use the low power cpus as an excuse to implement smaller batteries and 4k displays and we still won't get much more than 10h in best case scenarios...

dcaxax - Tuesday, August 12, 2014 - link

I'd argue that it may well be too late for Intel to enter this market, unless they can deliver a major step change in performance compared to ARM. Right now the ARM-Android & ARM-iOS ecosystems are well established and humming along nicely. On top of which tablet sales in the developed world are slowing down. The developing world is still growing but in those regions, cost will be a key factor.That leaves Intel targeting a market with an entrenched competitor, a set software ecosystems with no benefits from migrating to a new architecture (what do Apple, Google, Samsung, HTC, LG etc gain out of this?) and slowing hardware sales.

I Core M can deliver double performance for the same power draw AND price, then sure, I can see a rush to migrate to it, otherwise what's the point?

Krysto - Tuesday, August 12, 2014 - link

"Core" chips will never EVER compete with ARM in its main market. The best Intel can do is try to compete in $700+ devices. Core is just not competitive on price. Not even close. Period.Intel's only competition against ARM in the MOBILE market is Atom, and Nvidia's Denver is already TWICE as fast as that. Also Atom is twice as expensive as Denver, but Intel keeps subsidizing half the cost...for as long as they can, which probably won't be much longer.

tuxRoller - Wednesday, August 13, 2014 - link

Link to the denver benchmarks?Natfly - Tuesday, August 12, 2014 - link

This article feels like marketing drivel just listing point after point without any further explanation. I'd expect a little more in-depth analysis. Seriously a tick/tock chart?KhalidShaikh - Tuesday, August 12, 2014 - link

Great write up.