The Intel Xeon E7 v2 Review: Quad Socket, Up to 60 Cores/120 Threads

by Johan De Gelas on February 21, 2014 6:00 AM EST- Posted in

- IT Computing

- Intel

- Xeon

- Ivy Bridge EX

- server

- Brickland

Bandwidth Monster

Previous versions of Intel's flagship Xeon always came with very conservative memory configurations as RAM capacity and reliability was the priority. Typically, these systems came with memory extension buffers for increased capacity, but those memory buffers also increase memory latency. As a result, these quad- and octal-socket monsters had a hard time competing with the best dual-Xeon setups in memory intensive applications.

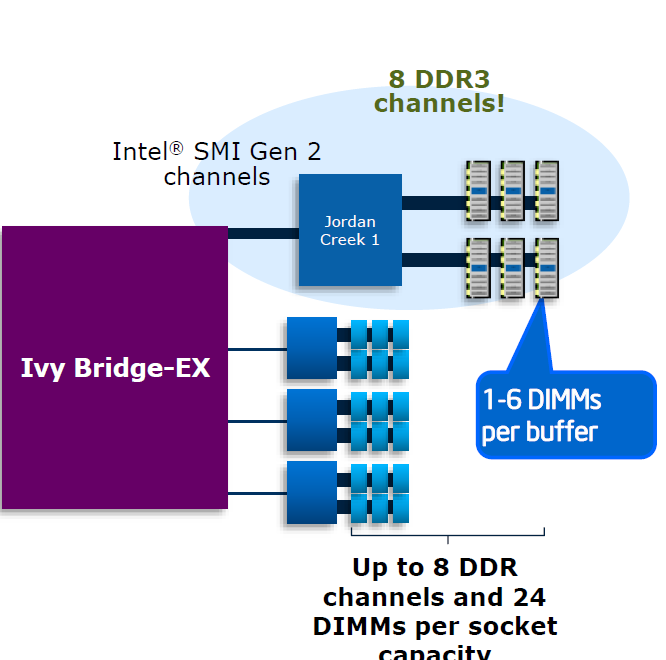

The new Xeon E7 v2 still has plenty of memory buffers (code named "Jordan Creek"), and it now supports three instead of two DIMMs per channel. The memory riser cards with two buffers now support 12 instead of eight DIMMs (Xeon Westmere-EX). Using relatively affordable 32GB DIMMs, this allows you to load a system machine up to 3TB RAM. If you break the bank and use 64GB LRDIMMs, 6TB RAM is possible.

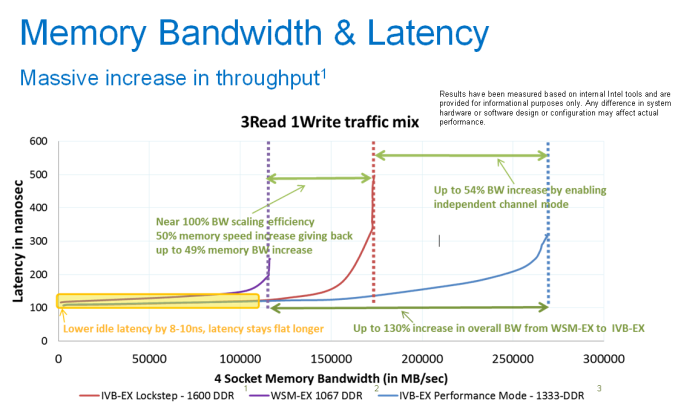

With the previous platform, having eight memory channels only increased capacity and not bandwidth as they ran in lockstep. Each channel delivers half a cache line, then the Jordan Creek buffer combines those halves and sends off the result to the requesting memory controller. The high speed serial interface or scalable memory interconnect (SMI) channels must run at the same speed as the DDR3 channels. With Westmere-EX, this resulted in an SMI running at a maximum of 1066MHz. With the Xeon E7 v2, we get four SMI interconnects running at speeds up to 1600MHz. In lockstep, the system can survive a dual-device error. As result, the RAS (Reliability, Accessibility, Serviceability) is best in Lockstep.

With the Ivy Bridge EX version of the Xeon E7, the channels can also run independently. This mode is called performance mode and each channel can deliver one cache line. To cope with twice the amount of bandwidth, the SMI interconnect must run twice as fast as the memory channels. In this case, the SMI channel can run at 2667 MT/s while the two channels work at 1333 MT/s. That means in theory, the E7 v2 chip could deliver as much as 85GB/s (1333 * 8 channels * 8 bytes per channel) of bandwidth, which is 2.5x more than what the previous platform delivered. The disadvantage is that only a single device error can be corrected—more speed, less RAS.

According to Intel, both latency and bandwidth are improved tremendously compared to the Westmere-EX platform. As a result, the new quad Xeon E7 v2 platform should perform a lot better in memory intensive HPC applications.

125 Comments

View All Comments

JohanAnandtech - Saturday, February 22, 2014 - link

I meant, I have never seen an independent review of high-end IBM or SUN systems. We did one back in the T1 days, but the product performed only well in a very small niche.Phil_Oracle - Monday, February 24, 2014 - link

Contact your Oracle rep and I am sure we'd be glad to loan you a SPARC T5 server, which we have in our loaner pool for analysts and press. Would be nice if you had a more objective view on comparisons.Phil_Oracle - Monday, February 24, 2014 - link

If you look at Oracles Performance/Benchmark blog, we have comparisons between Xeon, Power and SPARC based on all publicly available benchmarks. As Oracle sells both x86 as well as SPARC, we sometimes have benchmarks available on both platforms to compare.https://blogs.oracle.com/BestPerf/

Will Robinson - Saturday, February 22, 2014 - link

Intel and their CPU technology continues to impress.Those kind of performance increase numbers must leave their competitors gasping on the mat.

Props for the smart new chip. +1

Nogoodnms - Saturday, February 22, 2014 - link

But can it run Crysis?errorr - Saturday, February 22, 2014 - link

My wife would now the answer to this considering she works for ibm but considering software costs far exceed hardware costs on a life cycle basis does anyone know what the licensing costs are between the different platforms.She once had me sit down to explain to her how CPU upgrades would effect db2 licenses. The system is more arcane and I'm not sure what the cost of each core is.

For an ERP each chip type has a rated pvu metric from IBM which determines the cost of the license. Are RISC cores priced differently than x86 cores enough to partially make up the hardware costs?

JohanAnandtech - Sunday, February 23, 2014 - link

I know Oracle does that (risc core <> x86 core when it comes to licensing), but I must admit, Licensing is extremely boring for a technical motivated person :-).Phil_Oracle - Monday, February 24, 2014 - link

In total cost of ownership calculations, where both HW and SW as well as maintenance costs are calculated, the majority of the costs (upwards of 90%) are associated with software licensing and maintenance/administration- so although HW costs matter, it’s the performance of the HW that drives the TCO. For Oracle, both Xeon and SPARC have a per core license factor of .5x, meaning 1 x license for every two cores, while Itanium and Power have a 1x multiplier, so therefore Itanium/Power must have a 2x performance/core advantage to have equivalent SW licensing costs. IBM has a PVU scale for SW licensing, which essentially is similar to Oracle but more granular in details. Microsofts latest SQL licensing follows similarly. So clearly, performance/CPU and especially per core matters in driving down licensing costs.Michael REMY - Sunday, February 23, 2014 - link

that would have be very good to test this cpu on 3D rendering benchmark.i can imagine the gain of time in a workstation...even the cost will be nearest a renderfarm...

but comparing this xeon to other one in that situation should have bring a view point.

JohanAnandtech - Sunday, February 23, 2014 - link

What rendering engine are you thinking about? Most engines scale badly beyond 16-32 threads