Intel's Haswell Architecture Analyzed: Building a New PC and a New Intel

by Anand Lal Shimpi on October 5, 2012 2:45 AM ESTPrioritizing ILP

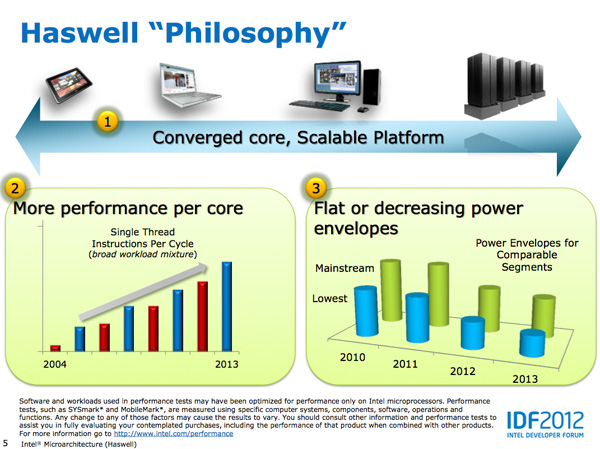

Intel has held the single threaded performance crown for years now, but the why is really quite easy to understand: it has prioritized extracting instruction level parallelism with every generation. Couple that with the fact that every two years we see a "new" microprocessor architecture from Intel and there's a recipe for some good old evolutionary gains. The table below shows the increase in size of some major data structures inside Intel's architectures for every tock since Conroe:

| Intel Core Architecture Buffer Sizes | ||||||

| Conroe | Nehalem | Sandy Bridge | Haswell | |||

| Out-of-order Window | 96 | 128 | 168 | 192 | ||

| In-flight Loads | 32 | 48 | 64 | 72 | ||

| In-flight Stores | 20 | 32 | 36 | 42 | ||

| Scheduler Entries | 32 | 36 | 54 | 60 | ||

| Integer Register File | N/A | N/A | 160 | 168 | ||

| FP Register File | N/A | N/A | 144 | 168 | ||

| Allocation Queue | ? | 28/thread | 28/thread | 56 | ||

Increasing the OoO window allows the execution units to extract more parallelism and thus improve single threaded performance. Each generation Intel is simply dedicating additional transistors to increasing these structures and thus better feeding the beast.

This isn't rocket science, but it is enabled by Intel's clockwork fab execution. Designers can count on another 30% die area to work with every 2 years, so every 2 years they increase the size of these structures without worrying about ballooning the die. The beauty of evolutionary improvements like this is that when viewed over the long term they look downright revolutionary. Comparing Haswell to Conroe, the OoO scheduling window has grown by a factor of 2x, despite generation to generation gains of only 14 - 33%.

245 Comments

View All Comments

defiler99 - Tuesday, October 16, 2012 - link

One of the best articles on Anandtech in some time. This is great original tech industry reporting.Gc - Saturday, January 12, 2013 - link

Congratulations, an intel cpu engineer wrote around 27 Dec 2012:"... Anandtech's latest Haswell preview is also excellent; missing some key puzzle pieces to complete the picture and answer some open questions or correct some details but otherwise great. ..."

http://www.reddit.com/r/IAmA/comments/15iaet/iama_...

xaml - Thursday, May 23, 2013 - link

This was first posted here a few handfuls of pages back as a comment by user "telephone". ^^yhselp - Friday, March 29, 2013 - link

A few questions.Is there going to be a replacement (37W) for the current IVB 35W quad-core part? Quite a few designs are now dependable on this, lower power quad-core option - Sony S-series and Razer Blade, to name a few.

When can we expect all mobile CPUs (except maybe for the extreme series) to fall into the 10W-20W range? In three years' time and 10nm?

The decision to not include GT3 with desktop parts is very disappointing. A 35/45W low-voltage part with GT3 would make for an excellent HTPC build, among other things. Is there a chance Intel change their mind and start shipping GT3 desktop parts at some point?

JVimes - Tuesday, August 19, 2014 - link

Does EU stand for Execution Unit? That was surprisingly hard to google for.