The AMD Trinity Review (A10-4600M): A New Hope

by Jarred Walton on May 15, 2012 12:00 AM ESTImproved Turbo

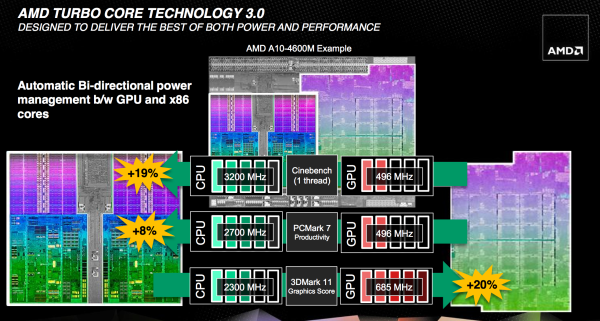

Trinity features a much improved version of AMD's Turbo Core technology compared to Llano. First and foremost, both CPU and GPU turbo are now supported. In Llano only the CPU cores could turbo up if there was additional TDP headroom available, while the GPU cores ran no higher than their max specified frequency. In Trinity, if the CPU cores aren't using all of their allocated TDP but the GPU is under heavy load, it can exceed its typical max frequency to capitalize on the available TDP. The same obviously works in reverse.

Under the hood, the microcontroller that monitors all power consumption within the APU is much more capable. In Llano, the Turbo Core microcontroller looked at activity on the CPU/GPU and performed a static allocation of power based on this data. In Trinity, AMD implemented a physics based thermal calculation model using fast transforms. The model takes power and translates it into a dynamic temperature calculation. Power is still estimated based on workload, which AMD claims has less than a 1% error rate, but the new model gets accurate temperatures from those estimations. The thermal model delivers accuracy at or below 2C, in real time. Having more accurate thermal data allows the turbo microcontroller to respond quicker, which should allow for frequencies to scale up and down more effectively.

At the end of the day this should improve performance, although it's difficult to compare directly to Llano since so much has changed between the two APUs. Just as with Llano, AMD specifies nominal and max turbo frequencies for the Trinity CPU/GPU.

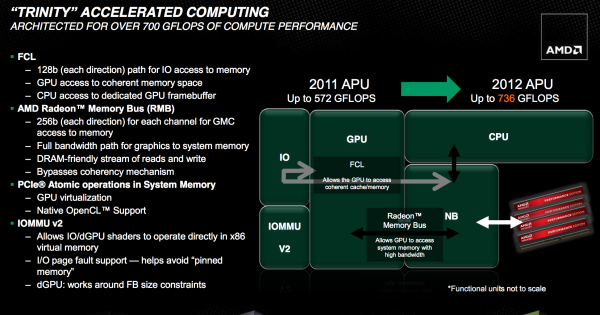

A Beefy Set of Interconnects

The holy grail for AMD (and Intel for that matter) is a single piece of silicon with CPU and GPU style cores that coexist harmoniously, each doing what they do best. We're not quite there yet, but in pursuit of that goal it's important to have tons of bandwidth available on chip.

Trinity still features two 64-bit DDR3 memory controllers with support for up to DDR3-1866 speeds. The controllers add support for 1.25V memory. Notebook bound Trinities (Socket FS1r2 and Socket FP2) support up to 32GB of memory, while the desktop variants (Socket FM2) can handle up to 64GB.

Hyper Transport is gone as an external interconnect, leaving only PCIe for off-chip IO. The Fusion Control Link is a 128-bit (each direction) interface giving off-chip IO devices access to system memory. Trinity also features a 256-bit (in each direction, per memory channel) Radeon Memory Bus (RMB) direct access to the DRAM controllers. The excessive width of this bus likely implies that it's also used for CPU/GPU communication as well.

IOMMU v2 is also supported by Trinity, giving supported discrete GPUs (e.g. Tahiti) access to the CPU's virtual memory. In Llano, you used to take data from disk, copy it to memory, then copy it from the CPU's address space to pinned memory that's accessible by the GPU, then the GPU gets it and brings it into its frame buffer. By having access to the CPU's virtual address space now the data goes from disk, to memory, then directly to the GPU's memory—you skip that intermediate mem to mem copy. Eventually we'll get to the point where there's truly one unified address space, but steps like these are what will get us there.

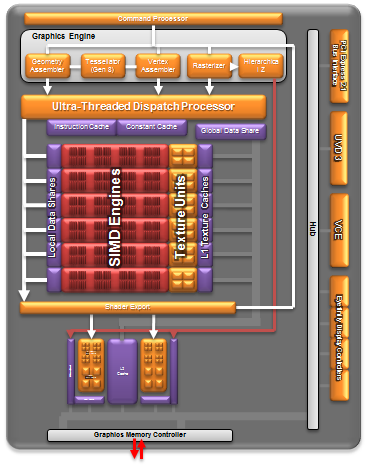

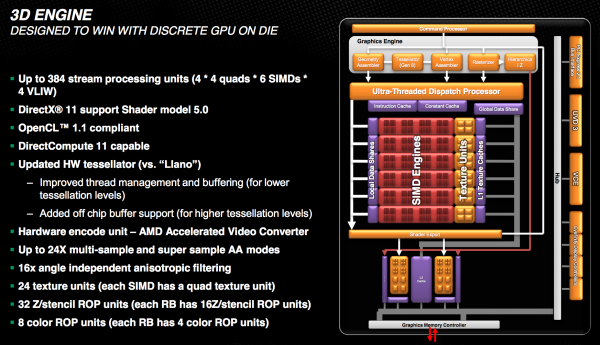

The Trinity GPU

Trinity's GPU is probably the most well understood part of the chip, seeing as how its basically a cut down Cayman from AMD's Northern Islands family. The VLIW4 design features 6 SIMD engines, each with 16 VLIW4 arrays, for a total of up to 384 cores. The A10 SKUs get 384 cores while the lower end A8 and A6 parts get 256 and 192, respectively. FP64 is supported but at 1/16 the FP32 rate.

As AMD never released any low-end Northern Islands VLIW4 parts, Trinity's GPU is a bit unique. It technically has fewer cores than Llano's GPU, but as we saw with AMD's transition from VLIW5 to VLIW4, the loss didn't really impact performance but rather drove up efficiency. Remember that most of the time that 5th unit in AMD's VLIW5 architectures went unused.

The design features 24 texture units and 8 ROPs, in line with what you'd expect from what's effectively 1/4 of a Cayman/Radeon HD 6970. Clock speeds are obviously lower than a full blown Cayman, but not by a ton. Trinity's GPU runs at a normal maximum of 497MHz and can turbo up as high as 686MHz.

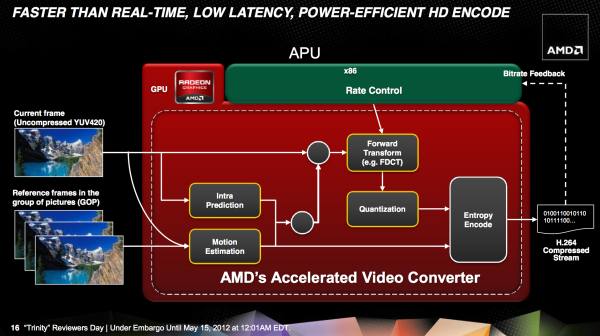

Trinity includes AMD's HD Media Accelerator, which includes accelerated video decode (UVD3) and encode components (VCE). Trinity borrows Graphics Core Next's Video Codec Engine (VCE) and is actually functional in the hardware/software we have here today. Don't get too excited though; the VCE enabled software we have today won't take advantage of the identical hardware in discrete GCN GPUs. AMD tells us this is purely a matter of having the resources to prioritize Trinity first, and that discrete GPU VCE support is coming.

271 Comments

View All Comments

deathpony - Tuesday, May 15, 2012 - link

Also the Gpu overclock wasn't limited by the chip itself but by a bios limitation, by staying at stock voltage i could have reached 2.5 Ghz realistically. But with such high clocks i think the Gpu was starved by the main memory bandwidth.Rookierookie - Tuesday, May 15, 2012 - link

Let's not forget though, A New Hope came BEFORE The Empire Strikes Back...JarredWalton - Tuesday, May 15, 2012 - link

But it also came after the Phantom Menace, Attack of the Clones, and Revenge of the Sith. *Shudder* Thanks for making me remember baby Anakin and Jar Jar, you cruel, cruel person.... ;-)wintermute000 - Tuesday, May 15, 2012 - link

looks like a nice well rounded product for the budget to mid range.the CPU is fine for 'normal' workloads, and the IGP can handle AAA titles @ medium detail 720p.

Agreed the devil is in the pricing, it needs to be substantially cheaper than i5+optimus otherwise theres no point.

phatboye - Tuesday, May 15, 2012 - link

When referring to AMD Bulldozer based architectures please use the term "module" instead of "core" as it gets confusing as to which one you are talking about.JarredWalton - Tuesday, May 15, 2012 - link

If you know enough to post this comment, you should also know enough to understand from context whether we're talking about a Piledriver core (e.g. the INT core) or a Piledriver module (e.g. two INT cores and the shared FP). And trust me, it's just as confusing trying to write about Bulldozer architectures as it is to read about them. But if there's a specific place in the article where we say "core" when we should say "module", let me know where and I'll be happy to correct it.phatboye - Tuesday, May 15, 2012 - link

Actually I was confused at first. On the first page you stated that the A10 chip was a 4 core chip. Before reading this article I was under the impression that the first trinity chips would have 8 cores (4 modules). It took a bit of reading before I realized that what you said was actually correct in that in that it is a 4 core (2 module) CPU.Yes the misunderstanding was totally my fault but it would make things a lot easier if you made a convention when referring to AMD bulldozer "cores" in terms of modules instead.

Cow86 - Tuesday, May 15, 2012 - link

You seem to have forgotten to mention the 'resonant clock mesh' technology that AMD recently acquired, and uses in Piledriver (and therefore Trinity)...said to account for a ~10% saving in power consumption at the same clockspeed alone already.Anyway, I'm rather pleased to see this part arrive :) Seems to put AMD in a much better position in the mobile space again, and I'd be very interested to see how they can compete with ultrabooks this time around with their 17W chips. Now to wait how they measure up on the desktop as well...And of course the new FX CPU's later this year...bodes well for those too, looking at the reduced power consumption, as their high power draw is the biggest problem right now.

mikato - Wednesday, May 16, 2012 - link

Yeah nice catch. I forgot that was going in Trinity.ltcommanderdata - Tuesday, May 15, 2012 - link

In one of the AMD slides on the first page, it mentions Trinity supports AVX1.1. I haven't heard of that standard before, only AVX and AVX2. What does AVX1.1 add over AVX and is AMD the only one to implement it right now?I also saw you tried WinZip 16.5 OpenCL and Ivy Bridge OpenCL which I commented on before. Thanks for that. Too bad the results didn't turn out that exciting.