The Apple iPad Review (2012)

by Vivek Gowri & Anand Lal Shimpi on March 28, 2012 3:14 PM ESTA Word on Packaging

Unlike the first two iPads, the 3rd generation iPad abandons the high density flip-chip PoP SoC/DRAM stack and uses a discrete, flip-chip BGA package for the SoC and two discrete BGA packages for the DRAMs.

If you think of SoC silicon as a stack, the lowest layer is where you'll find the actual transistor logic, while the layers of metal above it connect everything together. In the old days, the silicon stack would sit just as I've described it—logic at the bottom, metal layers on top. Pads around the perimeter of the top of the silicon would connect to very thin wires, that would then route to the package substrate and eventually out to balls or pins on the underside of the package. These wire bonded packages, as they were called, had lower limits of how many pins you could have connecting to your chip.

There are also cooling concerns. In a traditional wire bonded package, your cooling solution ultimately rests on a piece of your packaging substrate. The actual silicon itself isn't exposed.

As its name implies, a flip-chip package is literally the inverse of this. Instead of the metal layers being at the top of the stack, before packaging the silicon is inverted and the metal layers are at the bottom of the stack. Solder bumps at the top of the silicon stack (now flipped and at the bottom) connect the topmost metal layer to the package itself. Since we're dealing with solder bumps on the silicon itself rather than wires routed to the edge of the silicon, there's much more surface area for signals to get in/out of the silicon.

Since the chip is flipped, the active logic is now exposed in a flip-chip package and the hottest part of the silicon can be directly attached to a cooling solution.

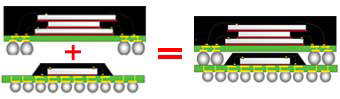

An example of a PoP stack

To save on PCB real estate however, many SoC vendors would take a flip-chip SoC and stack DRAM on top of it in a package-on-package (PoP) configuration. Ultimately this re-introduces many of the problems from older packaging techniques—mainly it becomes difficult to have super wide memory interfaces as your ball-out for the PoP stack is limited to the area around your die, and cooling is a concern once more. For low power, low bandwidth mobile SoCs this hasn't really been a problem, which is why we see PoP stacks deployed all over the place.

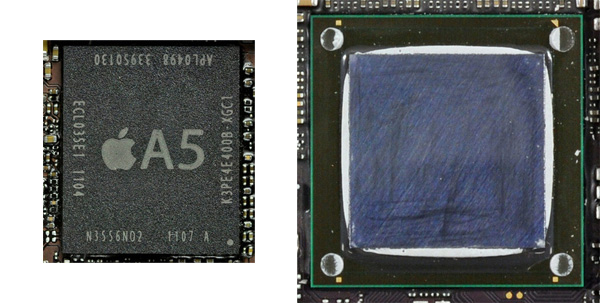

Take a look at the A5, a traditional FC-BGA SoC with PoP DRAM vs. the A5X (this isn't to scale):

Images courtesy iFixit

The A5X in this case is a FC-BGA SoC but without any DRAM stacked on top of it. The A5X is instead covered in a thermally conductive paste and then with a metallic heatspreader to conduct heat away from the SoC and protect the silicon.

Given the size and complexity of the A5X SoC, it's no surprise that Apple didn't want to insulate the silicon with a stack of DRAM on top of it. In typical package-on-package stacks, you'd see solder bumps around the silicon, on the package itself, that a separate DRAM package would adhere to. Instead of building up a PoP stack here, Apple simply located its two 64-bit DRAM devices on the opposite side of the iPad's logic board and routed the four 32-bit LP-DDR2 memory channels through the PCB layers.

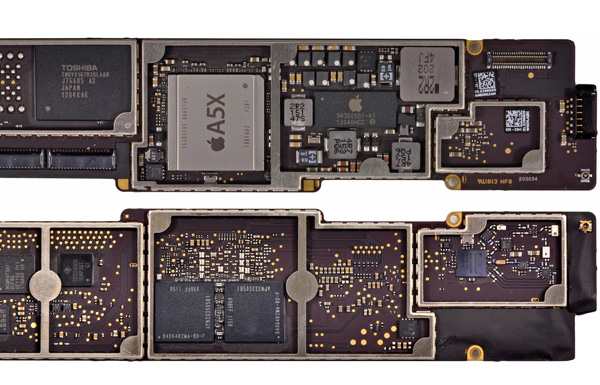

iPad (3rd gen) logic board back (top) and front (bottom), courtesy iFixit

If I'm seeing this correctly, it looks like the DRAM devices are shifted lower than the center point of the A5X. Routing high speed parallel interfaces isn't easy and getting the DRAM as close to the memory controller as possible makes a lot of sense. For years motherboard manufacturers and chipset vendors alike complained about the difficulties of routing a high-speed, 128-bit parallel DRAM interface on a (huge, by comparison) ATX motherboard. What Apple and its partners have achieved here is impressive when you consider that this type of interface only made it to PCs within the past decade.

Looking Forward: 12.8GB/s, the Magical Number

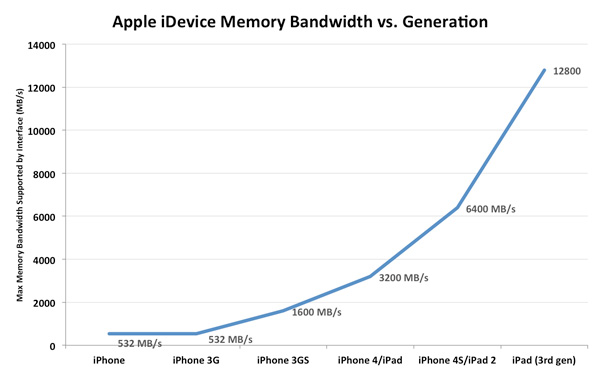

The DRAM speeds in the new iPad haven't changed. The -8D in the Elpida DRAM string tells us this memory is rated at the same 800MHz datarate as what's used in the iPhone 4S and iPad 2. With twice the number of channels to transfer data over however, the total available bandwidth (at least to the GPU) doubles. I brought back the graph I made for our iPhone 4S review to show just how things have improved:

The A5X's memory interface is capable of sending/receiving data at up to 12.8GB/s. While this is still no where near the 100GB/s+ we need for desktop quality graphics at Retina Display resolutions, it's absolutely insane for a mobile SoC. Bandwidth utilization is another story entirely—we have no idea how good Apple's memory controller is (it is designed in-house), but there's 4x the theoretical bandwidth available to the A5X as there is to NVIDIA's Tegra 3.

There's a ton of memory bandwidth here, but Apple got to this point by building a huge, very power hungry SoC. Too power hungry for use in a smartphone. As I mentioned at the start of this article, the SoC alone in the new iPad can consume more power than the entire iPhone 4S (e.g. A5X running Infinity Blade 2 vs. iPhone 4S loading a web page):

| Power Consumption Comparison | ||||

| Apple A5X (SoC + mem interface) | Apple iPhone 4S (entire device) | |||

| Estimated Power Consumption | 2.6W—Infinity Blade 2 | 1.6W—Web Page Loading | ||

There's no question that we need this much (and more) memory bandwidth, but the A5X's route to delivering it is too costly from a standpoint of power. There is a solution to this problem however: Wide IO DRAM.

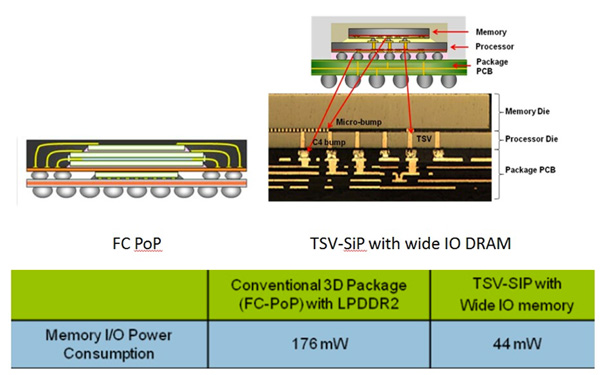

Instead of using wires to connect DRAM to solder balls on a package that's then stacked on top of your SoC package, Wide IO DRAM uses through-silicon-vias (TSVs) to connect a DRAM die directly to the SoC die. It's an even more costly packaging technique, but the benefits are huge.

Just as we saw in our discussion of flip-chip vs. wire bonded packages, conventional PoP solutions have limits to how many IO pins you can have in the stack. If you can use the entire silicon surface for direct IO however, you can build some very wide interfaces. It also turns out that these through silicon interfaces are extremely power efficient.

The first Wide IO DRAM spec calls for a 512-bit, 200MHz SDR (single data rate) interface delivering an aggregate of 12.8GB/s of bandwidth. The bandwidth comes at much lower power consumption, while delivering all of the integration benefits of a traditional PoP stack. There are still cooling concerns, but for lower wattage chips they are less worrisome.

Intel originally predicted that by 2015 we'd see 3D die stacking using through-silicon-vias. Qualcomm's roadmaps project usage of TSVs by 2015 as well. The iPhone won't need this much bandwidth in its next generation thanks to a lower resolution display, but when the time comes, there will be a much lower power solution available thanks to Wide IO DRAM.

Oh and 2015 appears to be a very conservative estimate. I'm expecting to see the first Wide IO memory controllers implemented long before then...

234 Comments

View All Comments

name99 - Friday, March 30, 2012 - link

Compared to the iPad1, the screen is, IMHO slightly smoother and a lot more oleophobic (ie it's a lot easier to clean off fingerprints by wiping a cloth over it). I never had an iPad2 so I don't know if these improvements are new or came with iPad2.shompa - Friday, March 30, 2012 - link

See = AppleTVTouch = Ipad.

But there was rumors about touch feedback from the screen. Probably in the next Ipad.

rakez - Friday, March 30, 2012 - link

as long as they stick with 4:3 i will never buy it.darkcrayon - Friday, March 30, 2012 - link

Similarly, that's one of the best things about the iPad. I can't see using a widescreen tablet in portrait mode, there is pretty much no popular content that works well there. On the other hand, 4:3 isn't as good for video, but the net effect is that the video is just smaller. I'll take properly positioned and scaled documents and smaller video over larger video and tiny documents.shompa - Friday, March 30, 2012 - link

You know that 16:9 is interesting if movies is the only thing you want to do.If you want to work on a tablet 16:9 does not work. You cant use landscape mode and see enough of the screen when you type. The 4:3 sceen is a bold move against tech nerds. I bet you are one of the tech nerds that screems when there are black bars on the side on you 16:9 TV. "why aren't the TV shows using the whole screen".

Then stupid TV people listen to you and crop 4:3 TV shows to fit 16:9 and cutting of large part of the picture.

The whole 16:9 debacle is actually a step backwards for the computing industry. Apple introduced widescreen displays early 2000. Steve made a great choose in 16:10. 2004 Apple invented the 2560x1600 screen. 16:10. Today its almost impossible to get a 16:10 screen. We all use TV LCDs for our computers = 16:9. 2560x1440. You loose 10% of real estate.

KoolAidMan1 - Saturday, March 31, 2012 - link

4:3 is better for web browsing and applications on a screen that size, the vertical room in landscape is great. It also makes for a much better balanced feel when holding it in portrait mode.Do you also like 16:9 on a desktop monitor? I sure don't, not unless it 27" 2560x1440

rakez - Saturday, March 31, 2012 - link

it's hard to argue with isheep and their products designed by god. i am pretty sure i know what i like more than someone else would know what i like. that being said, once again i prefer to not have 4:3 on my tablet. to each his own,Formul - Saturday, March 31, 2012 - link

starting with isheep and ending with "to each his own" ... you do love your bipolarity, don't you?rakez - Saturday, March 31, 2012 - link

sounds like i hit a nerve. go ahead keep following the herd. in the meantime i will buy what i want.PeteH - Monday, April 2, 2012 - link

Out of curiosity, what do you dislike about the 4:3 aspect ratio, and what's your preferred aspect ratio?